ADF4350模块设计笔记

换到KiCad6.0后画的第一块板子,为白菜价的ADF4350做一个小模块,主要还是作验证之用,方便之后开发体积更小、功能更专一的模组(比如专门输出2.2-4.4GHz的纯正弦波)。

新Ki的改动不小,感觉整个操作逻辑在向鼠标偏移,而且少了我前最喜欢的C热键,还是有些不快的。不过弧形线和从选择的轮廓生成区域的功能非常方便,插件管理也更优秀了。

0.资料汇总

ADF4350与ADF4351相差不大,所以设计时参考了二者的相关资料。此外,ADF4350的数据手册似乎有些小错,于是又去查阅的ADF4351数据手册相同部分的内容。

- ADF4350锁相环数据手册:https://www.analog.com/media/en/technical-documentation/data-sheets/ADF4350.pdf

- EVAL-ADF4350EB2Z评估板手册:https://www.analog.com/media/en/technical-documentation/user-guides/UG-110.pdf

- ADF4351锁相环数据手册:https://www.analog.com/media/en/technical-documentation/data-sheets/ADF4351.pdf

- EVAL-ADF4350EB2Z评估板手册:https://www.analog.com/media/cn/technical-documentation/user-guides/UG-435.pdf

- ADP3334低压差稳压器数据手册:https://www.analog.com/media/en/technical-documentation/data-sheets/ADP3334.pdf

- HMC284射频单刀双掷开关数据手册:https://www.analog.com/media/en/technical-documentation/data-sheets/hmc284a.pdf

1.设计要点

1.1.杂七杂八

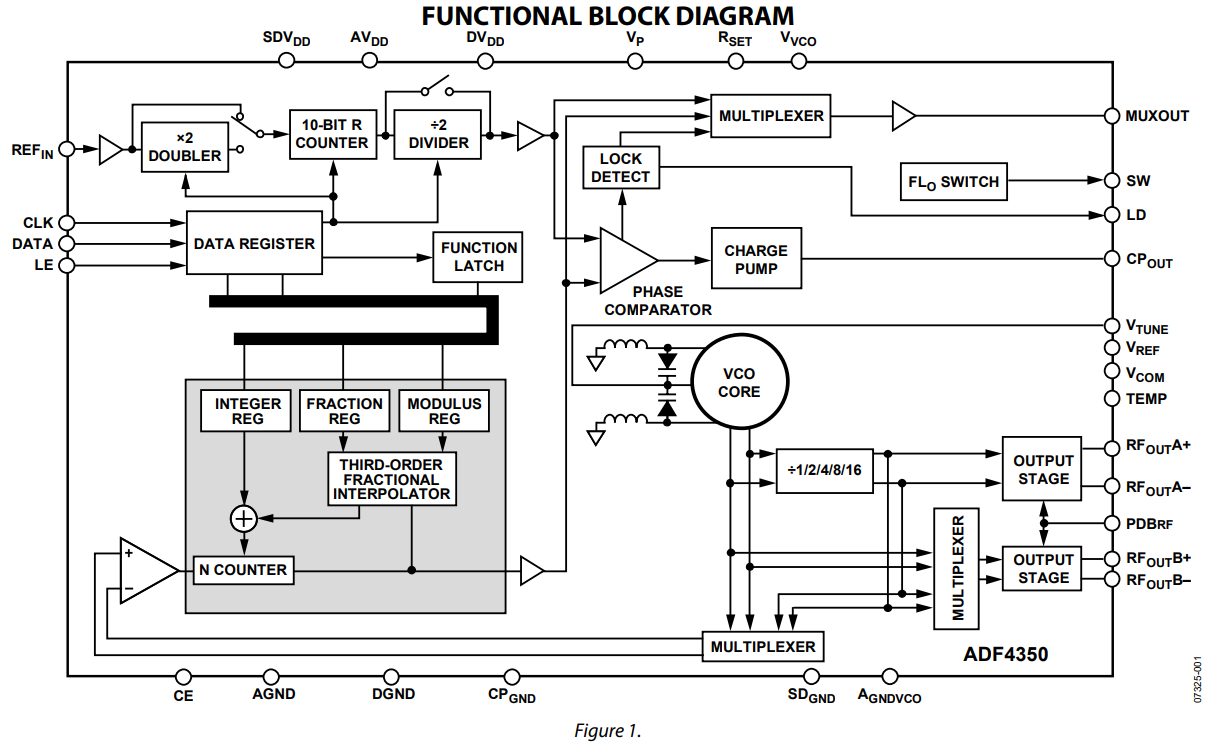

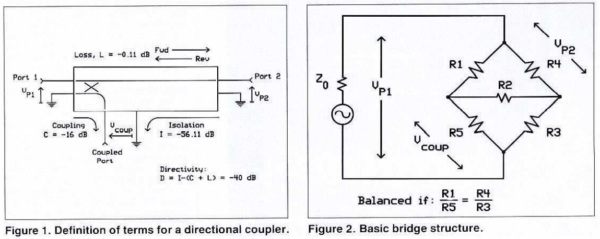

- ADF4350的框图,没啥用,暂且放在这里。

- 极限参数中,供点耐受范围基本是-0.3V至+3.9V,看来不需要提供5V级别的供电。

- 电流需求方面,数字与模拟部分合21mA,输出级6至24mA,VCO 70mA,低功耗模式下全片7至1000uA。VCO部分的电流需求还是较大的,在使用HMC860、HMC1060这种多路LDO的时候需要注意合理分配。

- 参考时钟输入允许小于10MHz的信号,但要保证压摆率大于21V/us,在使用某些正弦输出的振荡器时要注意处理。

1.2.输出级设计

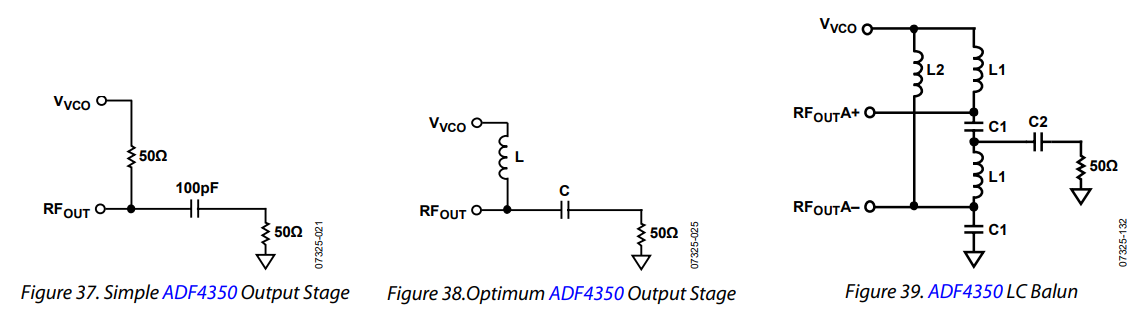

ADF4350的输出级类似集电极开路的长尾差分对,需要接入输出负载才可工作。根据使用场景,可分为有耗宽带输出匹配和窄带无耗输出匹配。同时,若有单端的输出需求,还可选择使用宽带巴伦或是窄带巴伦。

这些选择决定了正常输出的频率范围以及输出功率,在将ADF4350作为本振等用途时,这些参数至关重要,需要仔细考量。下面这部分是对ADF4350手册中27页往后OUTPUT MATCHING部分给出的接法:

使用电阻匹配为宽带匹配;使用电感作为负载,为窄带匹配,但此时输出功率得以增强,可达到5dBm。电感匹配差分输出的元件参数选择如下:

| Frequency Range (MHz) | L (nH) | C (nF) |

|---|---|---|

| 137.5 to 500 | 100 | 1 |

| 500 to 1000 | 47 | 1 |

| 1000 to 2000 | 7.5 | 1 |

| 2000 to 4400 | 3.9 | 1 |

如果需要单端输出,可直接将差分输出的一个端口接匹配负载,使用另一个端口。这样相当于浪费了一个端口的功率。如果使用巴伦转换,则理想情况可以将两个端口的功率合路输出。ADF4350的手册中给出了一个使用无耗元件搭建窄带巴伦的示意,如上图的Figure 39。所需元件参数选择如下:

| Frequency Range (MHz) | Inductor L1 (nH) | Capacitor C1 (pF) | RF Choke Inductor (nH) | DC Blocking Capacitor (pF) | Measured Output Power (dBm) |

|---|---|---|---|---|---|

| 137 to 300 | 100 | 10 | 390 | 1000 | 9 |

| 300 to 460 | 51 | 5.6 | 180 | 120 | 10 |

| 400 to 600 | 30 | 5.6 | 120 | 120 | 10 |

| 600 to 900 | 18 | 4 | 68 | 120 | 10 |

| 860 to 1240 | 12 | 2.2 | 39 | 10 | 9 |

| 1200 to 1600 | 5.6 | 1.2 | 15 | 10 | 9 |

| 1600 to 3600 | 3.3 | 0.7 | 10 | 10 | 8 |

| 2800 to 3800 | 2.2 | 0.5 | 10 | 10 | 8 |

从输出功率的数据看,巴伦起到了输出合路的功能,例如将两个无耗输出匹配时单端口输出的最大功率5dBm合路为10dBm。这种分立式巴伦应该是通过将两个输出端口的信号移相再合成实现的,工作带宽较窄。

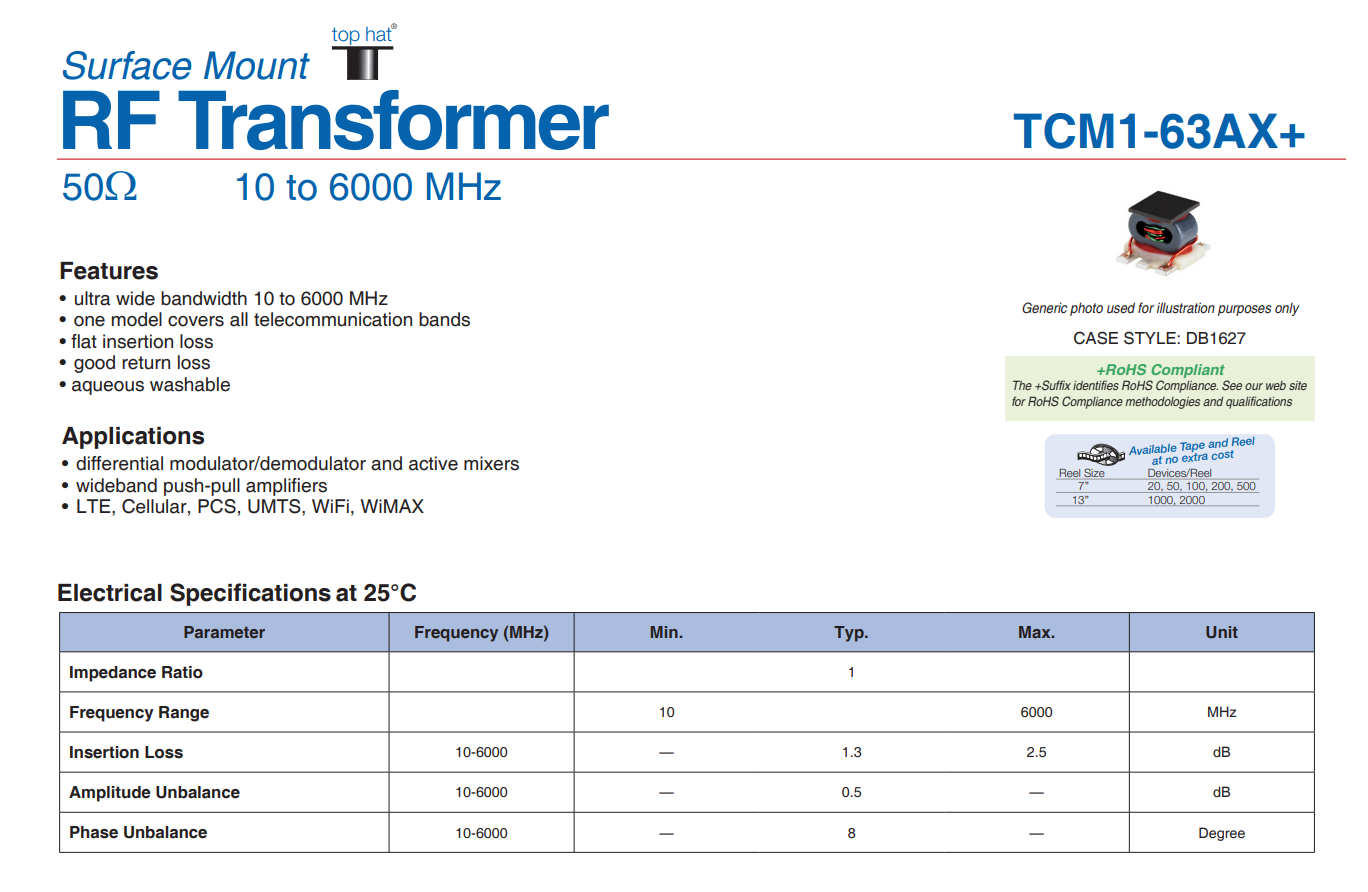

如果使用变压器巴伦,则带宽可以大大拓宽,例如著名的TCM1-63AX+:

作为测试的第一版,我决定依然采用无耗匹配,差分输出,之后在外部测试一下使用变压器巴伦的效果。此外,变压器巴伦有电流型、电压型之分,有直流接法和隔直接法之分,有待研究,先将部分资料记录在此:

- Current vs. Voltage Baluns: https://www.markimicrowave.com/blog/current-vs-voltage-baluns

- Baluns: What They Do And How They Do lt: https://www.eznec.com/Amateur/Articles/Baluns.pdf

- RF Transformer TCM1-63AX+: https://www.minicircuits.com/pdfs/TCM1-63AX+.pdf

- RF 1:1 Transmission Line ETC1-1-13: https://cdn.macom.com/datasheets/ETC1-1-13.pdf

对于备用输出端口B,不使用的时候可空置。最终输出级的设计如下图:

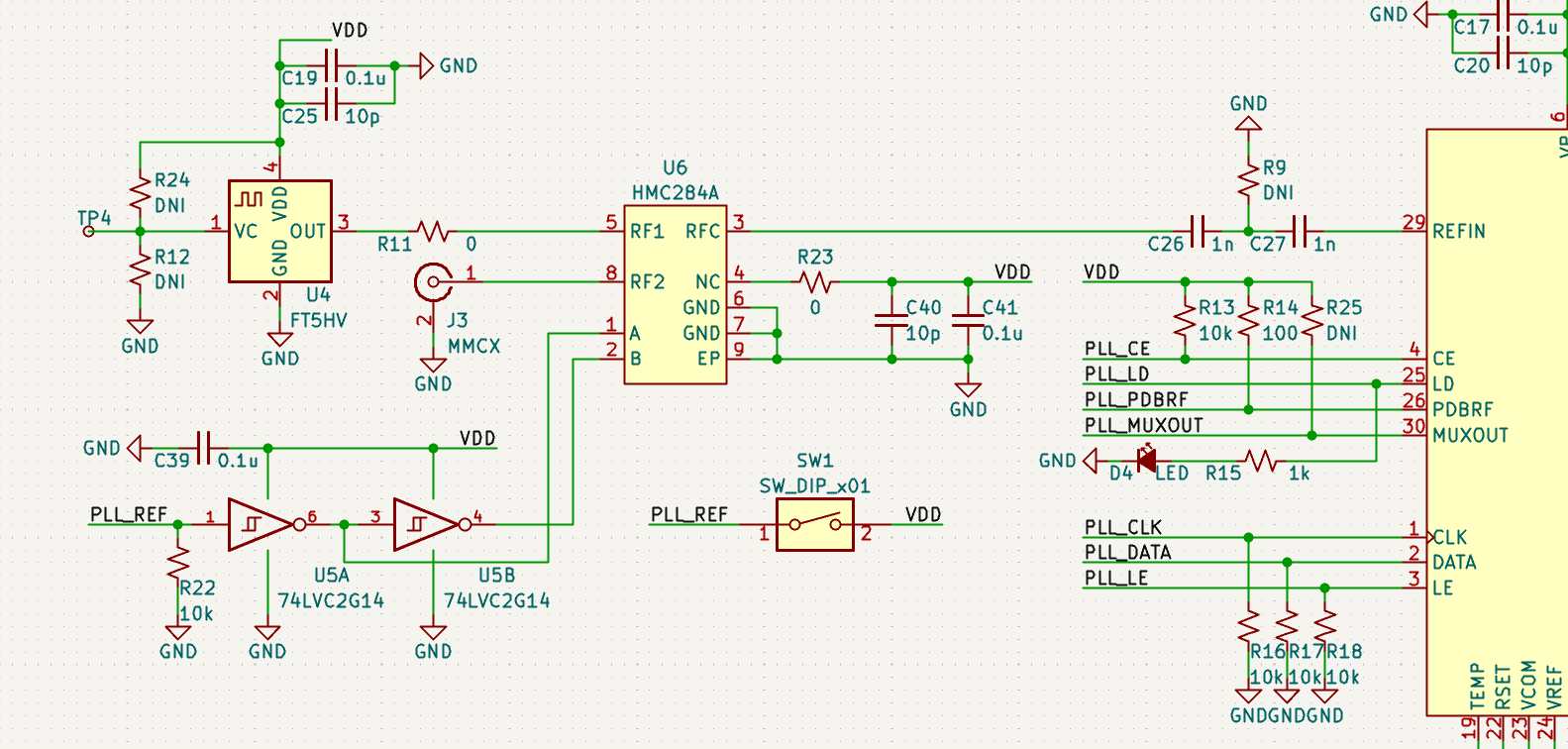

1.3.参考输入设计

参考输入端基本照抄了评估板的设计。由于想加一个外部输入的选择,又不想用跳线(排针太高)和开关(太奇怪),毕竟有可能要把参考时钟给到100MHz,所以上了一片射频SPDT,然后为了方便控制,又上了个sot23封装的双非门处理逻辑,再上了个拨码开关控制非门输入,简直就是简直了。这么麻烦主要还是因为我想把通信接口往PMOD上靠,而PMOD定义给出的8根数据线实在不够呀。

最终参考输入的设计如下图:

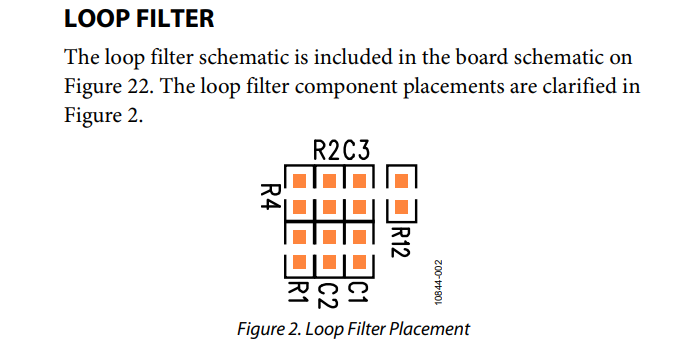

2.原理图及PCB设计

基本上是照抄ADF4350的评估板,稳压器采用了ADP3334,虽说感觉LT1763更合适。这二者都号称对输出电容很宽容,但上次调LT1763给我振了个爽,不知道这次用ADP3334会不会翻车。其实最理想的选择也许是HMC860,专为RF电路设计,QFN封装也更小。但HMC860的输出电流实在是太小了,对于ADF4350的几组供电来说捉襟见肘,还是下一版再考虑吧。

环路滤波器和射频输出部分的布局参考了ADF4351评估板。这ADF4350和ADF4351芯片差别不大,评估板的差别倒是挺大的,不知道是不是同一组开发的。

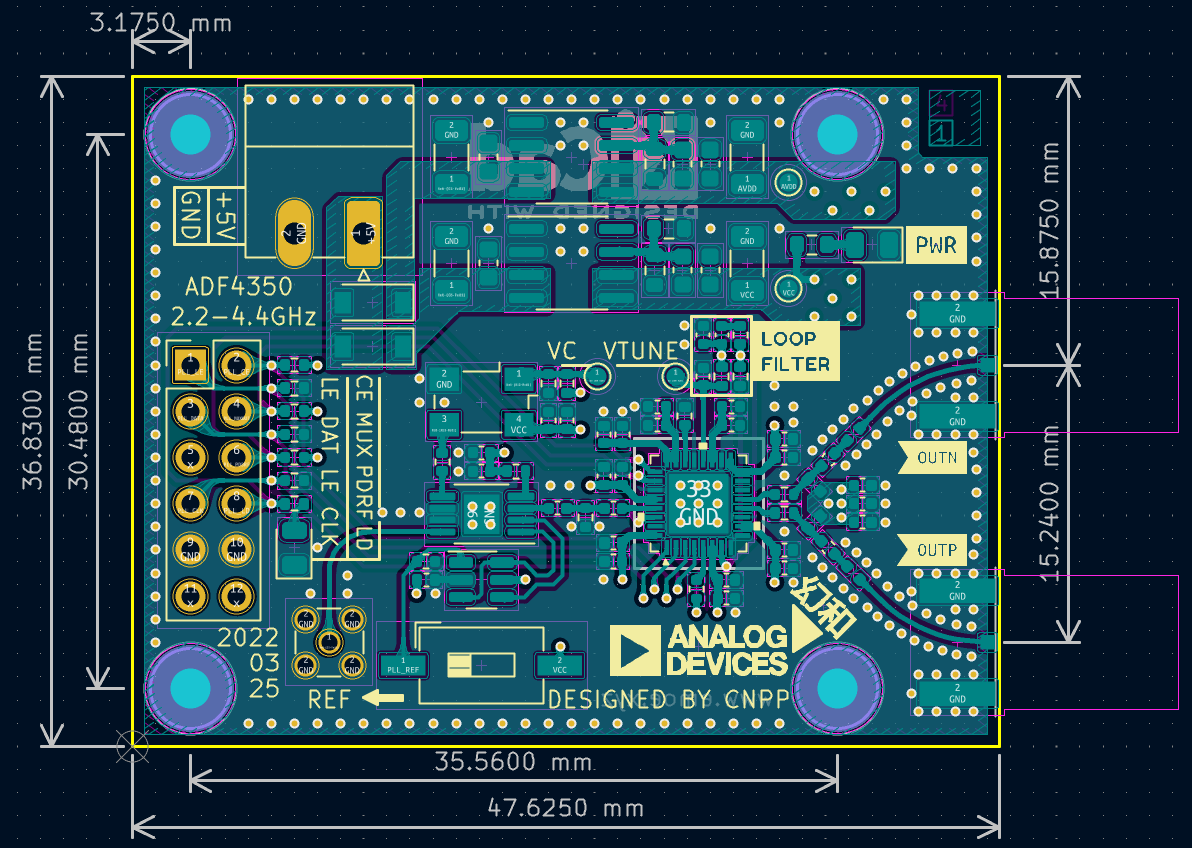

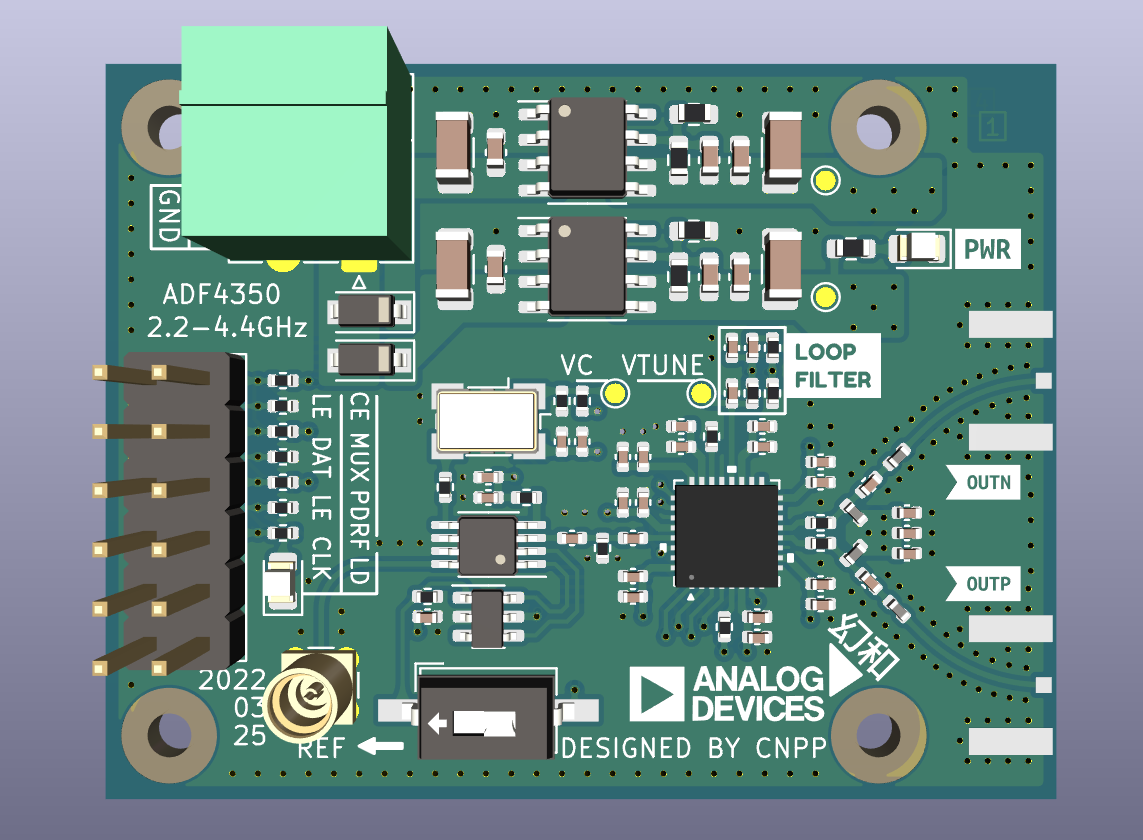

最后是完工的PCB设计样貌:

3.上料焊接

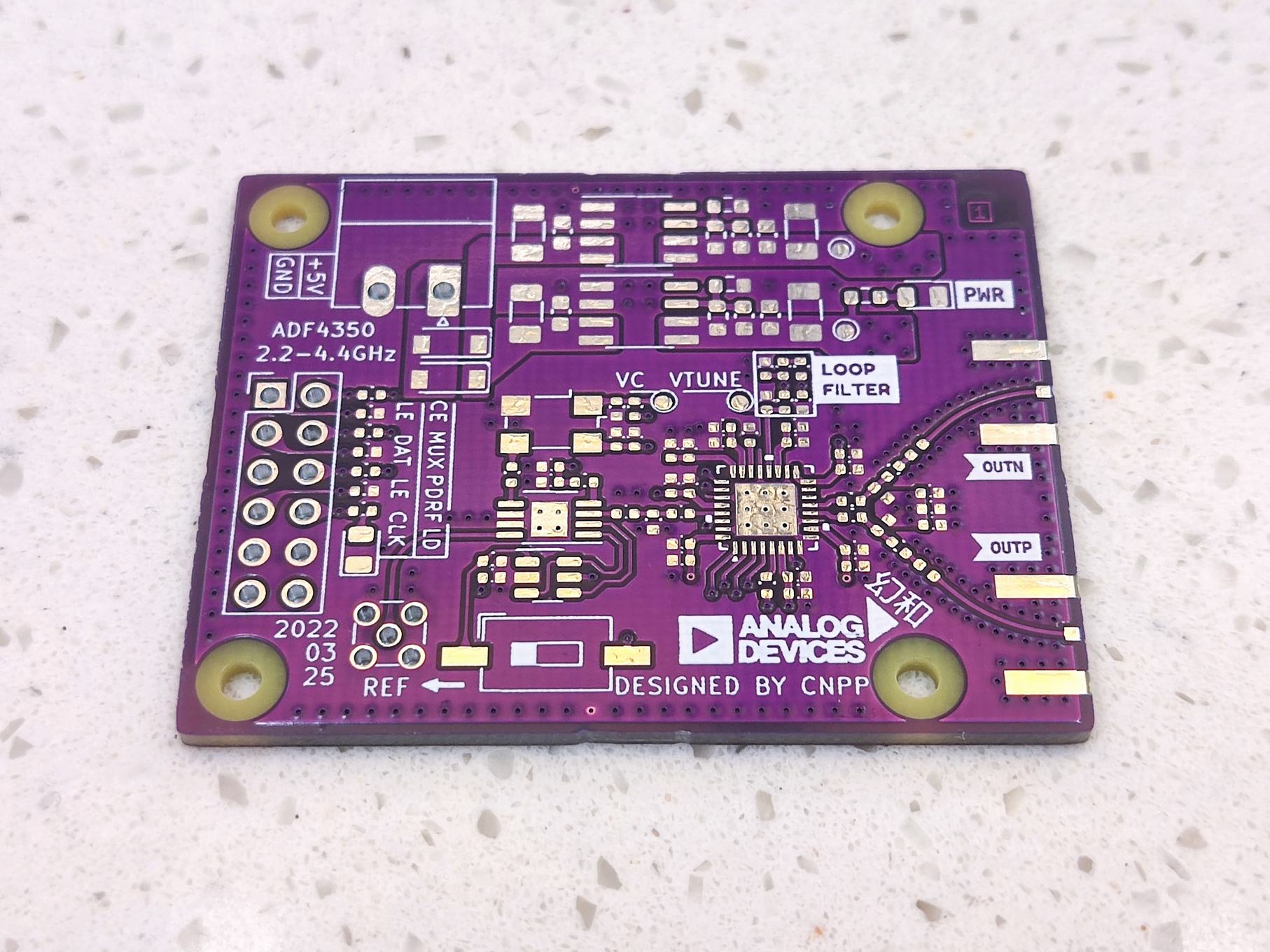

3月27日在嘉立创投板,4月1日拿到:

配BOM,未完待续

两个5dbm合起来是8dbm吧

是的是的,我当时写的时候没多想,疏忽了。不过手册中的测量结果表示可以达到10dBm也挺神奇的。这么多年了板子还没做出来,其实该实测一下的(((