先说明一点,这个板子最初设计的目的是用来驱动IMX178传感器的(更多内容即将到来),也就是想做一个针对应用特化的板子,没有往开发板那方向去想。

不过后面研究了一下,发现扩展性也还说的过去,勉强算个开发板?

另外市面上开源的、带DDR3内存的开源Lattice板子很少,所以打算单独开个文写一写。

和往常一样,该板子的设计全部开源在Github上,地址文末可以找到,欢迎复刻。该文章同步在我的B站专栏进行发布,可以转载。

本文目录

设计需求

开头说过,这个板子最开始是为了采集IMX178传感器的图像设计的,所以我给板子定下几个基本目标:

- 需要有最少8条LVDS数据通道+1条LVDS时钟通道,用来接收图像传感器数据。仅接收不发送(这个很重要)

- 有24bit-RGB显示屏接口,用来实时预览画面,或者用作其他通用IO

- 使用FT232H作为上位机连接通道,USB2.0速率

- 板载DDR3内存,最少16bit位宽,最好32bit,以应对大量吞吐,同时用加宽总线的代价降低内部逻辑时钟的速度。

- 六层板设计,因为我还有一次200元的六层优惠券没用

按照这些目标就可以开始选型了,但在选型之前,我想说说关于FPGA前期硬件规划。

FPGA硬件的前期规划

有人说FPGA是万能芯片,就给人一种错觉:这玩意我爱咋来咋来,闭着眼弄都可以跑。

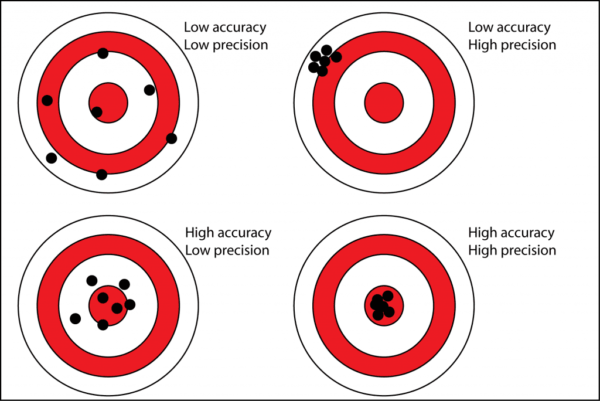

我刚入门FPGA那会也是抱着这个想法的,然后画板子、写Verilog都是“想当然”的去做,结果可想而知:综合器闹脾气、时序违例、布线器报错,导致最后做出来的东西是完全不工作的。

所以我把这个作为一个大章节,就是因为太重要了,但网上很少有文章提及的FPGA硬件设计的前期规划,主要重点在高速接口和DDR内存接口的安排上。

高速接口

相较于动不动就能跑上3、4个GHz的CPU、或者其他通用处理芯片/ASIC,FPGA内部逻辑在进行复杂处理时能跑几百MHz就烧高香了(或者有富哥整点Ultrascale+,那倒是能跑更快点),更多时候还是卡在200MHz附近或者更低,对于中低端FPGA,资源使用率上来后,不到100MHz的FMax也是很正常的。而高速接口动不动就几百MHz,甚至上GHz的时钟速度,差距十分悬殊。

除了速度跟不上以外,FPGA内部逻辑还有个特点,就是只能使用单边沿触发。而高速接口通常使用DDR(Double Data Rate)方式,也就是时钟的上升沿和下降沿都有数据传输。这可不是写一个 “always@(posedge clk or negedge clk)” 就能搞定的,这样写连综合器的语法检查都过不去,也就仿真里用用。如果是Serdes收发器,还要涉及时钟恢复、8b/10b编解码问题,FPGA内的普通逻辑块更加没办法实现了。

那FPGA上的高速接口是咋实现的?答案是在IO接口旁加入特殊电路,这些电路能以远超内部其他逻辑部分的速度运转,同时在硬件层面支持双边沿触发、时钟恢复等一系列特殊功能,从而实现数据的快速接收。

当接收数据攒够一定数量后,再统一的交给后面的逻辑,此时数据宽度增加,时钟频率降低到后级能够接受的水平,同时转换为单边沿触发逻辑。这个过程也可以反过来,内部处理完成后再交给特殊电路发出去。

一般情况下,用户可以使用IP核,或者自己写原语来调用这些特殊电路。但是,这种特殊电路肯定有使用条件的,例如只在特定的引脚上支持。由此引出要点:

FPGA硬件设计时,但凡涉及高速接口的,一定要多读手册,确定对应的Bank和引脚能支持想要的通信方式、通信速度,最好是在厂商EDA里验证一遍,写个简单的接口逻辑,然后把综合、约束、布线全跑通后,再根据结果确定电路原理图。

后文我会用这次板子作为例子说明Lattice ECP5的高速接口硬件设计过程。

DDR内存接口

说完高速接口,还有DDR内存接口可以补充一下。DDR内存接口有许多特点:

- 时钟的上下边沿都有数据传输,这部分设计要点上面提到了

- 使用SSTL接口标准,DDR3一般是SSTL15,需要给器件接入参考电压

- 单端和差分信号混合,地址线和数据线使用单端,而DQS和时钟信号使用差分

- DQ和DQS是双向的,器件需要支持双向切换

- DQS信号方向为“颗粒->FPGA”时,需要使用专用电路对DQS信号进行相移,确保采样时机正确

- 使用Fly-By拓补进行多颗DDR设计时,需要确认相应引脚支持延迟调整功能

这部分我就不过多的展开了,网上都能找到信息。总之道理和前文一样:多读手册,在EDA里验证通过后再做硬件,不然容易翻车。

芯片选型

FPGA

FPGA我选择了Lattice公司的ECP5系列,具体型号为LFE5U-25F-BG256。一个小型FPGA,价格十分的便宜,LCSC全新只要30多,TB上甚至20出头就能买到。

可能有人会问:ZYNQ7010性价比不是更高吗?为什么不用捏?

啊,这个说的确实没错,ZYNQ7010把LFE5-25F性价比按在地上摩擦。

但是嘛,首先:网上做ZYNQ的很多了。其次:ZYNQ性价比高没错,但Vivado那坨屎我打开就犯恶心。最后:哥们喜欢Lattice❤

电源芯片

主供电使用EA3059,老朋友,用了很多次没出过问题。每路2A的供电能力也够25F这个规模的FPGA用了,Lattice家的片子都挺省电的,好评。

因为这次设计用到了Fly-by拓扑结构的内存走线,故添加一颗TPS51200DRCR,用来产生DDR颗粒所需的VREF参考电压和VTT端接电源。

最后,加上一个MT9284,用来给LCD屏幕背光提供恒流源。

FT232H使用内置LDO降压,就不从EA3059那边取电了,至此电源部分就齐活了。

内存芯片

南亚NT5CC128M16,用这个没其他原因,只是因为之前买错了,本来想买4Gbit颗粒买成2Gbit的,库存了好久,干脆用起来。

注意: 因为这个颗粒只有14条地址线,所以设计的时候我偷懒也只拉了14条线。如果装了4Gbit颗粒,就只能用到其中一半容量,想用满的朋友可以自己多拉一根地址线。

剩下乱七八糟的杂项

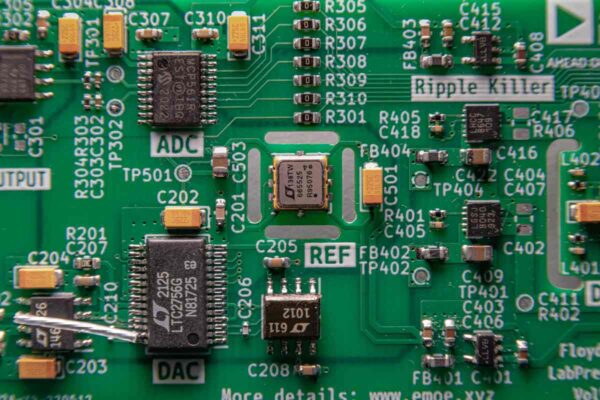

整个板子也不是很复杂,主要的芯片就那几个,Flash是W25Q128,给FPGA用。EEPROM是93LC56BT,给FT232H用。

除此之外就是被动器件了:各种电容、电阻、LED、接插件啥的,值得提一嘴的是电感,长江微电T-Core系列,小体积超好用强烈推荐。

原理图设计

高速接口/DDR3内存引脚分配

目标部分,我提到至少要分配8条LVDS-DDR数据通道和一条LVDS时钟通道,以及32比特的DDR3内存,而后又提到这种高速接口不能胡乱一顿接就完事。

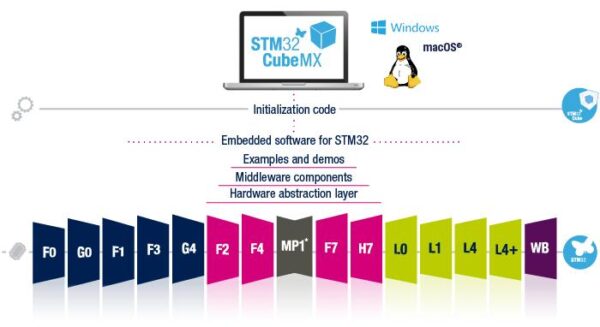

我不知道其他家有没有这种工具,但Lattice的Diamond可以让软件自动帮你分配引脚,然后再自己进行微调,最后检查DRC不报错即可。

打开Diamond新建工程,选择器件后在IP-Express里选择“ddr_generic”,打开界面参数设置如图,之后点击生成。

重点来了,点开顶部的Planner,把eclk_group拖到右侧的图示里,软件就会自动帮你把这些信号绑定到可用引脚上,如下图。

这些就是使用SUBLVDS接口、8通道、工作在300MHz下时,器件能够处理该信号的输入引脚。你可以根据自己的需求进行一些微调,调整后点击顶部的DRC,不报错即可。最后把这些引脚的位置记下来,这就是我们原理图里要用到的连接方式。

同理,退回主界面,生成一个“ddr_memory”的IP,我的设置如下图。

然后用同样的方式自动分配引脚,自己进行调整。需要注意的是,DDR3组内的DQ信号可以互换,而地址/控制线也可以在FPGA侧的Bank内互换,只要DRC通过那就是没问题,这在后面拉线时候非常有用。最后结果如下图:

DDR3内存的地址控制线在最顶部的Bank,然后两个16比特颗粒的DQ和DQS各占右侧两个个Bank出线。ECP5系列的FPGA只有左右两侧的Bank支持DQ和DQS信号,而地址和控制信号可以放置在同侧Bank,也可以放在顶部或者底部的Bank。

同时,接入了DQ和DQS信号的Bank需要接入VREF电压,地址/控制线不要求VREF电压(所以才可以放在顶部Bank,顶部Bank压根就没给你接VREF的引脚)

以上这些信息,都可以在Lattice官方手册《FPGA-TN-02035-1-3-ECP5-ECP5-5G-HighSpeed-IO-Interface》中找到

其他部分

剩下的就很简单,跟着厂商应用手册走就好。需要说明的只有两点:

FT232H以FT245-FIFO模式连接到FPGA,并且CLKOUT必须连接到FPGA的时钟专用引脚上(在这里是标有PCLK的FPGA引脚),这是从FT232H输出的同步时钟。

事实上,任何进入FPGA的时钟都要连接到标有PCLK的引脚,只有这样时钟信号才能驱动内部逻辑,不然布线会报错。

DCDC部分,反馈分压电阻没有给出具体值,这个依据个人而定,看你手头有啥合适的电阻就焊,电压对应上就行。

拉线

这个…好像没啥可以说的,DDR3内存拉线应该是最难的部分,但也只能多练。善用FPGA带来的灵活性,在规则允许的范围内调换一些线序来方便走线。下面是Layout完成的结果

使用了盘中孔工艺,最小走线宽度5mil,DDR3内存和LVDS接口部分等长并控制阻抗(好吧并不是很严格的阻抗控制,但能跑)

下单时候多加20块钱选择高TG值板材,这样不容易在焊接时给阻焊搞掉,这钱真不用省,极大改善生活质量(雾

焊接

普通元器件用的183度中温锡膏,风枪280度焊接。

焊接BGA前先用助焊剂给芯片和PCB抹上薄薄一层(别挤太多了,一定要抹开抹薄!)。焊接的时候铁板烧+热风枪上下夹击,风枪280铁板180左右,这套组合干原厂的无铅锡球成功率很高,对于自己重新植了中温球的芯片就更简单了。

下面是焊接完成的效果(懒得洗板):

测试时间到

LCD显示屏测试

用到了正点原子教程代码,测试效果如下:

FT232H通信测试

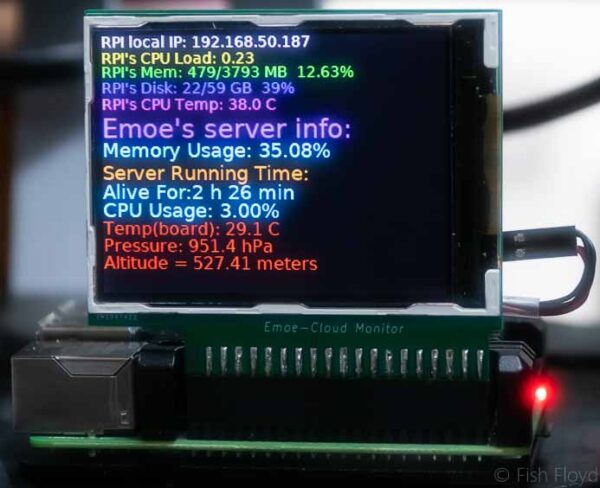

用到了FPGA-ftdi245fifo这个库和测试软件,结果如下:

DDR3内存读写测试(16比特)

三个项目拼起来,组合成一套测试,分别是:core_ddr3_controller、core_ram_tester、core_dbg_bridge

测试结果如下:

需要注意的是,这个库在Lattice的FPGA上暂时只支持16bit宽,50MHz时钟速度,2:1速率操作。

计划后续会对这个库进行一些改造,让其支持32bit宽,4:1的接口速率,以增加吞吐量。

LVDS高速接口测试

使用IMX178传感器板子进行测试,结果如下:

(啊,反正就是能正常接收就对了,数据上看不出什么规律,这东西也没个测试模式啥的)

除了LVDS接口测试以外(因为需要额外硬件配合),剩下的三个测试源码和工程我都一并打包上传了。第二和第三个测试需要上位机软件支持,具体请移步相应的github repo查看。

总结

至此,FPGA部分硬件已经制作完成,配合IMX178传感器板子,希望不久后能顺利弄出图像来,然后再水几篇文章)。感谢您的支持!

可以开源下imx178的图纸吗,自己焊了个启动不了

问一下您的阻抗是怎么计算的呢,正在搞lpddr4

被jp气晕了(x

可以用计算器计算,前提你能估计频率,当然离实际比较远,因为各种因素都会影响,当然最好仿真下,然后用高级测试设备测试,就能完美实现,条件有限,所以大多实操都是经验来的。

加个千兆网络PHY可实现GigEVision相机呢。FPGA换个ECP5-45,整个RISC-V软核、简单的ISP、GEV协议栈和以太网MAC。

非常感谢评论,这些想法我是有在规划的。不过可能还需要亿些时间,最近刚刚解决Lattice官方DDR3控制器IP无法使用的问题(原因是他们的EDA有bug)

厉害!