先放个成品图😎

——————————————————分割线——————————————————

前一阵子突然想要一个USB隔离器,于是先上淘宝看了看,发现大多数都是下面这种几十块钱的烂货:

这种方案一眼就能看出来:一片打磨拆机的ADUM3160+一个1块钱的B0505S-1W,其他各种保护则是基本没有。

其中,ADUM3160限制了USB的速度,使其只支持Full-Speed(12Mbps):

B0505S-1W更是重量级,隔离耐压只有1500Vdc,效率低发热大不说,纹波与EMI更是巨大,而且隔离输出的电流只有可怜的200mA,并且还是非稳压输出!!!

这还是立创上面有卖的,比较正规一点有手册的产品,淘宝上卖的估计就给你用个1块钱的隔离模块拉倒。

由此,因为嫌弃现成的东西太烂,于是我准备自己做–个好的——外观好看,性能也好。

1-预期性能

由于是自己做,那对于性能的要求自然是各项拉满,具体如下:

1.USB2.0 High-Speed 480Mbps的速度

2.5000kVdc以上的隔离电压

3.至少1.5A的输出电流能力

4.输出稳压为5V

5.低EMI,低输出纹波

2-主要芯片选型

2-1 USB隔离芯片选型

目前市面上主流的USB2.0 HS隔离有两种方案,TI的ISOUSB211以及ADI的ADUM3165/3166/4165/4166(数字不同仅代表隔离耐压以及时钟输入方向不同)。

这里选用了TI的ISOUSB211,因为它小一些而且性能够,最重要的是好买一些(

2-2 隔离电源芯片选型

选芯片首先要确定拓扑,这里首先排除天生不太适合低纹波低EMI的反激,然后排除较为复杂的谐振变换器比如LLC之类的,最后选择了较为简单,并且适合低EMI与低纹波的推挽拓扑。

这里为了追求低EMI与低纹波,打算选用LT的超低噪声推挽稳压器,基本上就是LT1533/LT1683/LT3439/LT3999这四个。

由于除了LT3999之外其他的都是SSOP/SOIC封装的,太大了,所以这里打算用LT3999的DFN封装。

2-3 次级侧稳压芯片选型

由于LT3999不带反馈,所以需要在次级侧做稳压,为了追求低纹波低噪声,这里打算用一个LDO来完成稳压;为了尽可能提升效率,这个LDO要适合工作在小压差下,并且输出电流≥2A。

TI的TPS7A8300,这个非常便宜(立创买几块钱),输入耐压到6.5V(AbsMax为7V),输出电流2A,Dropout在2A时仅为125mV,非常合适。

2-4 其他DC-DC选型

2-4-1 LT3999配套Boost选型

由于LT3999的开关限流为1A,为了保证次级侧的输出电流大于1.5A,这里需要抬高一下LT3999的输入电源轨,考虑到一些纹波电流以及留一些余量之后,LT3999的输入电压应当在12V-15V左右。

所以,这里需要一个BOOST稳压器,把USB的5V升到12V-15V左右,在送入LT3999。

挑了半天感觉TPS61178最合适,引脚排布合理,最高出20V,开关限流10A,同步整流,效率应该能做到比较高。

2-4-2 ISOUSB211配套Buck选型

另外,ISOUSB211还需要1.8V的供电,尽管可以使用内部的线性稳压器来产生,但是这样会烫烫烫烫,所以我打算在外部用一个BUCK由5V产生1.8V,由于这个1.8V没什么要求,所以就选一个小小的也很便宜的TPS82130就可以了。

2-5 保护部分选型

保护部分主要分为电源线上的保护与数据线上的保护

2-5-1 电源线保护部分选型

首先,次级侧(隔离侧)的输出打算加一个最大电流为2A的自恢复保险丝,看到Little Fuse的1206L200SL不错,导通电阻很小,就用它了:

然后,电源线上要有一个TVS到地,看到TI有一个新型的TVS,叫TVS0500,貌似性能不错:

其内部就是一个有源FET钳位,如下图:

它的钳位能力很不错,所以这里打算选用这个,但是又担心它的响应速度不如传统的TVS,于是准备再给它并一个传统的TVS,这里选一个低寄生电感的小封装TVS即可:

这里插一句,很多地方经常把ESD与TVS搞混,其实这俩不太能混用;ESD主要用于数据线保护,承受冲击能力较差但结电容小,用在高速信号线上插损不大;TVS主要用于电源线防护,承受冲击能力强,结电容大,结电容大用于电源线上是好事,但是用于数据线上就会造成过大的插损。至于其具体的内部结构,东芝有讲(https://toshiba-semicon-storage.com/cn/semiconductor/knowledge/e-learning/basics-of-tvs-diodes.html)。

2-5-2 数据线保护部分选型

USB数据线保护本来习惯性的想用RCLAMP0522P.TCT的,结果偶然发现ST有个USB专用ESD,还集成了共模电感,感觉很不错,于是选了它:

3-原理图设计

选型完成,接下来开始画原理图!

这里为了尽量压缩体积,打算把信号和电源分开做两个小板,立体堆叠。

3-1 信号隔离部分

基本没啥特别的,配置一下ISOUSB211,加两个Buck和一个LDO,再来点外围就好了

3-2 隔离电源部分

隔离电源部分也很简单,一个Boost+推挽:

其中,D3,D4用来防止变压器漏感造成的电压尖峰击穿芯片,并且回收一部分能量到输入端;类似反激里面的一个肖特基串一个齐纳的钳位电路,不过这里为了减小占板面积,用一个双向ESD替代,效果一样。注意这里最好选不带回扫的ESD。

次级侧这里我改变了二极管的连接方式,这样二极管可以直接连接到大面积的地,方便散热。综合考虑正向压降与反向漏电流,这里D1,D2选择PMEG3050BEP,以最大化效率。

L1这里起到抑制电流突变的作用,可降低电流纹波与斜率,同时改善EMI降低纹波,并且提升效率与最大输出电流能力。注意L1与变压器连接的节点不要加电容,这样虽然输出纹波可能更低,但是电流纹波与斜率会变大,EMI变大,效率降低,输出电流能力也降低。

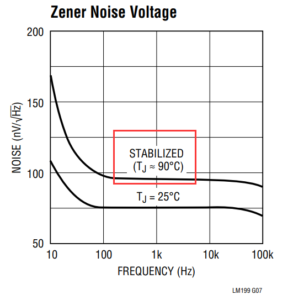

由于漏感,DCR,开关管压降以及二极管压降,整个推挽隔离电源的负载调整率并不太好,要保证输出1.5A时仍有足够的压差给后级LDO,在负载很轻的时候输出电压可能过大;为了防止击穿后级LDO,这里加入一个高精度的齐纳管D6,保证输出电压不超过7V,也就是TPS7A8300的AbsMax Vin。

在LT3999的两个开关节点之间加入R3与C6,降低开关节点振铃的频率,优化EMI。

Boost的设计直接交给Webench就行,在Webench生成的电路基础上,这里还加上了D5,为了降低Boost芯片内部上管体二极管的Qrr带来的损耗,提升效率。

4-变压器设计

4-1 变压器磁芯选型

我们这里需要一种比较扁平比较小的变压器骨架,那么就锁定EFD/EPC/ER系列,从中选取一个最小的且能提供至少8mm爬电距离的骨架,于是暂定EPC13。

根据Wurth的资料,EPC13用作推挽出个10W以上应该是没什么问题的:

而且它的尺寸也比较合适,于是这里选择了EPC13。

为了进一步提升效率,磁芯材质这里选择PC95的,磁损更小些。

4-2 绕制线材选择

为了足够的隔离耐压,这里选用了三层绝缘线:

4-3 绕制方式设计

在设计绕制方式之前,首先需要知道磁芯和骨架的尺寸,如下:

(10.5-6.9)/2=1.8mm,两侧的绕组空间为1.8mm

绕发的话,这里用次级包初级的绕法,这样绕制比较简单,而且漏感相对较小,如下图所示:

其中,绕组空间初次级两侧对半分,这样整体损耗最小;这样的话,单侧有四层线,那么每层线的最大直径就是1.8/4=0.45mm,胶带的厚度可以忽略,因为磁芯尺寸的10.5mm是最小值,通常为11mm,足以容纳。

这里直接选用0.45mm外径的线,其内部铜芯直径为0.25mm,而铜在200kHz时的趋肤深度是0.15mm,0.25mm的线用在这里趋肤效应不太明显,所以不需要用多股利兹线了。

然后,就是设计绕制圈数了,这里以略大于2:1的目标设计:

初级侧,单线绕,可以绕6.9/0.45=15.333,向下取整,15匝。

次级侧,双线并绕,可以绕(6.9-0.45)/(0.45*2)=7.1666,向下取整,7匝,这里绕6匝来增大电流变比,让LT3999尽量远离限流。

4-4 变压器参数计算

计算参数来源参照下面的TDK的PC95材质特性表:

与EPC13的特性表:

初级侧电感:L_{PRI}=A_{l}×N_{p}^2=1.06×10^{-6}×15^2=238.5μH

次级侧电感:L_{SEC}=A_{l}×N_{s}^2=1.06×10^{-6}×6^2=38.16μH

伏秒积:2×N_{p}×B_{s}×A_{e}=2×15×0.38×12.5×10^{-6}=142.5Vμsec

4-5 验证变压器参数

在16.5V输入,200kHz开关频率,占空比为LT3999的最大占空比48%下,推挽拓扑所需要的变压器伏秒积为:\frac{V_{in}×0.48}{f_{sw}}=\frac{16.2×0.48}{200×10^3}=39.6Vμsec,远小于变压器的伏秒积,所以变压器不会饱和。

同样在上述情况下,纹波电流为:ΔI=\frac{V_{in}×0.48}{f_{sw}×L_{PRI}}=\frac{16.2×0.48}{200×10^3×238.5×10^{-6}}=163mA,大约是最大输入电流的25%,也比较合适。

另外,我们希望通过变压器传递到负载的电流要大于励磁电流很多,所以一般要求次级侧输出的电感,即电源部分原理图中的L_{1}≤\frac{L_{PRI}}{5×(N_{PRI}/N_{SEC})^2}=7.632μH,

这里L1的实际值为4.7uH,满足条件。

5-Layout

Layout部分要注意的不多,保证隔离两侧有至少8mm的爬电距离即可。

6-焊接准备工作

6-1 绕制变压器

这部分比较简单,有耐心即可,成品如下图:

唯一需要注意的是,要绕紧一些,因为我充分的利用了绕组空间,绕不紧可能就塞不进去磁芯了:

6-2 升级TPS82130

TPS82130原厂搭载的是一个叠层电感,如下图所示:

叠层电感一般相比扁线一体成型DCR大,AC损耗大,EMI差,我这里找了个同封装的,准备替换它:

这是替换前后的对比图:

把TPS82130上面的电感拆下来后实测,DCR是我换上去的扁线一体成型的两倍多。

7-焊接

焊接就很简单了,先焊贴片再焊插件即可。

7-1 USB隔离小板焊接

7-2 隔离电源小板焊接

8-测试

8-1 电源测试

输出1.5A长时间也没拉爆,电源OK。

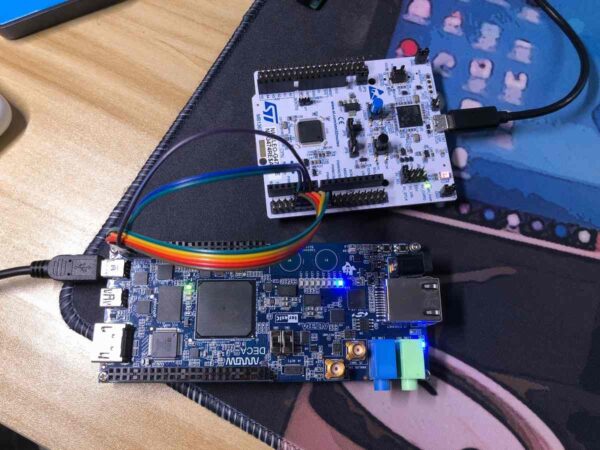

8-2 USB信号测试

传输文件能跑满USB2.0,信号OK。

8-3 隔离耐压测试

注意,做这个测试之前要把板子洗干净,不能有助焊剂残留。

用绝缘电阻测试仪,5kV档位测试1分钟,绝缘电阻一直超量程,OK。

9-成品欣赏

10-后续改进

为了进一步提升效率,以及优化隔离电源的负载调整率,这个打算从以下几个方面改进:

1.初级侧电源IC更换为集成功率MOS的IC而非LT3999这种内置BJT功率管的IC,来降低管压降,减小损耗。

2.初级侧换为支持低压大电流输入的IC,省去一级Boost,提升效率。

3.初级侧拓扑改为全桥,提升变压器绕组的利用率。

4.次级侧改为倍流整流拓扑,提升变压器绕组利用率。

5.次级侧整流管由肖特基改为MOS同步整流,降低管压降,提升效率。

除此之外,还打算改进以下几点:

1.Y电容换为Y1等级的安规电容,满足安规。

2.变压器工艺优化,加上背胶提升绝缘耐压;磁芯点胶来确保长期稳定性。条件允许的话,还要加上浸漆。

3.两个小板内部的两层增加PCB交趾电容,优化EMI。

![雷达信号处理-[3]-数字下变频(DDC)](https://www.emoe.xyz/wp-content/uploads/2021/11/1-1-600x184.png)

请问下,上面那一片小黄点是啥零件?

我现在Macbook Pro上如果插入USB线,经常会在USB 设备的VCC和D+,D-上出现5-10ns的20~30V的电压脉冲,USB设备经常损坏,请问这种隔离器能够隔离这黄总脉冲吗?

这种情况你需要在USB的D+和D-上加上ESD,如果需要钳位能力强的话,可以用深回扫的ESD。

完美复刻,感谢大佬分享

哇,可以看看复刻的东西吗?

大佬,能出一个么。

不出,你可以按照我文中写的自己复刻

思路非常不错