【Arty-A7填坑笔记】01:软硬件概览

0.前言

0.1.Arty简介

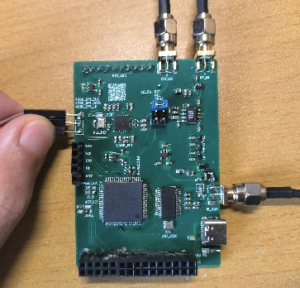

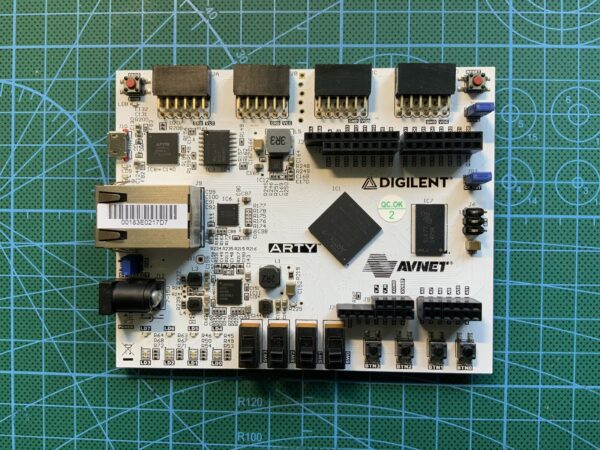

Arty-A7是Digilent公司推出的基于Xilinx公司Artix-7系列FPGA的开发板。目前有搭载XC7A35T及XC7A100T这两种芯片的版本,我手上的这块板卡为前者,拥有约33k的逻辑单元(Logic Cells),可以满足FPGA数字逻辑的学习以及简单软核系统的搭建。

不同于Xilinx7系列FPGA家族的明星ZYNQ7,Artix7系列均为纯可编程逻辑器件(不包含硬核处理器),因此,我们通常会在上面部署Xilinx的Microblaze软核系统,来实现SOC+FPGA的灵活设计。而Arty-A7板卡的设计也专为Microblaze软核开发考量,设有256MByteDDR3存储器以及百兆网口,方便搭配实用。

此外,板上除了学习数字逻辑开发时常用的LED灯组、拨动开关组外,将其余大部分引脚通过Arduino板卡接口及PMOD接口引出,没有设置多余的外设(个人认为这才是好的嵌入式开发板设计思路,很多时候开发板上一堆豪华的外设其实是懒得一个个都学会的)。

0.2.资源链接

Arty-A7技术参考导航页:

https://reference.digilentinc.com/reference/programmable-logic/arty-a7/start

为Vivado安装Digilent板卡支持的方法:

https://reference.digilentinc.com/reference/programmable-logic/arty-a7/start

Vivado Digilent 板卡支持包

https://github.com/Digilent/vivado-boards/

Digilent板卡引脚约束文件(.xdc文件):

https://github.com/Digilent/digilent-xdc/

关于如何使用Arty的DDR3的讨论:

https://forum.digilentinc.com/topic/8992-how-to-use-ddr3-on-xilinx-arty-board/

Arty-MIG-DDR3相关配置文件:

https://github.com/Digilent/Arty/tree/master/Resources/Arty_MIG_DDR3

Arty – Getting Started with Microblaze:

https://reference.digilentinc.com/learn/programmable-logic/tutorials/arty-getting-started-with-microblaze/start?redirect=1

Arty – Getting Started with Microblaze Servers:

https://reference.digilentinc.com/learn/programmable-logic/tutorials/arty-getting-started-with-microblaze-servers/start

How To Store Your SDK Project in SPI Flash:

https://reference.digilentinc.com/learn/programmable-logic/tutorials/htsspisf/start

1.开发环境

Arty-A7的开发软件还是选择Xilinx家的Vivado+SDK/Vitis啦,虽然一直有人吐槽Vivado的综合速度很慢,不过我认为使用Vivado的Block Design 图形化开发工具,配合自定义IP打包功能,学习、开发的效率还是很高的,从某种角度来说也是节省了时间吧。

截至本文撰写时,Vivado已经发行到2020.2版本。从2019.2版本往后,Vivado开始搭配Vitis嵌入式开发软件,在此之前则是SDK软件,其实二者的操作变化不大,稍加尝试便能迁移。

需要注意的是,Vivado各版本间不能上下兼容,原因其一在于使用高版本Vivado打开低版本工程时,需要运行自动迁移才能在高版本进行综合、布线等工作。其二在于不同版本Vivado内置的IP核版本也不同,同一IP核的不同版本间在引出的信号端口上都可能存在差别,因此在工程迁移的过程中,IP核的连接与设置可能发生变化,需要手动去修改,有的时候会非常麻烦。因此对于合作开发,一定要选择同一版本的Vivado。

另外,各版本的Viivado都或多或少的有些BUG,有些BUG会严重影响开发,就我使用过程中经历到的整理如下:

| Vivado版本 | 问题描述 | 后果 | 解决方案 |

|---|---|---|---|

| 2018.3 | 使用Microblaze,download.bit烧录后无法上电运行 | 使用了Microblaze的工程无法固化运行 | 安装AR# 71948补丁 |

| 2019.1 | 使用ZYNQ,SDK烧录NAND-FLASH时出错 | ZYNQ工程无法固化进NAND-FLASH | 通过命令行使用其他版本SDK/Vitis的烧录插件进行烧录 |

| 2020.1 | 自定义AXI接口IP核打包后不生成Driver文件夹,不生成嵌入式开发所需的驱动代码 | 无法为嵌入式系统(ZYNQ、Microblaze)开发自定义AXI外设 | 使用其他版本Vivado开发自定义IP后导入此版本使用 |

| 2020.2 | 生成Vitis工程后,大量头文件缺失,示例工程无法编译通过 | 无法进行Vitis嵌入式开发 | (将出现问题的头文件引号改为尖括号)(待定) |

可见,不少BUG会导致“这软件真没法用了”。就我来看,以及参考学长的意见,比较稳定的版本还是2018.3,在安装补丁后,我也暂未发现其他BUG,因此我们还是选其作为FPGA开发工具。

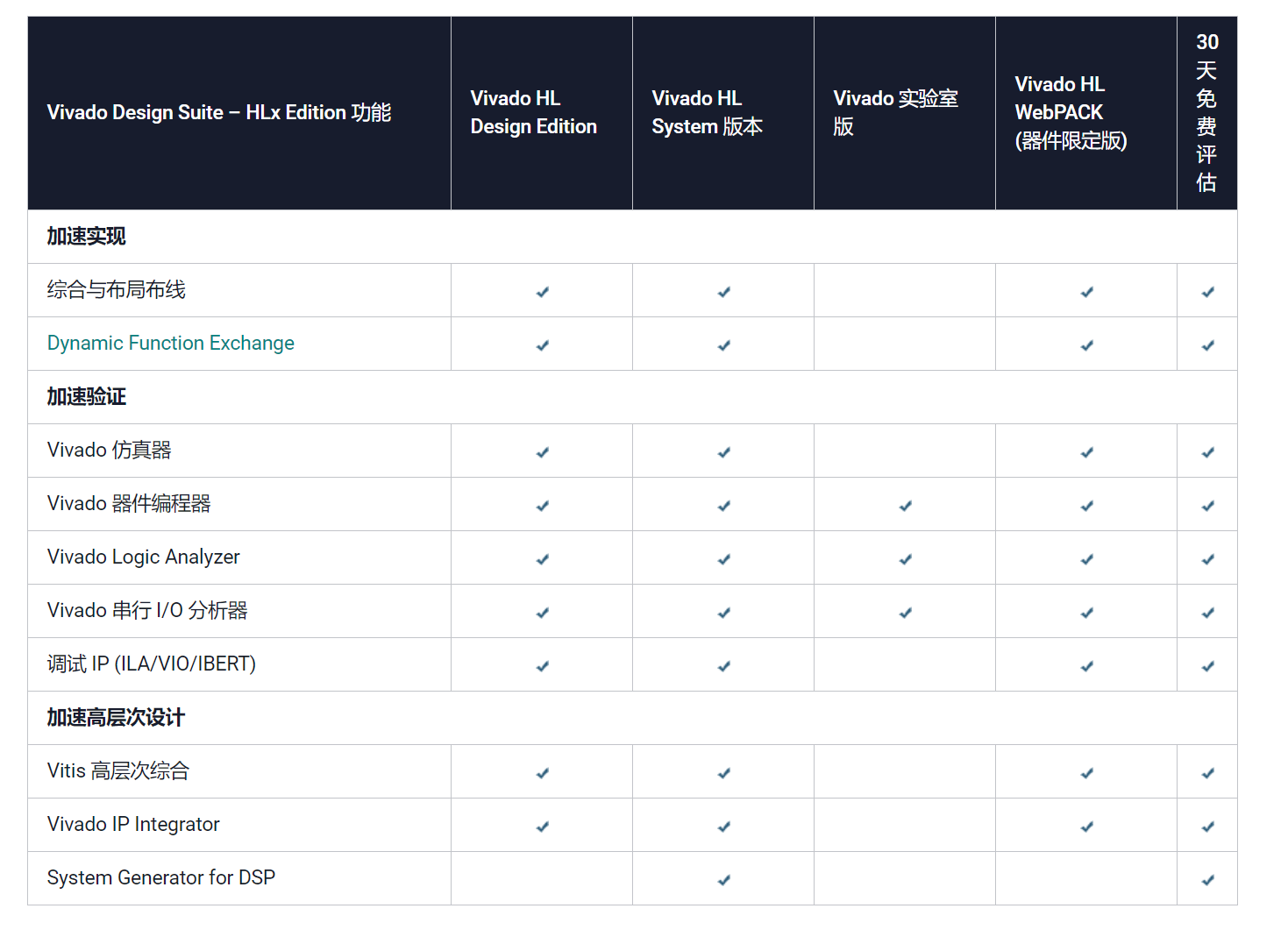

现在,Vivado各在支持的版本都提供个人可以免费使用的WebPACK版本,限制了部分高级功能以及大规模器件的使用,其他部分完全可以满足我们的学习(ZYNQ-7000、Artix-7、Spartan-7和部分小资源的Kintex-7这些能买得起的器件都可以用),还是非常推荐的。现在Vivado都采用未定义安装包,下载运行后可自行选择安装Vivado、SDK/Vitis和PetaLinux(我全都要也行),还是非常方便的。

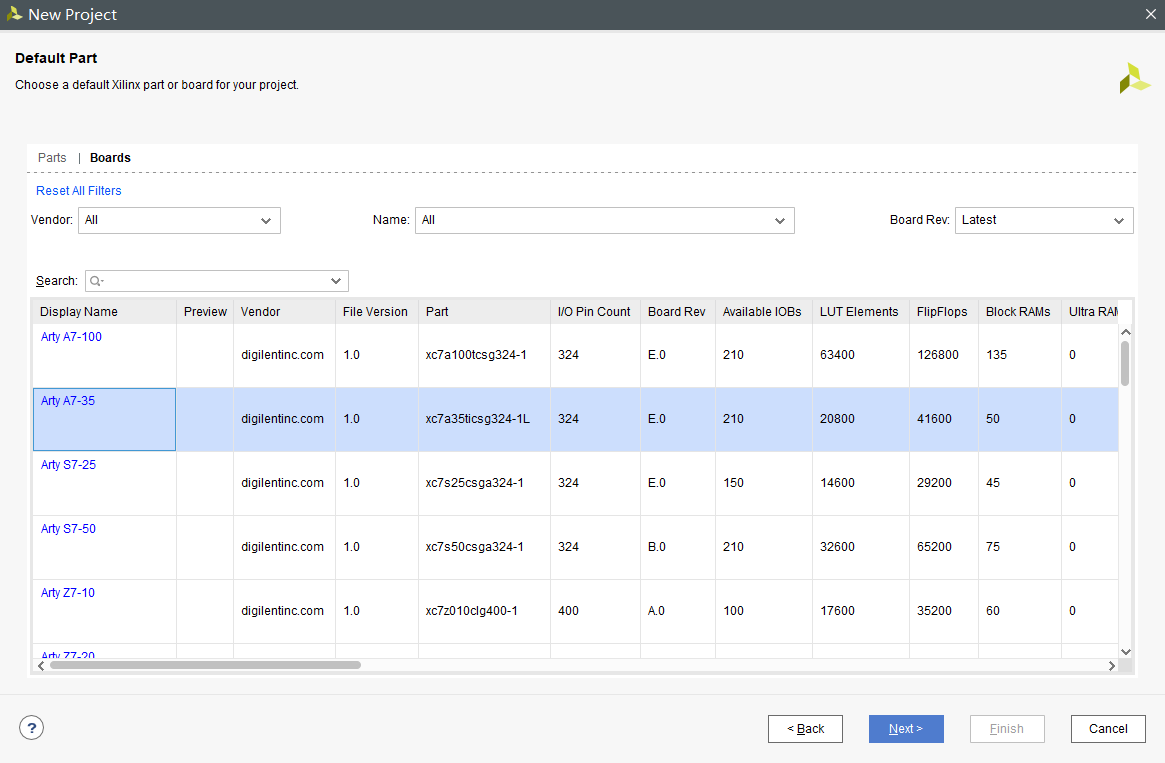

安装好Vivado后,可以在在0.2的资料链接处下载包含Arty-A7的板卡支持包,解压后将new/board_file中的全部文件复制,粘贴进Vivado的安装目录下的<version>/data/boards/board_files文件夹后重启Vivado,就可以在新建工程时选择对应的板卡了。

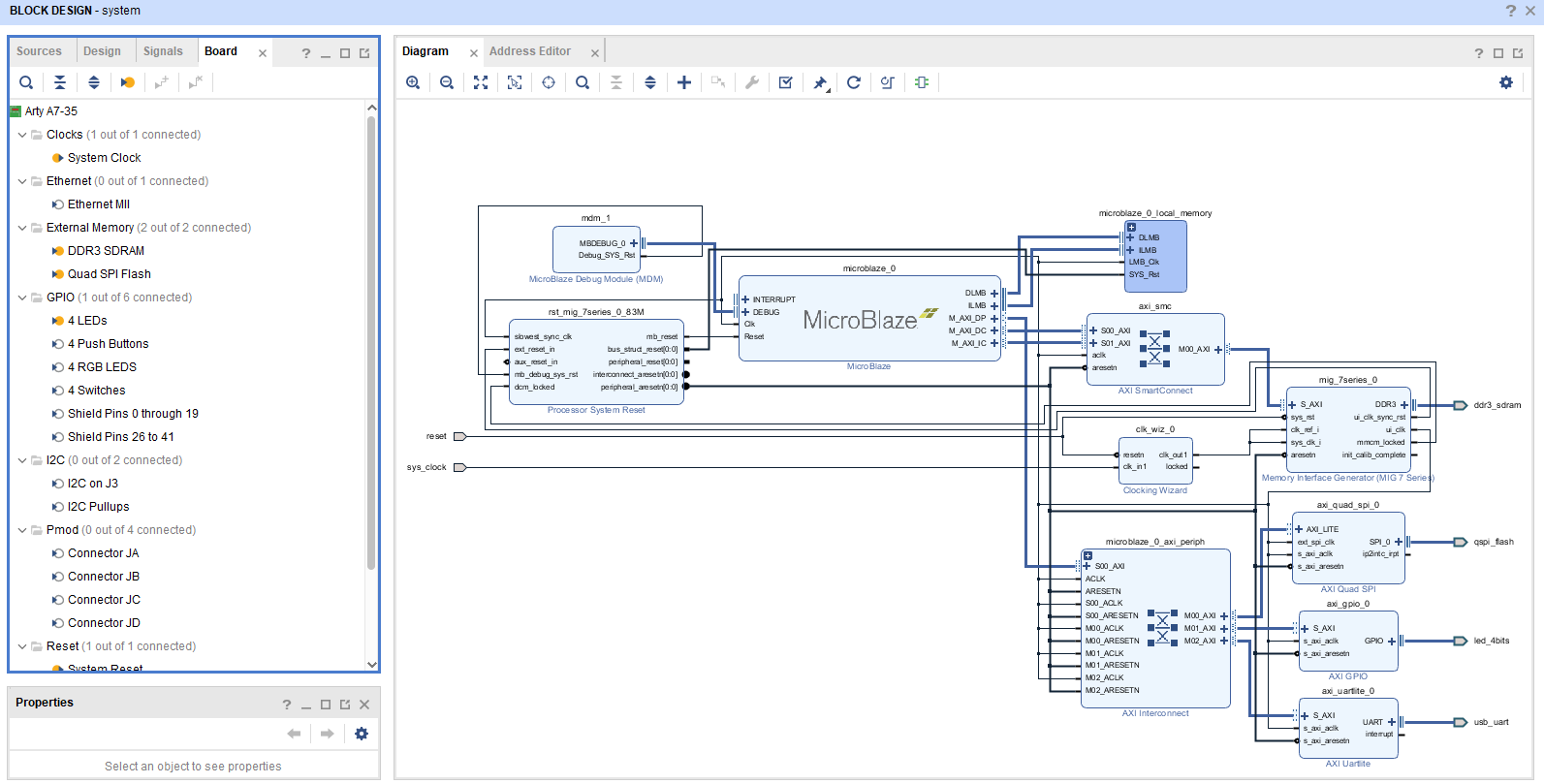

当然,也可以选择相应的芯片建立工程,比如Arty-A7-35T选择的芯片应为XC7A35TICSG324-1L。若选择板卡建立工程,则可以在Block Design 界面左侧栏就会有Board界面,在这里可以选择针对板上资源配置好的模块插入设计,十分方便,同时引脚约束也是做好的。

当然,直接通过芯片建立工程有助于学习开发的全过程,而且适用于各种板卡,不过通过板卡建立工程,配置出错的可能更小,所以我先选择了这种方式。此外,Digilent并没有提供板上DDR3的引脚约束资料(脚相当多啊,虽然对着原理图一个个抄下来也是可以的),而是需要通过提供的mig.prj文件配置一个migIP核来约束DDR3,直接使用板卡工程中的DDR3模块就可以避免这个麻烦。关于如何使用Arty的DDR3的讨论及Arty-MIG-DDR3相关配置文件可以参考这里。

2.硬件资源

Arty-A7的硬件资料主要可以参考技术参考页给出的用户手册以及原理图,在这里我主要记录一下之后开发会涉及到的硬件信息。

2.1.供电,下载及配置

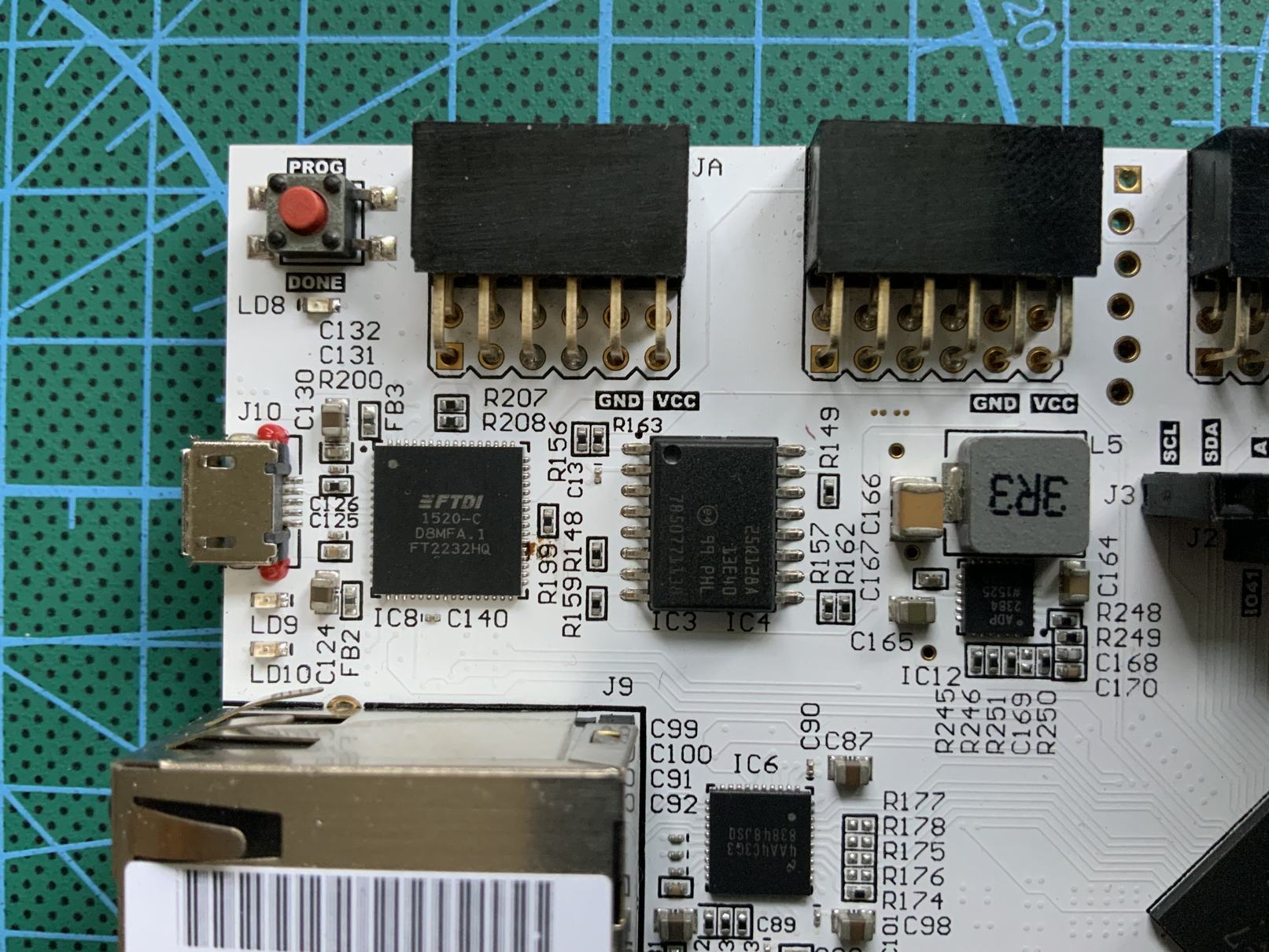

Arty-A7使用了一片FT2232芯片实现JTAG调试器以及串口,连接一条USB线即可同时使用,并可为板卡供电,使用十分方便:

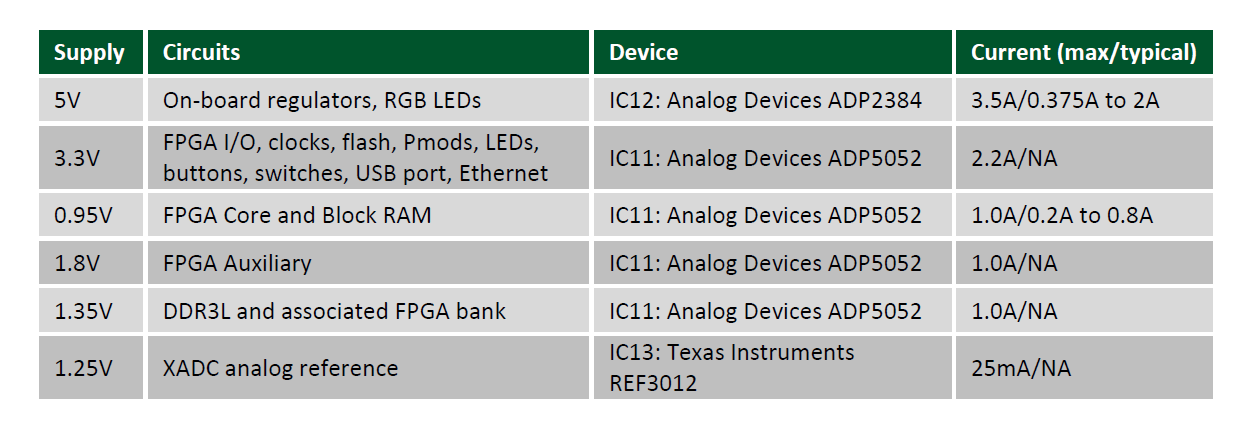

对于电源系统,手册给出的数据如下:

可见板上对外接口均为3.3V供电,且最大输出电流为2.2A,在通过板上PMOD口连接模块并供电时,要注意不超过这个限制。

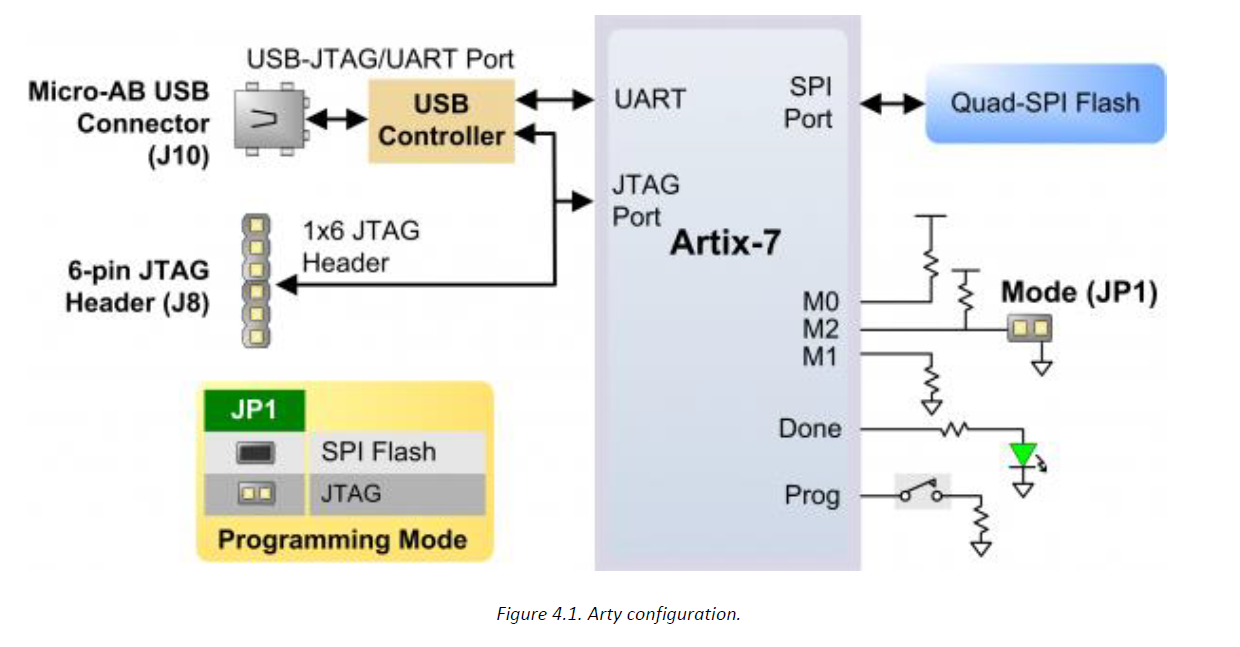

FPGA可通过JTAG或者QSPI-FLASH配置,并可由JP1选择配置方式,JP1默认闭合,即通过QSPI-FLASH配置,单无论怎样,只要FPGA上电,均可通过JTAG配置(将覆写FPGA)或烧录。PROG按键设置在板卡左上角,按下后,FPGA将重新配置,配置完成后,DONE标识的LED会亮起。

2.2.存储器

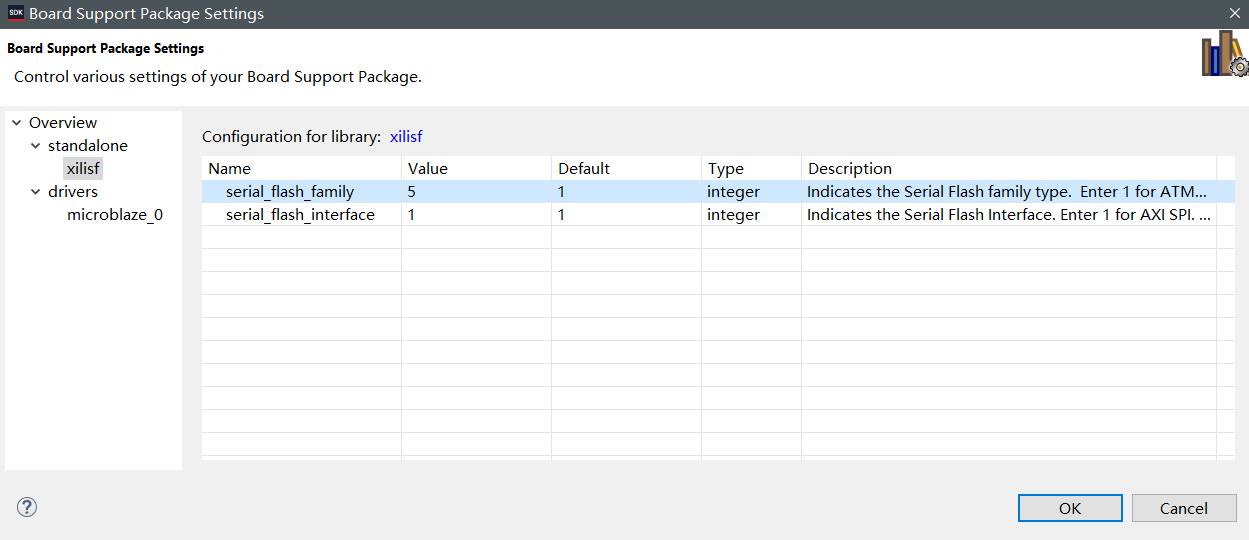

QSPI-FLASH的型号为N25Q128,属于Micron家族的串行FLASH,在SDK中要加入xilisfBSP时,注意选择serial_flash_family值为5:

另,图中两个选项的描述如下:

| Value | serial_flash_family | serial_flash_interface |

|---|---|---|

| 1 | ATMEL | AXI SPI |

| 2 | INTEL | PS SPI |

| 3 | STM(M25PXX) | PS QSPI (support families are (4) and (5)) |

| 4 | Winbond | |

| 5 | Spansion/Cypress,Micron,Macronix,ISSI | |

| 6 | SST |

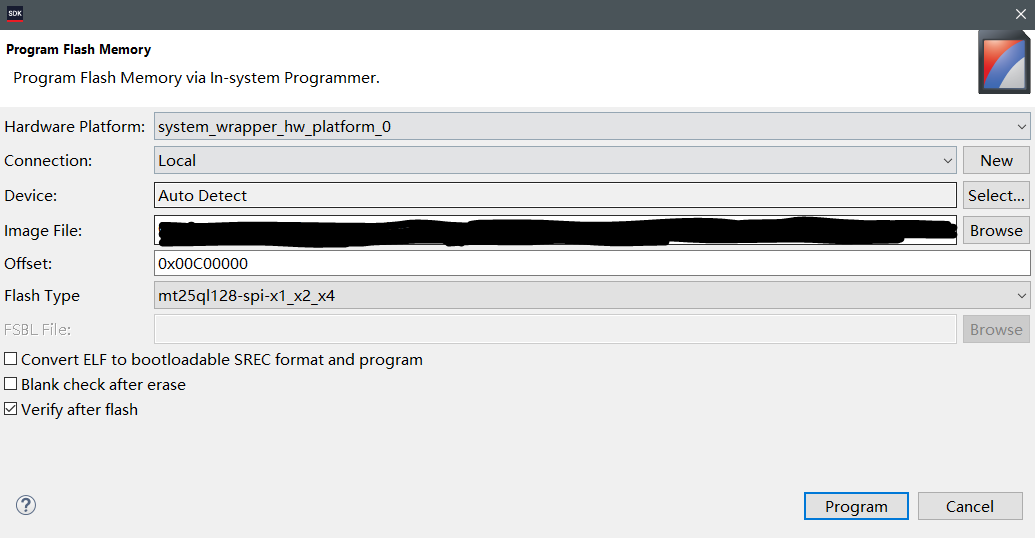

在烧写FLASH时,可选择兼容型号mt25ql128-x1_x2_x4:

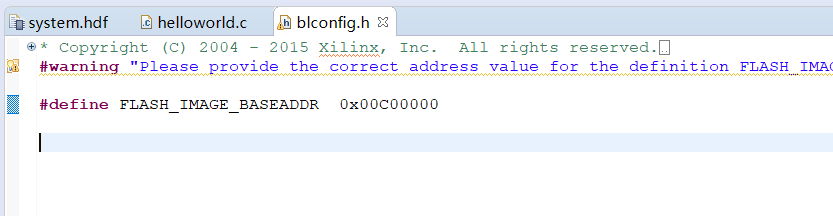

N25Q128的容量为128Mbit(16MByte)即0x00FFFFFFByte,由于FPGA配置时是从0x00000000开始读取的,建议使用QSPI-FLASH的前12MByte存储比特流以及Bootloader,后面的部分可用于存储用程序,即于地址0x00C00000处烧写。注意Bootloader的相关定义保持一致:

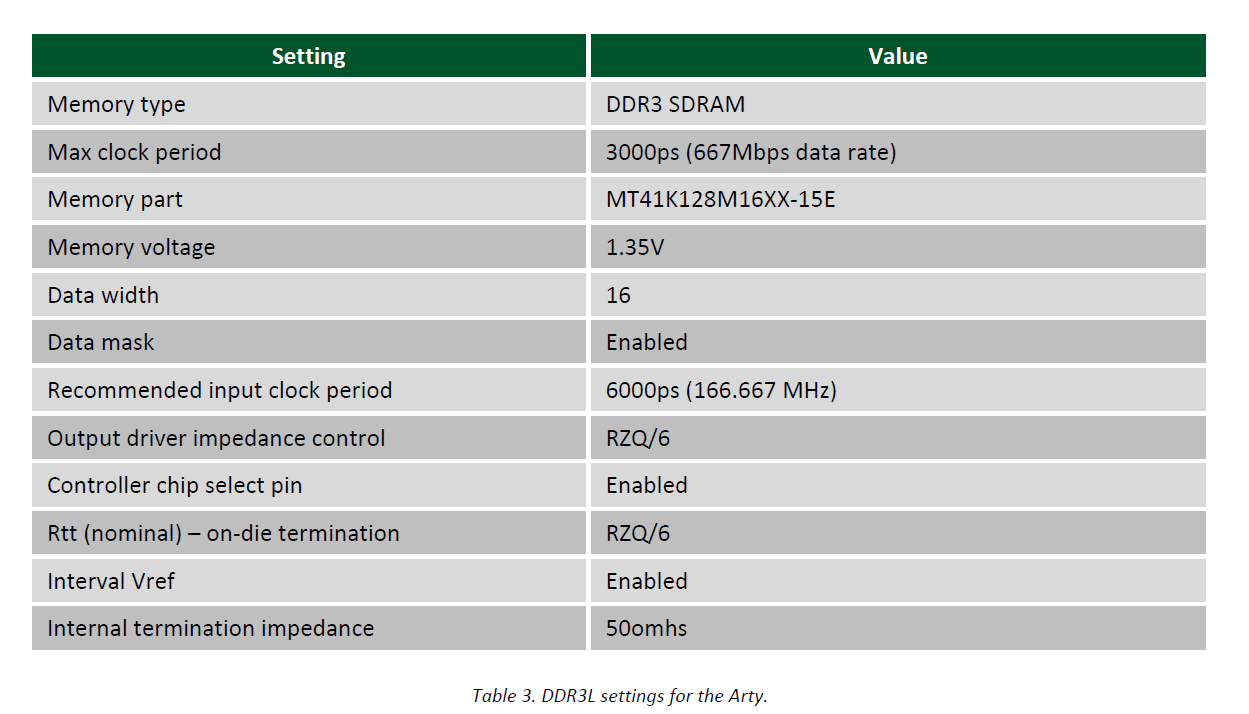

对于DDR3存储器,型号为MT41K128M16JT-125:K含义为:

- MT41:DDR3

- K:DDR3L,1.35V

- 128M16:120Meg*16bit

- JT:FBGA96

- -125:时钟周期1.25ns,即DDR3-1600

注意DDR3L接口电平为1.35V,而非DDR3的1.5V,在MIG配置以及引脚约束时要注意。另,手册中给出的参数如下:

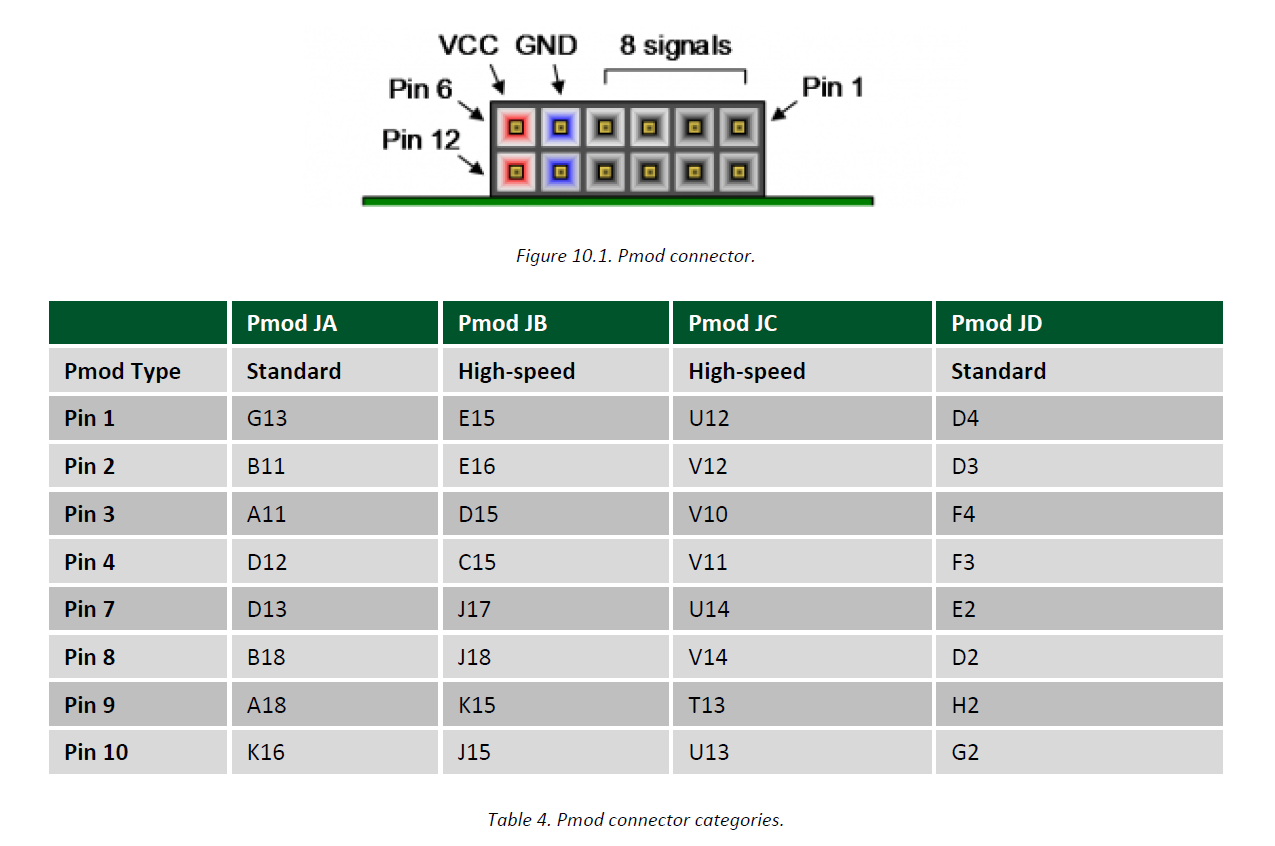

2.3.PMOD与Arduino接口

板上PMOD接口分为标准与高速两种,高速口引出了可设置为差分对的引脚。注意四个PMOD接口及Arduino接口的总输出电流不宜超过2A,同时他们最高可承受的工作电压均为3.3V。

2.4.其他外设及常用信号

| 名称 | 参数 | 引脚 | 备注 |

|---|---|---|---|

| 晶振 | 100MHz | E3 | 单端时钟 |

| FT2232-UART-TX | TX | A9 | 对于FPGA端为RX |

| FT2232-UART-RX | RX | D10 | 对于FPGA端为TX |

| Reset | 按键 | C2 | 按下为低电平 |

| LD4 | 单LED | H5 | 高电平点亮 |

| LD5 | 单LED | J5 | 高电平点亮 |

| LD6 | 单LED | T9 | 高电平点亮 |

| LD7 | 单LED | T10 | 高电平点亮 |

| BTN0 | 按键 | D9 | 按下为高电平 |

| BTN1 | 按键 | C9 | 按下为高电平 |

| BTN2 | 按键 | B9 | 按下为高电平 |

| BTN3 | 按键 | B8 | 按下为高电平 |

以上电平设置均为LVCMOS33。其他外设信息可参考手册,有需要再补充。

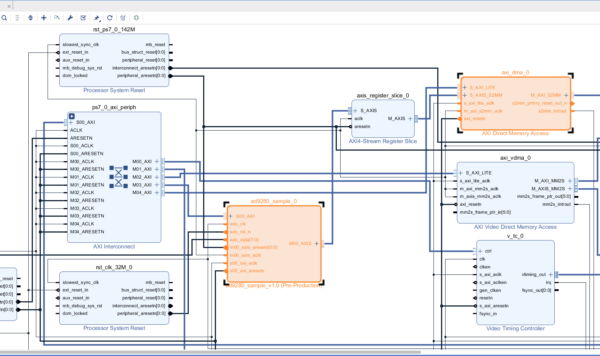

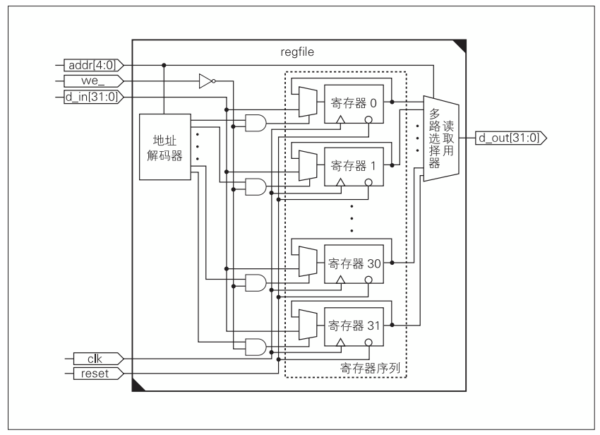

3.填坑路线

Artix7+Microblaze的开发方式与ZYNQ7000的裸机开发方式很接近,主要思路就是使用可编程逻辑资源设计外设,由处理器调动使用。Vivado提供的IP打包工具十分好用,加入AXI接口后,自己设计的外设在嵌入式编程阶段就可以像操作寄存器一样使用。

我嘛也没有什么太高的追求,主要就是想把FPGA当作一个更灵活的MCU来使用,方便完成一些平时的小项目,对此,Arty-A7是一个很好的平台,上电即用,接口外设恰到好处,学习起来还是很顺心的。目前的计划,就是把这个平台摸透,建立好完整的“片上”最小系统。因此,接下来几篇笔记应该是这样的(如果不鸽的话):

- Microblaze最小系统

- 自定义IP核

- DDR3与Bootloader

- LWIP

对于教程,我主要参考的是正点原子编写的《达芬奇之FPGA开发指南》与《达芬奇之Microblaze开发指南》。个人觉得正点原子的教程比较新,也足够简明易懂。不过由于教程通常都是一个模块一讲,一个模块建立一个工程,这样线性学下来我觉得是挺枯燥的,而且知识点也是割裂的。我认为可以速览数个简单的章节,将各个模块融合进自己的一个完整的工程中,效果更好。

那么,第一篇笔记就到这里了。

原理图好像不全,没有USB下载部分电路。