精密电路硬件设计指南

🐟发现网上几乎没有paper/doc总结精密测量技术的注意事项的,但在做项目时又经常用到,所以我打算结合多方收集的资料总结一下写篇文。如果有什么遗漏或错误还请批评指出~

1-精密在哪?

微弱信号的处理、测量、采集电路就是最常见的精密电路,比如uVpp级的信号调理。但大信号就与Precision无关了吗?Nope。比如10.000000V的电压基准源系统(基准佬就是喜欢数0~),这也在精密的范畴内。

说到底,我们对于精密的定义取决于我们的需求,对于数模转换系统来说,4位半和6位半的设计考量是截然不同的。在24H恒温恒湿的计量实验室中运行的设备与在恶劣工业环境中运行的设备的设计考量又是一番天地。。。fish大致总结了需要考虑的问题种类如下:

- 热电势影响(Seebeck效应)

- 环境温度影响(温漂、热迟滞)

- 环境湿度影响(器件封装吸潮导致的封装应力变化)

- 环境电磁噪声影响(EMI,共模干扰)

- PCB影响(机械应力、电介质极化)

- 器件封装方式影响

- 工作环境影响

- 元器件品质

- 等等…

本篇就不讲器件选型了,🐟打算把这些内容扔到另一篇单独的文章中。

我们先来看最烧的。

2-热电势—塞贝克效应

Seebeck effect(塞贝克效应) 是指:当2个结点的温度不同时,由至少2种不同导体组成的材料结点(异质结)中会产生热电势,并因此产生回路电流。

其实我们对这种效应并不陌生,它就是热电偶(ThermalCouple)的原理。但如果在精密测量场景中,我们当然不希望这种效应出现。

2.1-常用异质金属结的热电动势表格

Jim Williams在 Minimizing thermocouples maintains 20-bit DAC precision 这篇AN中附上了常见的异质金属结接触热电势表格,此数据出自Keithley的低电平测量手册。热电势的单位为uV/°C,表示温度每变化1°C,接触结上产生的热电势变化量。

可以看到,接触热电势最低的是 铜-铜 接触,其次是铜-银、铜-金、铜-锡等。然而…如果铜一不小心氧化了,那铜-氧化铜的热电势可就要起飞了…(>1000uV/°C),所以请注意保养你的爱机\^_\^。

2.2-连接器注意事项

Jim Williams同样在 Minimizing thermocouples maintains 20-bit DAC precision 这篇AN中附上了测量到的连接器接触热电势水平,可以看到,连接器组合中,热电势最低的是 低热电势香蕉头/座连接器,达到了0.07uV/°C的水平。其次是铜端子和铜香蕉座压接的结构,也有不错的热电势表现(0.08uV/°C)。

当然,实际的连接器千差万别,同一个外形也有不同材料制作而成的。比如某宝上最常见的便宜香蕉插头/插座都不是纯铜制成的,更常见的反而是镀金。也会有专用的低热电势香蕉座,不过会比较贵,比如最常见的碲铜合金材质接线柱,一般都是大几十一颗。

所以,玩精密是很烧钱的一件事(悲

2.3-PCB设计注意事项

除了连接器考量,PCB设计中也需要考虑到积热带来的影响。

2.3.1-精密电路的layout

通常,我们的PCB在运行过程中总是会发热的,除非你是超导,不存在任何热损耗…

热量在IC和元器件中积累,通过管脚、封装和流动空气传导到PCB上,逐渐扩散开,最终会使PCB的热量分布达到一个微妙的平衡态(当然如果PCB敞着放那当我没说orz),这时PCB上不同部位的温度可能会存在差异,比如电源芯片可能是最烫的,而远处的低功耗传感器可能是最凉快的。

而我们的元器件要焊接到PCB上,必然需要使用焊料来完成(锡、铅、银等合金),那么器件管脚、焊料和PCB的Trace(铜)之间就形成了数个异质金属结,就会产生热电势。

如果这时候,精密运放的输入电阻两端存在温度差,那么电阻2端的热电势之和就会不相等,导致运放的输入失调性能恶化!

图源:ADA4522 数据手册

为了减小热电势造成的Vos不匹配问题,我们可能需要做如下处理:

- 尽可能将输入电阻/关键器件规则排布,使其受到加热源的影响均匀相等(比如同一个朝向、并排摆放,并与OPAMP中间轴对称,这样可以保证R1和R2受到OPAMP发热的影响近乎相同)

- 增加"无用"元件,平衡2个输入端的异质金属结数量,使得产生的热电势 数量级相等。(比如增加0欧或其他不影响电路功能的电阻),同时也要注意器件布局

- 尽量让高发热的器件远离敏感电路(很好理解,从源头解决问题;D)

- 尽可能在PCB内层使用完整地平面/电源平面,这样可以让PCB发热更均匀地分布在PCB上,从而减小局部温度差

下图来自OPAx189数据手册,我只取了个layout当作例子

2.3.2-精密电路的对外连接

PCB内的连接说完了,再来看PCB对外连接。

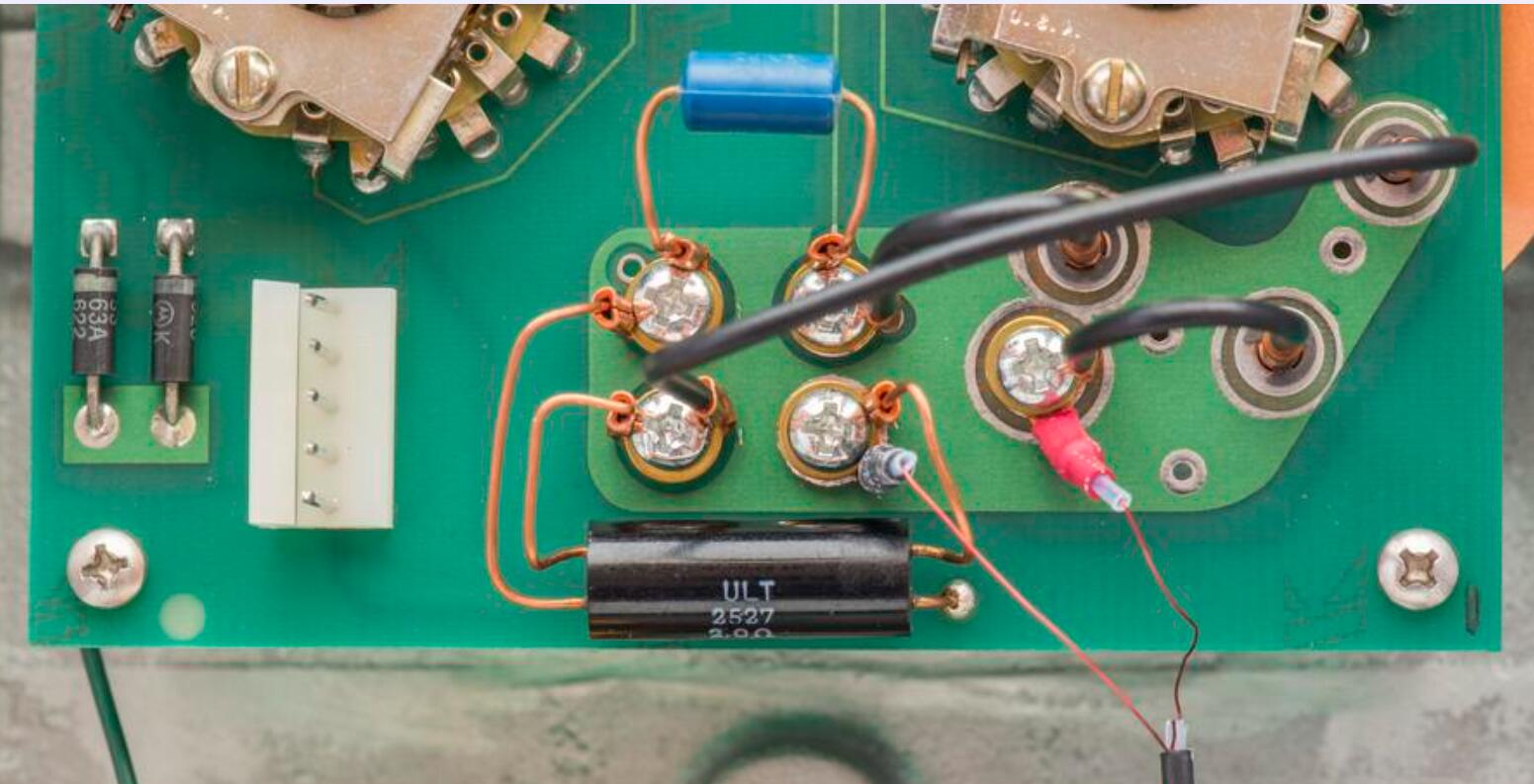

在精密分压器、基准源/校准器等仪器中,低热电势连接同样至关重要,uV级别的误差也会导致仪器指标降级。xdev拆解的 Keithley 262 low thermal divider 中就有着这种连接范例。

Keithley 262是一个精密分压器,分压最高比例为10^5:1,意味着在此档位下给仪器输入一个10V的信号,将输出一个100uV的信号,且在此档位下的噪声是1nVpp,热电势漂移典型值3nV,温度系数10ppm/°C,即10uV/°C。

其内部的输入输出连接器(从接线柱到PCB)均使用 铜-铜压力接触 连接,而不是我们以往经常见到的焊料焊接,或是插拔式连接器连接。

看完了最烧的,再来看第二烧的。

3-温漂与热迟滞

任何电子器件都做不到绝对稳定,多数情况下,最显著的影响源就是工作温度。

3.1-温漂(Temperature Drift)

器件在工作时消耗能量从而发热,热量积累致使器件温度升高,于是导致整个电路的工作点在缓慢或剧烈地移动。如果对大功率器件的散热处理不当,片子就真的烧了orz

由于人类的科技水平做不到水滴那种程度,你无法把所有分子、原子都钉死,分子热运动效应始终存在,所以任何器件都有温漂,只是程度的大小不同而已。

3.1.1-气流(Air Flow)

将精密电路PCB暴露在空气中工作,和密封在机壳中工作,其指标是完全不一样的。

虽然在室内我们很难察觉到空气的流动变化,但空气流动始终存在,且会对精密电路产生影响。比如精密电压基准IC如果暴露在空气中,气流流过它时会导致其温度产生变化(即使如LTZ1000、LM399这类自带加热的Reference也会短暂变化),由于基准输出电压存在温漂,那么其输出就会变化,导致仪器读数跳动。

有一种说法是,气流扰动引起的电压变化也可以视作极低频率的1/f电压噪声

同理,精密运算放大器也怕这样的工况。有时候屏蔽罩的作用不仅仅是电磁屏蔽,也具有防止气流流动引入的干扰的作用~

所以我们最好还是将精密电路小心地包装起来,让他享受一个相对安静的工作环境吧>﹏<

3.1.2-低成本控温方法

最简单的控温方法就是被动式。如果电路整体的发热规律且可控,可以直接将整块PCB塞到金属壳体中密封起来工作,依靠其工作自发热达到热量均衡态。

当然,这样你可能会等很久,俗称"烤机"(#滑稽

3.1.3-高成本控温方法

高成本一些的控温方法就是主动制热/制冷了,根据需求,你可以将温度敏感的PCB或器件单独密封,然后使用陶瓷加热片、半导体制冷片等器件去控制密封环境的温度。当然,你可能还需要一个PID控制器用来精确控制温度…

典型的应用比如:

- 天文冷冻CCD相机

- 高精度万用表的恒温室(放置基准、前端等敏感器件)

3.2-迟滞(Hysteresis)

顾名思义,迟滞描述了器件的"呆滞程度"。比如给一颗电压基准IC上电小时,再断电1小时,然后再上电待其稳定,你会发现它的输出电压可能与第一次上电时的电压有着微弱的区别,这就是迟滞造成的。

3.2.1-迟滞产生的机理

先来欣赏一下ADI最新的顶级基准IC——ADR1001吧;D

图源eevblog大佬: ADR1001 – Ovenized Voltage Reference System

将IC开盖,得到die的装配图如下:

这颗IC是将die(裸芯片)通过特殊导电胶粘接到金属基板上(不过这个看着像陶瓷基板,内部涂敷金属层?),然后用金属丝(看这个颜色像是铝丝?)将die上的pad引出连接到封装的引脚上,最后盖上金属顶盖制成的。一般我们所看到的黑块块IC(比如SOP8、QFN封装等)是用绝缘塑料填充封装而成的。

在芯片经受冷-热循环的过程中,由于材料的热胀冷缩形变,以及金属原子的扩散效应,导致die和连接线、封装体的机械结构、电气结构发生微弱变化,这些变化的积累体现为芯片内部应力分布的改变,最终致使工作点漂移,从而产生迟滞效应。

Cadence网站上的一篇blog:What Causes Thermal Hysteresis in a Voltage Reference? 对此有详细的解释:

Thermal hysteresis is created by mechanical stress that accumulates on the semiconductor die during temperature cycling. The stress distribution and how stress is released from the device depends on whether the die was previously at a higher or lower temperature, and the past history of stress in the device. Stress accumulates and sets in at different locations on the die due to thermal expansion and contraction.

3.2.2-迟滞的测量

迟滞的严格测试需要经过多次温度冲击循环:

- 将器件焊接到PCB上,然后在85°C环境中烘烤半小时,保证一批器件有相同的初始状态/条件

- 将待测器件扔到温控环境中,控制温度到-40°C、25°C、85°C进行循环,每次改变温度等待30分钟,测量器件输出电压

- 重复第二步多次,得到热迟滞曲线

在Linear Technology的 Design Note 229-Don’t Be Fooled by Voltage Reference Long-Term Drift and Hysteresis 中,提到了上述基准IC热迟滞测量流程,同时还diss了一下当时的竞争对手ADI…(第三个XX780为AD780,ADI的基准IC)

ADI:既然你这么骂了…看来不得不花钱让你闭嘴了呢(

于是2017年,ADI以148亿美元收购Linear Technology…

关于热迟滞测量,可以参考MAXIMUM的这篇文章: How to Measure the MAX6079 Voltage Reference Thermal Hysteresis, Considerations for PCB Layout(现在也是ADI哒!)

3.2.3-如何改善迟滞效应?

迟滞效应是不可消除的,只能尽可能通过良好的设计和测试去尽量减小它带来的影响。

MAXIMUM上面那篇文章提出了几个设计建议:

- 将敏感器件(基准IC)放置在PCB的短边边缘上,或者角落里,因为这些地方的PCB刚性最好。如果放在PCB中间或者长边上,很容易受到PCB弯折的影响从而导致封装应力变化。

- 一定要清理干净封装底部残留的助焊剂和焊料残渣,因为这些残留物会使封装底部压力不均匀,从而导致封装应力变化

- 尽量使用小面积、厚一些的PCB去安装敏感器件,薄而大的PCB更容易弯折。

- 可以在敏感器件周围开槽来创造局部刚性区域,最大程度减小应力对封装的影响

比如🐟的18位精密电压源所使用的LTC6655基准电压源IC,就放置在PCB的中间,在四边开了槽来减小应力影响,同时起到了隔热的作用。

3.2.4-带恒温控制的精密基准电压源器件

参考Fluke的文档 A practical approach to maintaining DC reference standards,电压基准器件在使用时经过上电-下电的循环过程中会积累热迟滞,导致输出电压发生变化,那么如何维持基准器件的精度呢?

- 给基准一直通电,保持恒温运行

这一点很好理解,很多高精度DMM基本是不断电运行的。

- 在断电一段时间再上电后,给基准的温控来一个调制信号,让基准经历一定规律的温度冲击循环,消除器件积累的热迟滞。

如果基准器件/仪器要经过长途运输,运输过程中可能不能保证一直供电,那么必然会经历掉电-再上电的过程,这时就可以用这个技术来消除积累的热迟滞影响。

Fluke说这是他们的专利技术,🐟也没玩过不知道实际效果如何。。毕竟能测出热迟滞的设备价值不菲。

4-环境湿度

🐟从小生活在长江边,上大学来到西安的第一个感觉是——好干啊!

不过干燥对电子元器件和芯片来说是一件好事,但也有不好的地方(更容易积累电荷,有ESD风险)。一般消费类电子产品对环境湿度的要求不是那么的敏感,但精密电路就是敏感肌,太干受不了,太湿也不行。

4.1-电阻器吸潮

以精密电阻举例,生产商在测试时会进行指定湿度工况下的稳定性测试,比如开步睿思PTFR系列精密贴片电阻的"双85"(85°C、相对空气湿度85%)测试图如下:

在测试2000小时后,可以看到右边电阻阻值发生了最大约300-400ppm的变化。

在设计电路时,通常要根据电路结构评估器件漂移带来的影响,然后选择对应等级的元件。如果你没有考虑到这一点,那就是个坑咯#狗头

4.2-IC吸潮

申请过TI/ADI样片的同学肯定知道,随着样片送来的还有包装盒中的干燥剂,以及一张湿度指示卡。IC为什么要这样包装呢?

参考ADI的 Assembly Considerations for Analog Devices mModule® BGA and LGA Packages,其中指出了ADI的uModule产品满足 IPC/JEDEC J-STD-020标准中的 MSL3/MSL4 湿度敏感度(Moisture Sensitivity Level)标准。

如果你在收到uModule后拆包发现,里面的湿度指示卡上粉色很亮眼,那么必须将这批芯片在125°C环境中至少烘烤48小时来烘干IC封装吸收的水分,不然这批芯片直接过回流焊会裂开(物理)。

4.2.1-MSL标准

MSL标准等级表示,IC暴露在非干燥环境中的最长时间。如果超过了这个时间,那么在过回流焊之前必须烘烤IC。

- MSL 6 – 使用之前必须烘烤

- MSL 5A – 24 hours

- MSL 5 – 48 hours

- MSL 4 – 72 hours

- MSL 3 – 168 hours

- MSL 2A – 4 weeks

- MSL 2 – 1 year

- MSL 1 – 不怕湿,随便造(bushi

4.2.2-吸潮失效的机理

第一点是因为塑料封装吸潮后体积会发生变化,导致芯片die上的应力发生变化,这会影响基准电压源等精密IC的精度。

第二点则更为常见和致命,IC封装材料吸潮膨胀,此时直接将其高温加热(过回流焊)极有可能会导致封装破裂。图源:Why do components require low humidity storage?

4.2.3-IC封装/PCB吸潮

LTC6655 的数据手册中也提到了封装湿度敏感度带来的迟滞变化影响,塑料封装的LTC6655受影响,而LS8(MCC)封装的LTC6655则不受影响,因为MCC封装的LTC6655是全密封的,湿气无法进入封装内部造成应力变化。那么代价是什么呢?成本罢了——

同时,PCB材料本身也是对湿度敏感的,PCB基板吸潮后其应力分布也会发生变化(很好理解,材料吸潮后通常会变软)

尽管湿度带来的影响非常可观,但通过合理的PCB设计可以减轻这些误差源。比如6655手册中推荐的3面拉环开槽设计:

🐟用了4面开槽孤岛设计,图在前面~

4.3-管脚硫化

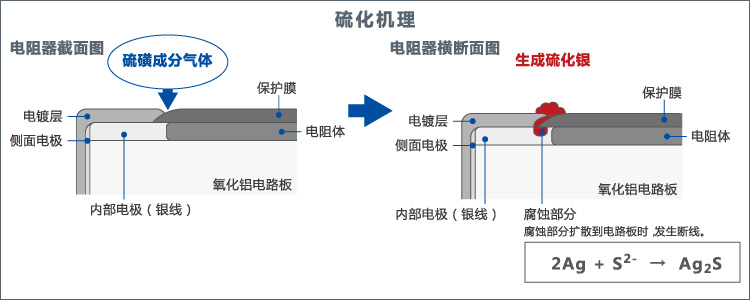

参考罗姆的电阻器基本知识介绍—— 电阻器的硫化

空气中存在着各种形式的硫化物成分,比如汽车尾气和温泉的硫磺气体等。这种硫化成分吸附在金属表面,慢慢地和金属发生反应。

厚膜贴片电阻器的内部电极采用了银 (Ag),如果有硫化成分气体从保护膜和电镀层之间的缝隙侵入,就会发生如下图所示的反应,慢慢地生成硫化银 (Ag2S)。最终会引起电阻器内部电极断线,电阻将失效。

我们就把这种现象称为硫化引起的断线。

在汽车电子等要求高可靠性的设计中,抗硫化电阻器是必不可少的。柱状MELF晶圆电阻器是抗硫化设计的常见选择,同时各大厂商也有生产抗硫化的贴片电阻,原理是在电阻的电极中混入高浓度的钯(Pd),来抵抗硫化,也可以使用金作为内部电极。

5-电磁兼容

电磁兼容(ElectroMagnetic Compliance)是指 器件、设备或系统 在电磁环境下保持良好性能,且不会向该环境中的任何器件、设备或系统引入大量电磁干扰的能力。简单来说就是:你不干扰我,我也不干扰你。

而精密电路最怕的就是 被干扰!(简直就是我本人)电磁兼容是一个非常大的坑,许多大公司有工程师专门负责EMC整改,我在这里也不陈列太多,只讲如何做好防范。

同时,给出一些参考资料,供对EMC测试与整改有兴趣的读者参阅:

- Texas Instruments – EMI Considerations for DC to DC Converters and Integrated Switching Regulators

- Texas Instruments – Fundamentals of EMI Requirements for an Isolated DC/DC Converter

- Texas Instruments – An overview of radiated EMI specifications for power supplies

5.1-电磁兼容2大问题

电磁兼容的核心是 干扰源 和 干扰传播路径,一图胜千言:

精密电路中一般不会包含很强大的电磁干扰源,我们只需要考虑别的电路/环境带给我们的干扰即可。

简单来说,我们无法彻底干掉噪声源,只能做好自我防护:找到传播路径,并针对性地去抑制/切断他。

5.2-最常见的干扰源——开关电源

每个电路都有电源。如果精密电路的供电采用了开关电源,那么就要小心勒。

首先做一个大致的频段摸底:我的精密电路所处理的信号频段在何处,与开关电源的开关频率/EMI辐射频段有没有重合呢?

比如我们的工作频段在DC-10kHz,而开关电源的工作频段在600kHz,那么有个好消息是开关电源所带来的干扰还算比较好处理,因为他远比信号频段高,所以可以用电源线滤波器轻松干掉。比如铁氧体磁珠、馈通电容(FeedThrough)滤波器等是电源设计中常见的降噪滤波器。

如果我们的工作频段在通信系统的中频频段(比如10MHz-40MHz),那么此时要格外注意开关电源所带来的影响了,因为开关纹波及其高频谐波成分与信号频段重合,会直接影响到电路的杂散性能。

5.2.1-电源线滤波器与LDO的使用

下图是村田的静噪滤波器产品线,针对不同的频段、功率,有不同的产品可以对应选择。

在村田的SimSurfing-设计辅助工具中,可以查看这些滤波器的传输特性(S21),下图是NFM21PC225三端子馈通电容滤波器的S21曲线图,可以看到其对高频段有非常好的抑制效果。用这种滤波器来滤除电源轨上的高频段噪声(10MHz-GHz)再好不过了。不过使用时需要注意其耐压(6.3V)和额定电流(4A)。

murata还提供了非常丰富的教程和应用示例,比如这些:

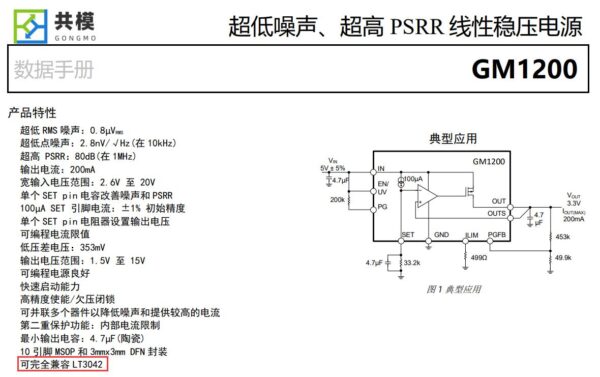

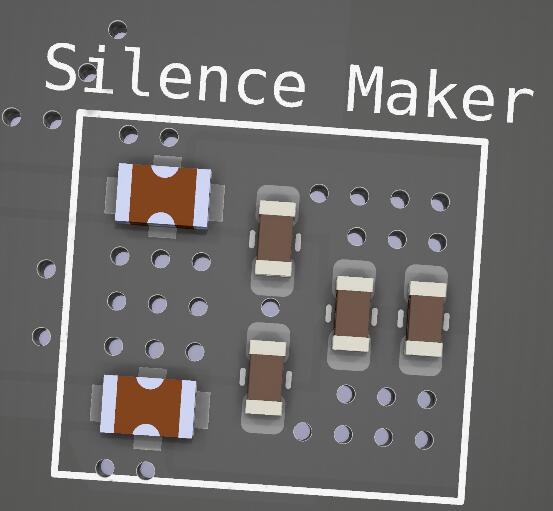

在工程应用中,通常使用高PSRR、低噪声LDO来配合这些滤波器完成对开关电源输出后级的稳压和滤波、降噪处理。比如这是🐟在最近的工程中使用的馈通电容滤波器(串联在正负电源LDO输出 和精密低噪声放大器电路供电之间),用以降低开关电源的高频传导噪声。(有4个脚的就是馈通电容滤波器)

而且🐟在很早的一篇文章,精密低噪声电源设计 中也讲解了DCDC后级滤波器(Post Filter)和LDO的使用~,这里就不展开了。

5.2-屏蔽措施

开关电源的输出纹波对电路带来的影响不仅仅在PCB走线上体现。EMI测试时,拿着接收天线对着待测电路接收,便能在频谱接收机上显示出惊人的高频噪声成分!此时测试的即是电路的辐射噪声。

如何应对辐射噪声呢?可以从EMC的2个方向入手:

- 从辐射源角度出发:谨慎选择电路结构、高EMI元件(电感),以及合理PCB Layout

- 从传播路径出发:切断/抑制传播路径,增加屏蔽结构

如何减小DC-DC的对外辐射呢?这又是个大坑哈哈哈哈,我就把这个议题留给电源专家DualMono同学了#狗头

我来讲讲如何做好屏蔽。

5.2.1-对敏感电路使用金属屏蔽罩

此节参考Murata的空间传导及其应对措施-静噪基础教程8-10节。(很棒的资料,推荐学习)

空间噪声传导的主要机制如下:

- 静电感应

- 电磁感应

- 无线电波的发射&接收(电磁波传导)

如果要屏蔽来自空间传导的噪声和干扰,就需要使用屏蔽罩。一般使用金属等良导体(或导磁体)完全覆盖/包裹目标电路/元件,屏蔽罩既可以用在噪声发射源,也可以用在被保护的敏感电路那一侧。只要不是环境极端恶劣(比如通信基站,大功率电机附近),用一层薄薄的金属也能在MHz频段内取得很好的屏蔽效果。

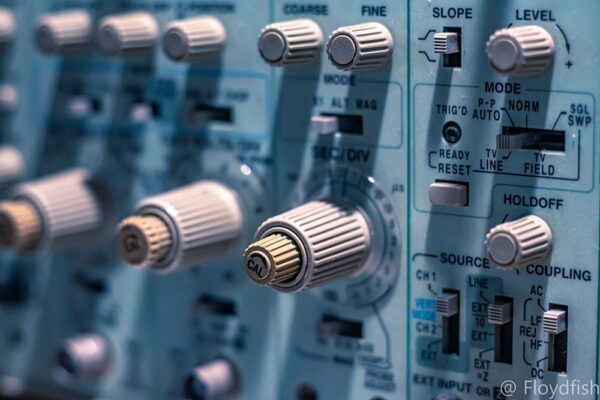

Keithley 2015 6位半数字万用表中,AC RMS测量电路被一块有些厚度的金属屏蔽罩挡板盖住,阻挡来自电源变压器的电磁干扰。

还有很多精密电路中常见的夹扣+屏蔽罩组合,完全覆盖部分敏感电路。

5.2.1.1-选择不同的屏蔽材料

由电磁场与电磁波的知识(损耗介质中平面波的传播)可以得知,良导体对外界电磁波主要有2个效果:

- 反射部分电磁波

- 吸收部分电磁波,以热能的形式损耗

如果吸收损耗未耗尽电磁波的能量,剩下的还是会进入到屏蔽罩内。

描述金属良导体对电磁波损耗的一个关键指标是趋肤深度(又称穿透深度)\delta,衰减常数 \alpha 是趋肤深度的倒数。

\delta={1 \over \alpha} = {1\over \sqrt{\pi f\mu \sigma} }其中,f是电磁波频率,\mu 是金属材料的相对磁导率,\sigma是金属材料的电导率。同等条件下,趋肤深度越小,说明电磁波越难以穿透材料,屏蔽效果越好。

不同材料的趋肤深度 vs 频率对比

数据来源-电磁场与电磁波-David K. Cheng 第二版

| 材料 | \sigma(S/m) |

f=60Hz | f=1MHz | f=1GHz |

|---|---|---|---|---|

| 银 | 6.17*10^7 | 8.27(mm) | 64(um) | 20(um) |

| 铜 | 5.80*10^7 | 8.53(mm) | 66(um) | 21(um) |

| 金 | 4.10*10^7 | 10.14(mm) | 79(um) | 25(um) |

| 铝 | 3.54*10^7 | 10.92(mm) | 84(um) | 27(um) |

钢(\mu_r=10^3) |

1.00*10^7 | 0.65(mm) | 5(um) | 1.6(um) |

| 海水 | 4 | 32(m) | 0.25(m) | 不适用 |

请注意,这表格里的公式渲染似乎有问题,电导率符号是\sigma,而不是表格顶部的\Sigma

从上表可以看出,对于MHz以上的高频干扰,使用铜、铝等良导体是经济实惠且效果好的选择。但如果干扰频率下降到kHz级别,这些良导体可能需要厚一些才能有效屏蔽。对于极低频的电磁干扰(比如工频),这些非磁导体材料的作用微乎其微。这时高磁导率的金属材料比如铁、钢、坡莫合金(Mu-Metal)将会是极佳的选择。在应用严苛的环境中,通常会采用多层混合屏蔽措施。

btw,铁/钢似乎是万金油,不过🐟在tb上见到的屏蔽壳多数都是洋白铜材质,不知道是什么成分。🐟还用磁铁试了下手里的几台老仪器外壳,多少都带些磁导性。

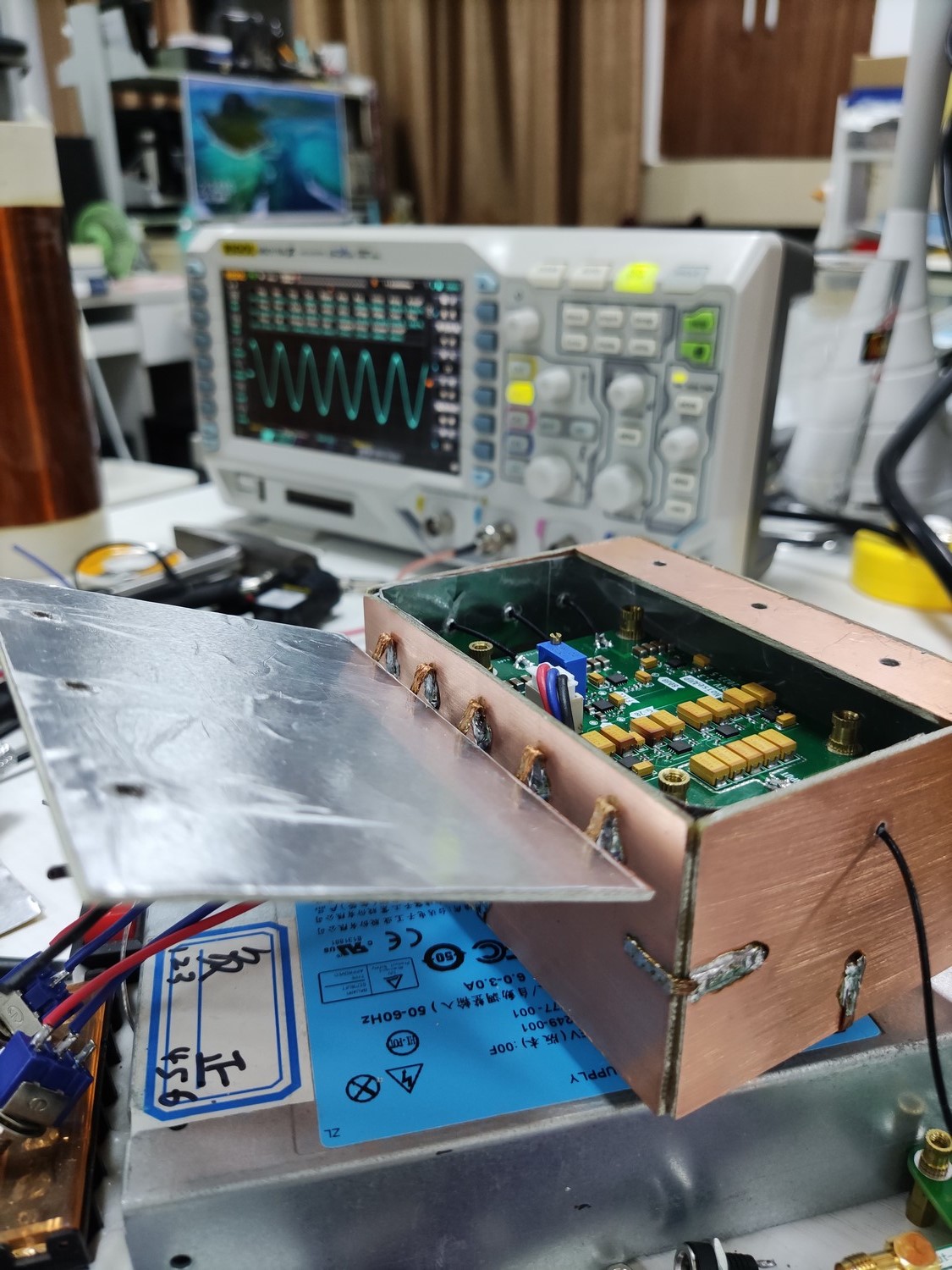

Floydfish的噪声放大器V2.1版本中,使用了铁壳-覆铜板-坡莫合金贴膜的三层屏蔽结构。此图中未展示最外层铁壳

5.2.2-屏蔽外壳的构建

全封闭的外壳自然是最好的,但这一般很难做到,因为仪器仪表的外壳总是需要开孔,来放键盘、屏幕、对外连接器、电源插座等等。但开孔也不是想怎么开就怎么开的…

在外壳上开孔时,主要需要注意的是孔/缝的物理尺寸是否与某些信号的波长对应,即使开了一个宽1mm,但是长50mm的缝,波长为100mm(对应空气中频率3GHz)附近的电磁波就可以愉快地进出屏蔽罩勒。

如果真的需要开大量的孔洞(比如用于散热的进出风口),可以用许多小孔组成的阵列来代替单一一个大孔,相当于把一块大蛋糕切成114514份(雾,这样能保证屏蔽的完整性。

同样的,壳子总需要打开,你看坦克也需要给人员进出留个顶盖不是)

通常使用螺丝和壳体上/内的螺孔来连接外壳,使其构成完整的屏蔽结构。murata的建议是,一定要确保螺丝的导电性,使用导电垫圈等配件可以让螺丝与外壳良好密封连接,保证屏蔽效果。

即使拧上了螺丝,但由于金属外壳的不平整,在边缘难免还是会有缝隙存在(如果是um级加工精度铣出来的壳子那当我没说…),这时需要通过设计螺丝孔位来保证屏蔽完整性。越密集的螺丝越能减小缝隙的宽度。所以看到很多微波模块的屏蔽壳上密密麻麻的螺丝也就不难理解了。

比如Mini-Circuits的LZY-22X+高功率射频放大器,工作频段0.1-200MHz,其外壳设计如下:

目测螺丝间距27mm左右,对应空气中频率约5.6GHz的信号(1/2波长),远高于此module的工作频段。

5.2.3-屏蔽线缆

如果在不同仪器或设备间传输敏感信号,为了保证信号不被干扰,屏蔽线缆可能是多数EE脑海中第一个蹦出来的选择。

当然还有别的选择,比如把单端信号转为差分传输以抑制共模干扰、将电压信号转换为不易受干扰的电流信号传输,或者直接将信号数字化后传输数字信号,这些都是工程中常见的设计。

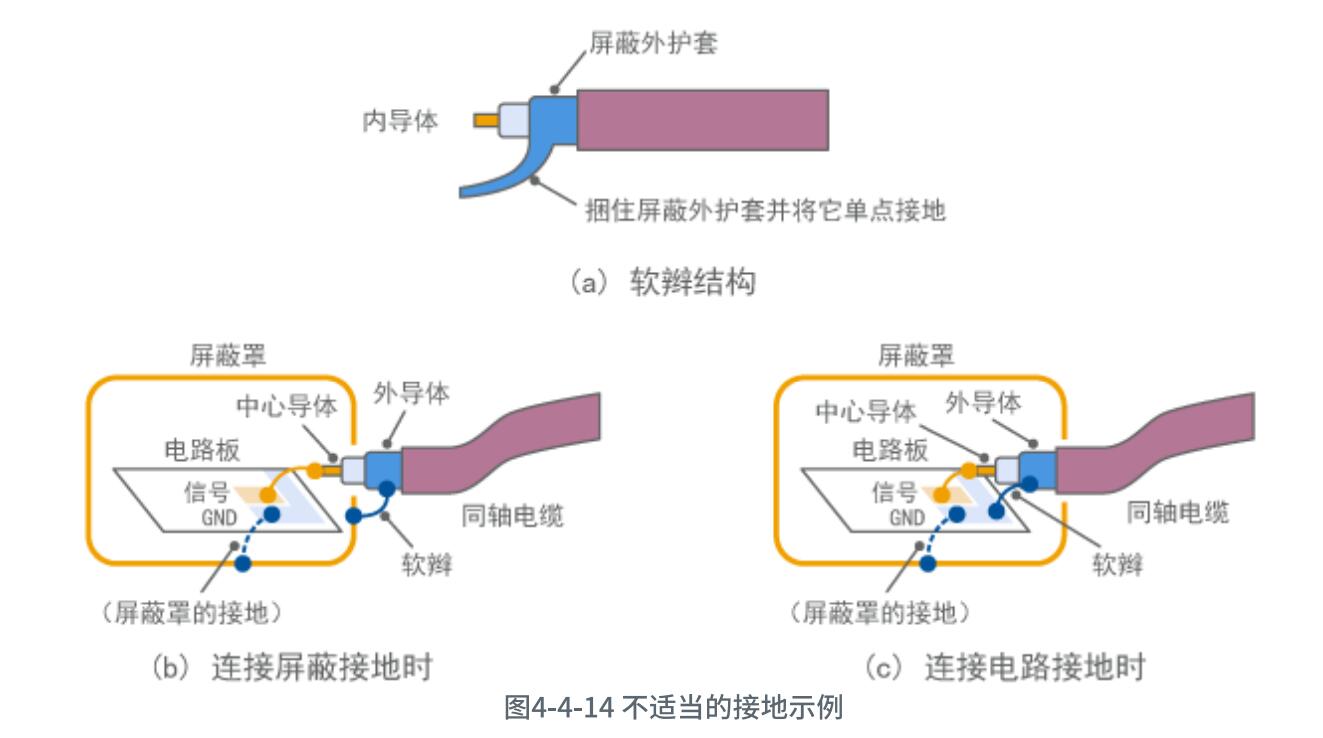

在使用屏蔽线缆-连接器时,同样存在很多问题,比如一个设备接了地,另一个则是floating的,屏蔽层应该怎么连接?如果两侧设备都接地了,这时又该怎么连接?下图展示了屏蔽线缆如何连接到屏蔽罩/外壳

为了获得完整的屏蔽,同轴线缆+连接器的整个圆周都必须与屏蔽罩良好接触连接。

如果2个屏蔽罩都单独接地了(通过电源线),这样连接可能会产生接地回路,不满足单点接地原则,反而可能会增加信号链中的噪声。

此时,断开一端的接地(让一端悬浮)就可以解决这个问题,但这样会增加ESD损坏的风险,是个需要权衡的问题。

同时,屏蔽罩与PCB上的电路地线也是必须相连的,否则无法形成有效屏蔽。此时同轴线缆+连接器+外壳+PCB的示意图如下:

如果不使用同轴连接器,直接将线缆伸出去/进来会怎样?

比如将同轴线剥开,屏蔽层绕到一起,形成一个辫子一样的形状(绕成一坨),然后直接焊接到PCB/屏蔽壳上

答案是negative。这样会使屏蔽罩效果大打折扣。但如果非要这样用的话,也可以通过一些措施改善屏蔽效果:

- 在PCB上使用同轴连接器,同时在同轴线缆接到PCB上的地方使用最短距离连接,将PCB的地与屏蔽罩相连,这样可以让屏蔽性能恶化的没那么严重。如果由于单点接地的设计策略导致不能这样做,可以用一个小电容连接

- 在输入线缆处装一个馈通电容来滤波,阻挡噪声进出设备。(如果走的是差分信号,换用共模扼流圈/滤波器)

5.2.4-同轴线坏了

一般来说,线缆的可靠程度和售价成正比…但如果使用不当,可能造成线缆损坏。比如被刀刮了,烙铁烫了/风枪吹了…

圆周方向的裂缝影响更大,纵向的裂缝影响相对较小,可以勉强凑合用。但无论是横向还是圆周向的裂纹,都会导致线缆的屏蔽效果受损。

如果屏蔽线缆的外层护套破裂,露出了屏蔽层,那就尽量换一条用吧~

更详细的屏蔽与降噪措施请参考上面提到的Murata的教学文档。🐟在官方群文件上传了一份整理好的文档压缩包,可自行搜索下载。

6-PCB设计与生产相关

完成了设计蓝图后,最重要的当然是实现——

在实现的过程中,也存在许多工程问题,对于我们敏感的精密电路来说,需要认真对待呢- –

6.1-精密运放的layout

对于高速数字信号和射频信号来说,我们对走线的特征阻抗有着明确的要求,比如单端50欧,差分90欧、100欧等等。在确定PCB层叠结构、介质、铜厚等参数的情况下,很容易计算出相应的阻抗线线宽和间距等参数。

如果是analog呢?其实无所谓(bushi

因为具体到不同的应用场景,layout的注意事项不尽相同。有时候需要在一堆指标中选出你最在意的一项,针对该指标去做对应的layout。

- 寄生电容(Stray Capacitance)

对于高带宽运放来说,如果希望输入走线的寄生电容较低,那么可以使用细走线连接,来减小走线和地平面之间的寄生电容。虽然略微增加导线内阻,但运放的高输入阻抗特性可以让其忽略不计。(不过导线拉太长的话,此电阻可能跟运放输入电容形成一个影响可观的极点,需要注意布局)

- 失调(Offset)

以及我们之前提到的,为了维持零漂移运放的直流失调性能,需要根据seebeck效应考虑器件和走线的热布局。

- 漏电流(Leackage)

对于微电流测量场景,需要为输入线设计Guard Ring来消除PCB基板上的漏电流影响。Guard Ring既可以是阻焊开窗的密闭走线环,也可以直接在走线两旁开机械槽,物理隔绝漏电流路径。详情请参考🐟之前的文章:Counting Electrons-飞安级静电计前端

不过通常情况下,可以参考运放datasheet中给出的layout example,并且参考他给出的layout considerations。比如这是INA333的layout example

不知道你注意到没有,这板子像是实习生画的…他的输入输出线都没跟焊盘中心对齐。(这是怎么过了review放上数据手册的啊喂!)

虽然画的有点别扭,但器件的布局和引线的走向还算可以参考的。。

另外,也可以参考他们画好的Eval Board,比如这是ADI的仪表放大器通用测试评估板:

好像也并不存在针对某一器件的layout技术。只要掌握了设计的思路(为什么要这样做),相信什么电路也难不倒你)

6.2-应力消除

前面我们提到过,针对精密基准源芯片,我们需要采用切割拉环设计来减小各种应力对其的影响。其实对于精密运放、精密电阻电容等器件,应力消除也是十分必要的。

对于IC来说,无论是什么类型的IC,其封装的形式都大同小异。塑料封装的IC难免受到PCB机械应力、环境湿度与温度循环的影响而发生漂移。如果是金属密封封装的IC,可靠性当然会更高,不过代价是成本+++。

精密电阻同样对应力非常敏感。贴在PCB表面的SMT器件会因PCB弯折、收缩/膨胀,在管脚2端产生机械应力,导致阻值发生变化。而且设备在运输过程中(或者本身就工作在极端环境(比如汽车)中的设备),可能遭受高加速度的冲击,同样会导致PCB机械应力波动。直插的立式电阻,管脚如果紧贴PCB同样会受到机械应力的影响,导致阻值发生漂移。

有几个针对此的对策:

- 合理设计优化焊盘和走线形状,合理布局这些器件,必要的话在旁边开槽降低机械应力

- 对于直插器件,可以适当弯折引脚后组装到PCB上,这样弯折的管脚对于机械冲击具有一定的缓冲作用(比如下图中,Keithley 2015中一颗弯折管脚的精密直插电阻)

- 换用更高可靠性的器件(耐冲击,抗造),得加钱。

6.3-大 清 洗

PCB刷好锡膏,贴上器件后,进回流焊炉子加热焊接,这样的PCB就可以直接使用了吗?当然不。

锡膏/焊锡丝中都含有一定比例的助焊剂成分,这些助焊剂在加热后只有部分化为魔法烟雾飘走了,剩下一坨还是会留在PCB上,形成一滩烂泥( 倘若不给PCB来个彻底的清洗,这些助焊剂残留物会让电路性能大打折扣。🐟见过的大部分EE爱好者焊完PCB后,会拿棉签/球蘸取洗板水,将看得见的助焊剂残留擦去。但这样程度的清洗是远远不够的——

不信的话你可以手焊一个SOIC-8的芯片,然后拿洗板水擦一擦周围,然后热风枪把芯片吹下来,看看屁股底下藏了多少助焊剂…

6.3.1-漏电

这些残留的助焊剂会形成漏电路径(因为其属于有机化合物和金属盐混合物,绝缘阻抗远比不上PCB基板),漏电一旦开始就是要命的。比如你发现:我买的0.05%精度的精密电阻,焊到板子上精度只有0.5%了!

这是当然…而且这颗电阻的阻值还会随着施加的信号幅度大小而变化(不同电压对应的漏电流大小不同呢),放在运算放大器中使用,这颗放大器的线性度和精度都白瞎了。。。

同时,运算放大器也因为残留助焊剂形成漏电路径,输入失调电流也远不如手册标的预期值。输入失调电流一起飞,作用到输入端接的电阻上,输入失调电压也寄了。不好好洗板子的最终结果就是性能的全面降级!!

6.3.2-还是应力

嗯?助焊剂跟应力有关系?当然有。

虽然肉眼看不到(其实也能观察到了…),残留的助焊剂很有可能并不是均匀分布在PCB上/芯片底部的。这会导致芯片看着像是紧贴着板子,实际则是被坑坑洼洼的助焊剂顶起来了。PCB开始工作后,这些助焊剂一受热又开始膨胀,软化,重新分布,芯片封装受到的应力又变了。。。

真是令人绝望的循环啊.jpg

6.3.3-怎么洗白白?

不知道工业产线用的什么,🐟个人用的是超声波清洗机+洗板水的组合(ADI的某篇Application Note也推荐)。感觉一般的工厂清洗PCBA也是用这套。

超声波清洗机真是个好东西,不过用它洗板子也需要注意一下,不要直接把PCB扔进去触底清洗,不然洗5分钟后你会发现芯片脚都给震断了。

一般超声波清洗机会附送一个避震笼子,将它架在机器内部,把板子放到笼子里洗,就ok啦。

6.3.4-什么?不能洗?

当然,强而有力的超声波清洗也会对器件产生很重的压。

🐟记得是Vishay还是谁的一篇Application Note提到,精密电阻焊到板子上之后最好不要用超声波清洗了,因为这样会改变电阻内的应力分布,使其阻值产生偏差。

不过🐟个人认为,用了避震笼子应该能减小这种影响…好像也没有一个很严谨的验证方式呢)

如果为了保险起见,可以改变器件的组装顺序。将最敏感的器件在其他器件组装、焊接、清洗之后进行二次焊接,然后用洗板水冲刷清洗,或许能避免这种现象。

7-尾声闲话

本文就到此为止结束了,关于器件选型这块以后有机会在讲了。。

又是一篇摸了很久的长文。最近🐟的产量也不是很好,得撒点金坷垃了(bushi。主要是因为之前挖了太多坑,此时想填有种无从下手的感觉。同时现在又面对着生存的难题,让人很难静下心来好好做事。这次更完一篇文章后,也想说说闲话解解闷了。(苦笑

从2019年走来,马上Emoe就要到第五个年头了,当时大家提出这个idea时,谁也没想到能走这么久这么远。Emoe一路走来,受到了许多社会各界的朋友和群友的帮助和赞赏,也很高兴有人能加入Emoe创作者的行列中,与我们一起发癫发电。非常感谢,没有你们就没有Emoe的今天呐~

🐟也再次感受到了运营一个组织的压力。虽然Emoe是一个纯兴趣个人组织,不存在盈利也没有KPI一说,平日里服务器的运维也不怎么需要操心,只需要管理好群,维护Github,定期写文章,做宣传就好。但总是会下意识地思考今后,思考Emoe做的好与不好的点,思考怎样才能做的更好。

在无所事事的这半年里,🐟也一直在做着和以前一样的事,挖坑填坑。虽然看起来很忙碌,但仔细一想又像是无所事事,一事无成,还时不时陷入焦虑循环进入停摆状态。虽然我觉得这样的生活倒也不错罢了)

真正意义上的完美并不存在,虽知晓了这点,脑中却仍然放不松这根紧绷的弦。有群聊这一载体后,写文章 似乎显得不那么重要了?毕竟有技术问题在群里问问,就能得到响应式的回答。不过倘若Emoe以后3个月才更新一篇文章,6个月,甚至成为年更,我个人内心是难以接受的。我还是想在这不起眼的互联网角落里留下些什么。可能是创作欲和理想主义作祟吧(雾

按你胃,以后还会有更多的技术文章出炉的。不过如果受特殊情况影响,产量可能会下降。这点还请谅解。

参考与引用

- Minimizing thermocouples maintains 20-bit DAC precision

- Watch Out for Those Thermoelectric Voltages! – Fluke Cal (提示,此链接将直接下载pdf)

- ADA4522 Datasheet

- OPA189 Datasheet

- Keithley 262 low thermal divider overhaul

- ADR1001 – Ovenized Voltage Reference System

- What Causes Thermal Hysteresis in a Voltage Reference?

- Don’t Be Fooled by Voltage Reference Long-Term Drift and Hysteresis

- How to Measure the MAX6079 Voltage Reference Thermal Hysteresis, Considerations for PCB Layout

- A practical approach to maintaining DC reference standards

- 电阻器的硫化

- JEDEC J-STD-020E

- Why do components require low humidity storage?

- LTC6655 datasheet

- Skin effect -Wikipedia

- 空间传导及其应对措施-静噪基础教程

- 电磁场与电磁波-David K. Cheng 第二版(何业军 桂良启 译)-清华大学出版社

- LZY-22X+

![[Bonjour STM32] No.3-单片机抽象编程思想小议(附状态机建模方法)](https://www.emoe.xyz/wp-content/uploads/2020/05/BonjourSTM32_NO3_04-600x257.png)