本文目录

噪声放大器(Noise Amplifier)进阶指南

在上一篇文章,噪声放大器(Noise Amplifier)构建指南 中,我们分析了几种Linear Technology公司的工程师设计的噪声放大器电路和架构,并动手制作了属于我们自己的Noise Amplifier。

但是由于作者写作当时的资源(RMB)和时间精力有限(当时还在同时忙毕设),没能将NoiseAmp的设计细节考虑周全。现在🐟有了相对较长的时间和还说得过去的资源,可以在这个课题上Step Further了。同时,我为这一代的噪声放大器取名叫:EmoeNAP(NoiseAmPlifier)。

Take a "NAP" and enjoy a moment of silence!

让我们进一步踏入微弱信号测量的神秘领域吧——

微弱信号处理

一般而言的微弱信号处理包含检测、测量、处理等几个方面,比如模拟量传感器的微弱电流转换放大、微弱射频信号的接收、放大、检波等。而在噪声放大器设计中,我们所做的是最简单的,也就是单纯的放大,但是具体到我们的目标,却又是十分困难的,因为我们已经在使用常规手段去逼近所能处理的极限了——接近热噪声水平的噪声信号放大。

NAP处理的信号类型

我们做这个噪声放大器用来测什么?

- 电阻热噪声(

乱入) - LDO/线性稳压器/基准电压源输出噪声

- 运算放大器/三极管等半导体模拟器件输出噪声

- 超低噪声的模块/系统级电路输出噪声测试

- 各类电池输出噪声

- 其他

以上这些信号,有白噪声信号(热噪声等),也有周期性信号(如开关电源纹波等)。有单频/窄带信号,也有宽带信号。有低阻抗信号源也可能有高阻抗信号源。想要制作一个能够同时兼顾这些信号类型的放大器,意味着它必须具有 平坦的通带内响应、极高的放大器输入阻抗、极高(可选)的放大倍数、极低的输入噪声、可选的通带范围、可调的增益档位 等近乎苛刻的要求。

NAP技术指标细化

🐟工作了2个多月,学到了很多项目管理的方法论。我们来定义一下NAP的详细技术指标吧~

在给出输入特性和输出特性、电气特性前,我们需要先设计好系统的顶层框图。由于NAP是一个相对简单的小系统,预计只包含2块PCB,所以画的十分简单:

- 输入特性:

- 输入交流耦合,RC高通输入构成0.5Hz的高通滤波器

- 输入耦合电容使用16V耐压680uF的钽电容组,所以输入电压峰值小于15Vpp

- 680uF钽电容组后通过499Ω电阻接地,构成截止频率0.5Hz的RC高通滤波器,所以交流输入阻抗为499Ω(不考虑后级放大器的情况下)

- 输出特性:

- 输出同样交流耦合,通过70uF电容组和499R电阻构成截止频率5Hz的高通滤波器

- RC高通滤波器由运算放大器串联一小隔离电阻后直接驱动,所以输出交流阻抗约等于该隔离电阻+输出级的输出阻抗

- 输出幅度取决于运算放大器的输出范围,被限定在约±4.2V内(2s锂电池满电电压)

- 频率特性:

- NAP分有3个输出口,分别输出宽带(10Hz-宽带)、10Hz-1MHz、10Hz-100kHz的3个频带内被放大后的噪声信号

- NAP在通带内的交流电压增益为10000倍(80dB)/500倍(54dB),通过一个增益切换开关切换

- 输入噪声性能:

输入运放采用OPA2211/OPA1612多单元并联,通过统计平均这一手段降低互不相干的各运放自身的输入噪声。并联N个单元的相同结构运放,输入噪声将降低至原来的1 \over \sqrt{N} 倍

- OPA2211在1kHz的输入噪声为

1.1nV/\sqrt {Hz},并联8单元的OPA2211运放,运放的输入噪声降低2.828倍,即389pV/\sqrt{Hz}

当然,实际电路的输入噪声比这个要大一些,需要根据电路的放大结构来计算最终的噪声水平。

前级低噪放电路分析

关于运算放大器的噪声分析问题,🐟在上一篇文章,噪声放大器(Noise Amplifier)构建指南 的运算放大器噪声分析一节中提了一嘴,同样的,在前不久刚发布的文章 运算放大器噪声分析 中我们还专门探讨了这个问题。这次让我们动点真格的:D

同相还是反相?

🐟用TI的Spice软件 Tina 搭建了OPA2211的仿真电路图,先来看反相。

理论上来说,相同的增益时反相放大器的输出噪声将优于同相。

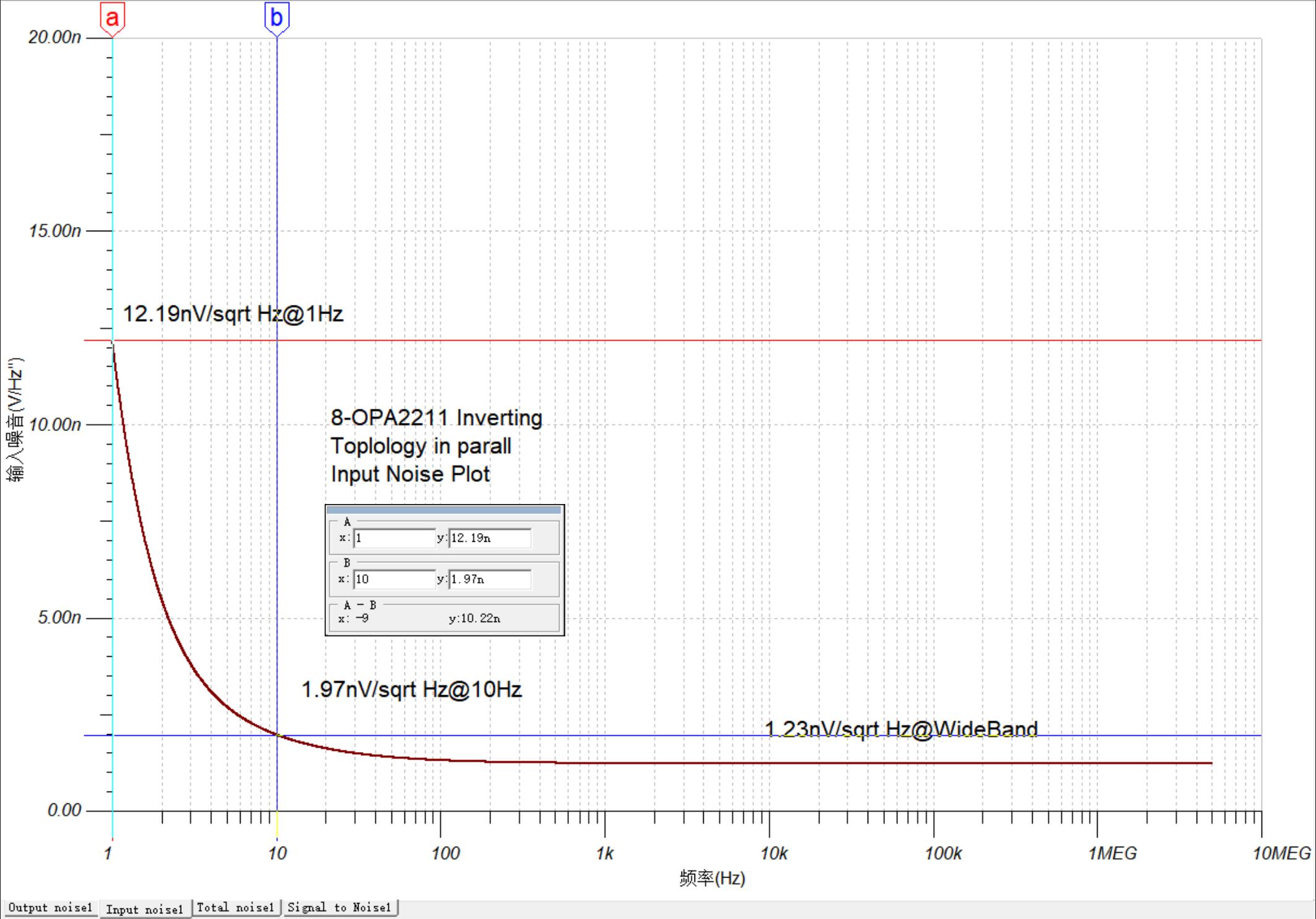

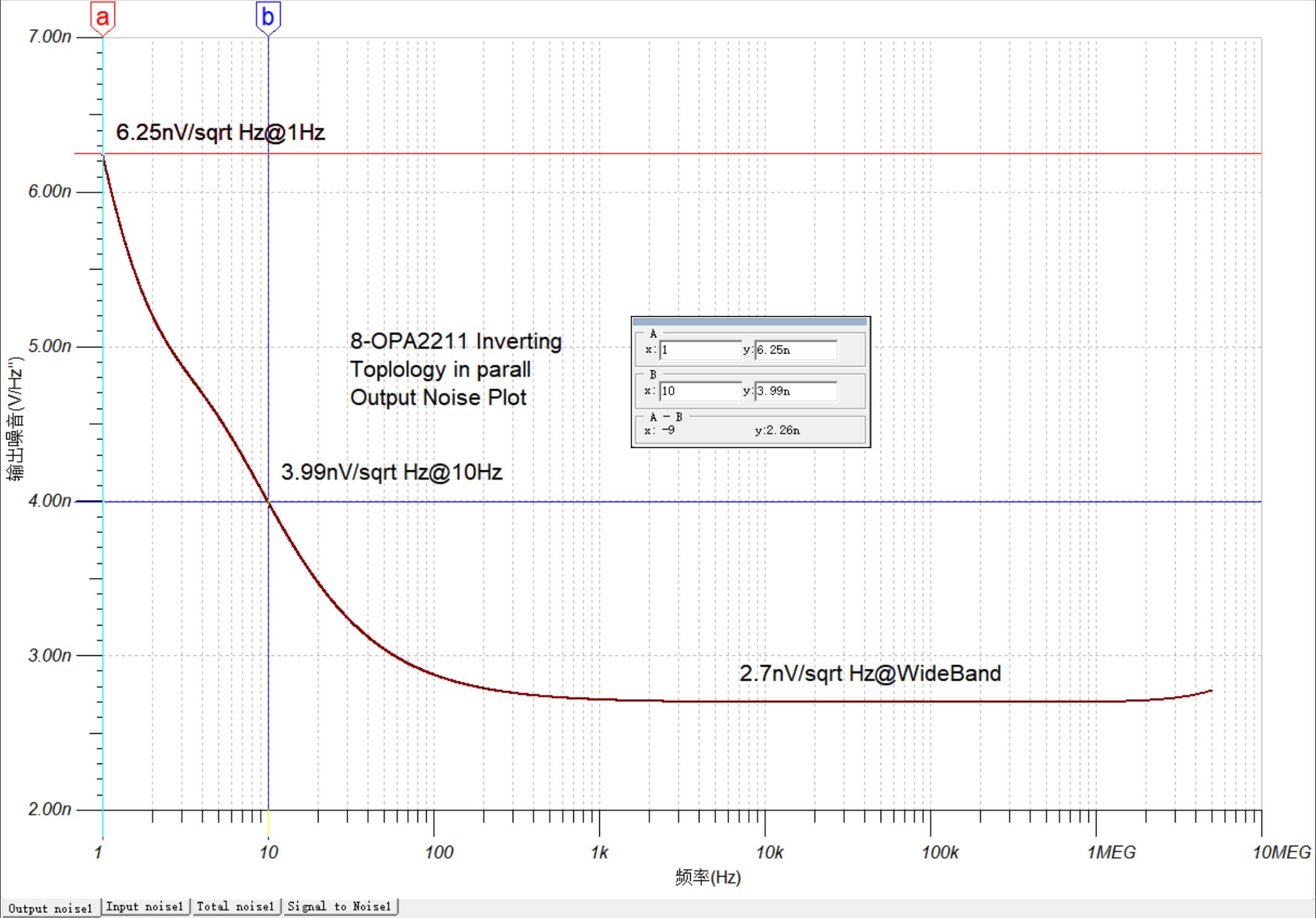

先将信号源阻抗设置为50欧,然后执行噪声分析,扫描从1Hz-5MHz频段内的噪声功率谱密度,得到如下曲线:

输入噪声

输出噪声

发现问题了吗?运放的输入噪声怎么会比没并联前的输入噪声还要大呢?

其实答案很简单,因为信号源的50欧姆源阻抗也为系统贡献了噪声输入,所以这个“高阻”源降低了系统的噪声性能。输入噪声都增大了,就别提输出了,必然增大,2.7nV/sqHz跟我们预计的相去甚远。

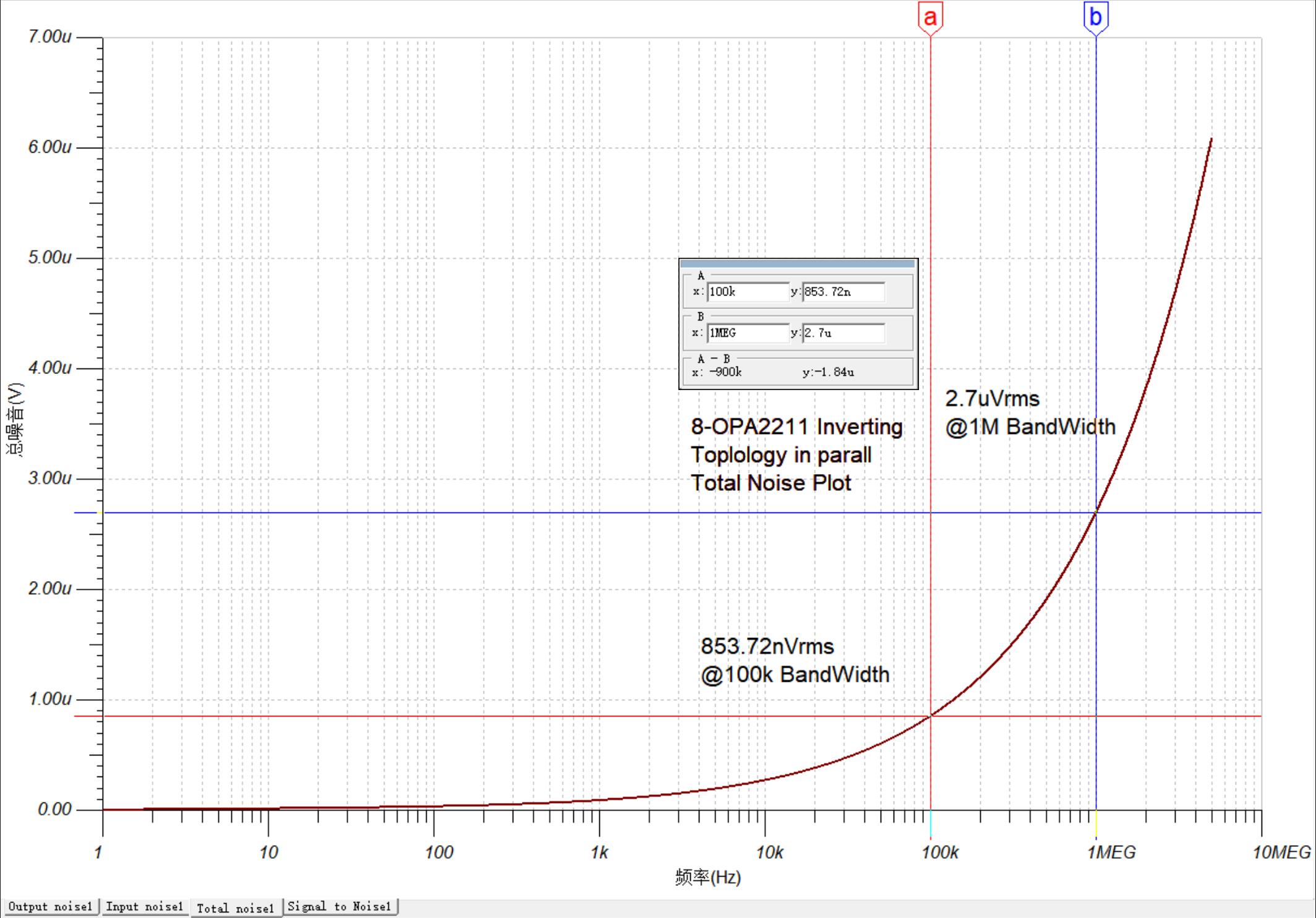

我们来模拟一下最理想的情况,即输入信号源源阻抗为0。再次运行噪声分析,直接查看电路的总输出噪声:

可以看到,在100kHz带宽内该电路总输出噪声是850nVrms。这一级电路增益约为-19.6,我们再乘以500(总共10000),得到最终输出噪声大约在425uVrms左右,折合输入噪声42.5nVrms,是一个十分惊人的数值。

可惜凡事都难完美,不然咱们的设计也太没挑战性了。我们要测量的源阻抗当然不可能是0欧姆。如果是电源,他可能比较低,几十毫欧到几欧姆的数量级,如果是运算放大器之类的有源器件,可就难说了。

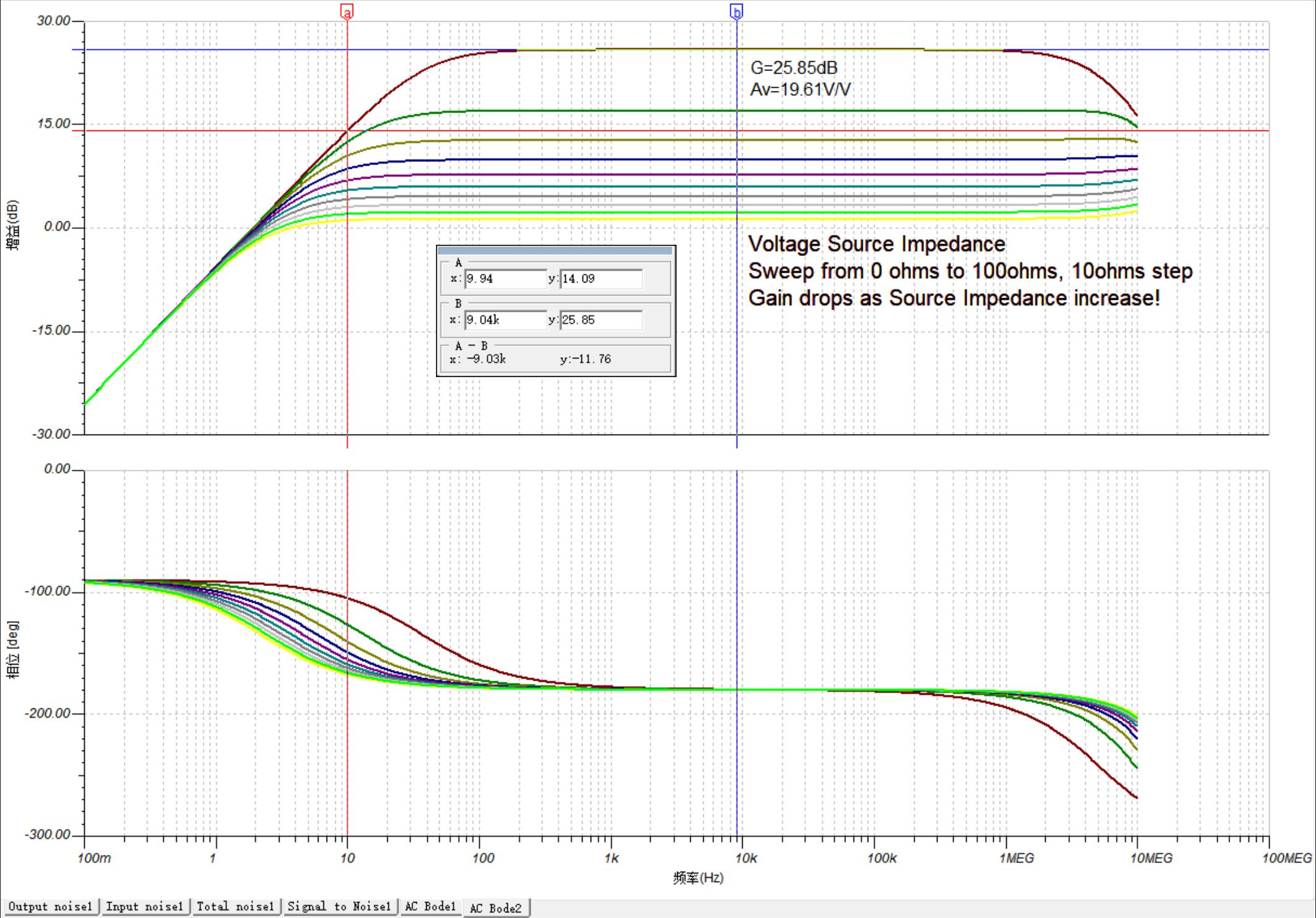

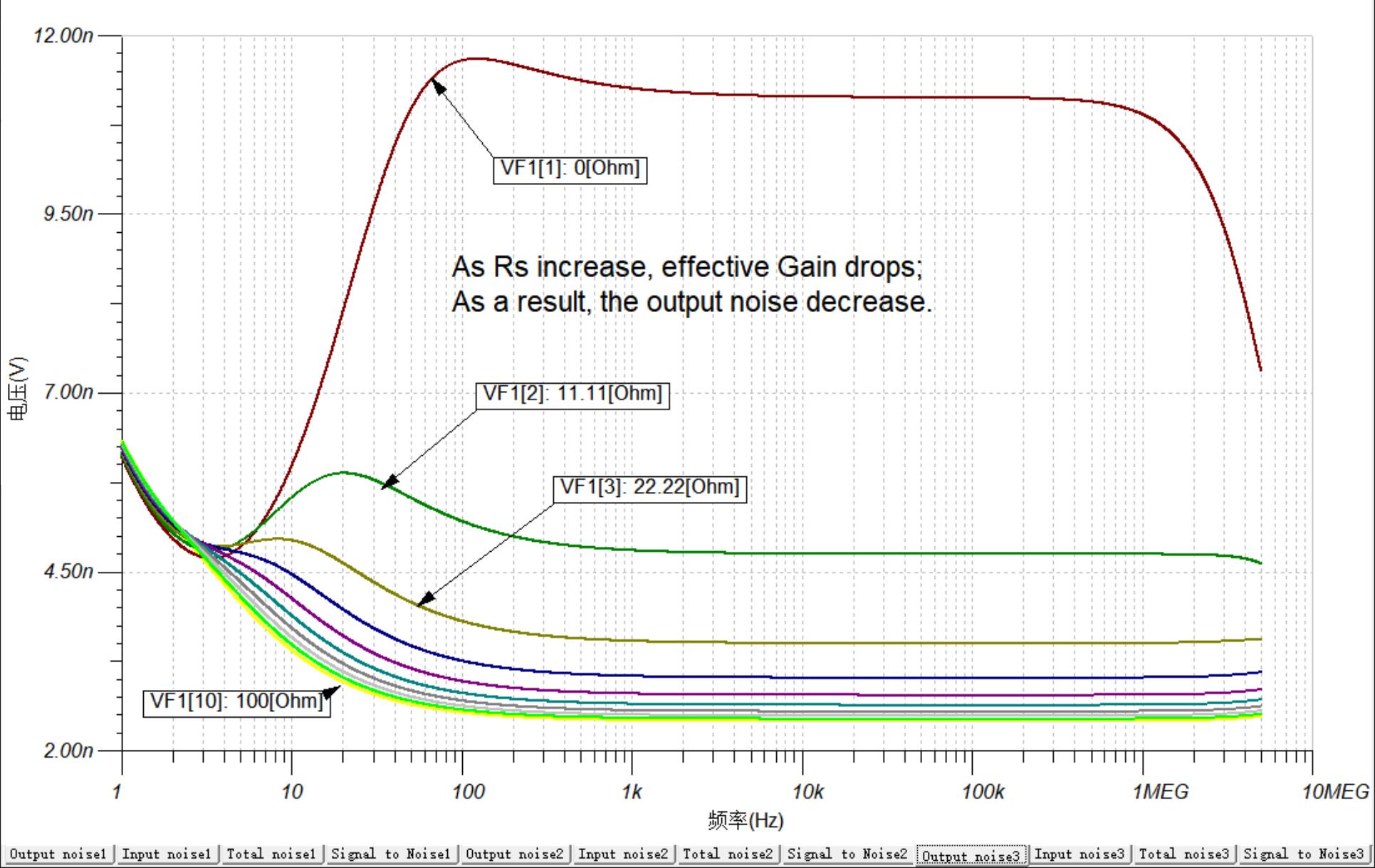

除开源阻抗带来的额外噪声问题以外,反相放大器结构还有一个致命的缺陷——输入阻抗等于输入电阻,这是由于工作在深度负反馈条件下的运算放大器的虚短特性导致的,运算放大器的2个输入端电位都为地电位,信号源的输入电流流入输入电阻直接到地,所以对于单个反相放大器单元来说其输入阻抗是51欧姆,然而这个电路并联了8单元,进一步降低了输入阻抗。我们来仿真一下源阻抗变化导致的增益降级效应:

设置Tina参数分析,选择控制参数为信号源的源阻抗,从0欧姆以10欧为步进扫描至100欧,得出一组增益曲线:

不难看出,只有信号源阻抗为0欧姆的时候,反相放大器才能达到其最初设计时的目标增益。随着源阻抗的上升,整个电路的有效增益迅速降级。源阻抗为100欧姆时,整个电路的增益几乎掉到了0。

这时的噪声也非常有趣。请看下图:

最高的那条曲线是我们仿真的源阻抗为0欧姆时的输出噪声谱密度曲线,可以看到因为电路有较高的增益,输入的噪声也被放大;但随着源阻抗的增加,如果电路的增益保持不变的话,输出噪声也会相应地增加。但是不断攀升的源阻抗所贡献的额外噪声终究是填不满因增益降低所导致的空缺,最终反而导致整个电路的输出噪声不断降低了。

同相放大器,前进四!

同相放大器有一个很妙的地方就在于,它的输入阻抗就是运算放大器同相输入端的输入阻抗,也就是无穷大(理想运放,OPA2211-EP的共模输入阻抗为1GΩ,非常接近理想了)。所以只要源阻抗的数量级不超过输入RC高通滤波器的电阻的1/10(500Ω/10=50Ω),源阻抗的波动变化对电路的增益影响就可以说是在一定范围内可忽略的。

而源阻抗的增加固然会为电路贡献一些额外的输入噪声,但这属于被测器件(DUT,Device Under Test)的固有属性,我们可以将其视作DUT的输出噪声的一部分。所以我们并不需要在意DUT的源阻抗会影响我们测量的精度。

至此我们已经基本确定了同相放大器结构在NAP电路中的正确性。那么我们来仿真验证一下吧。还是先搭一个电路图:

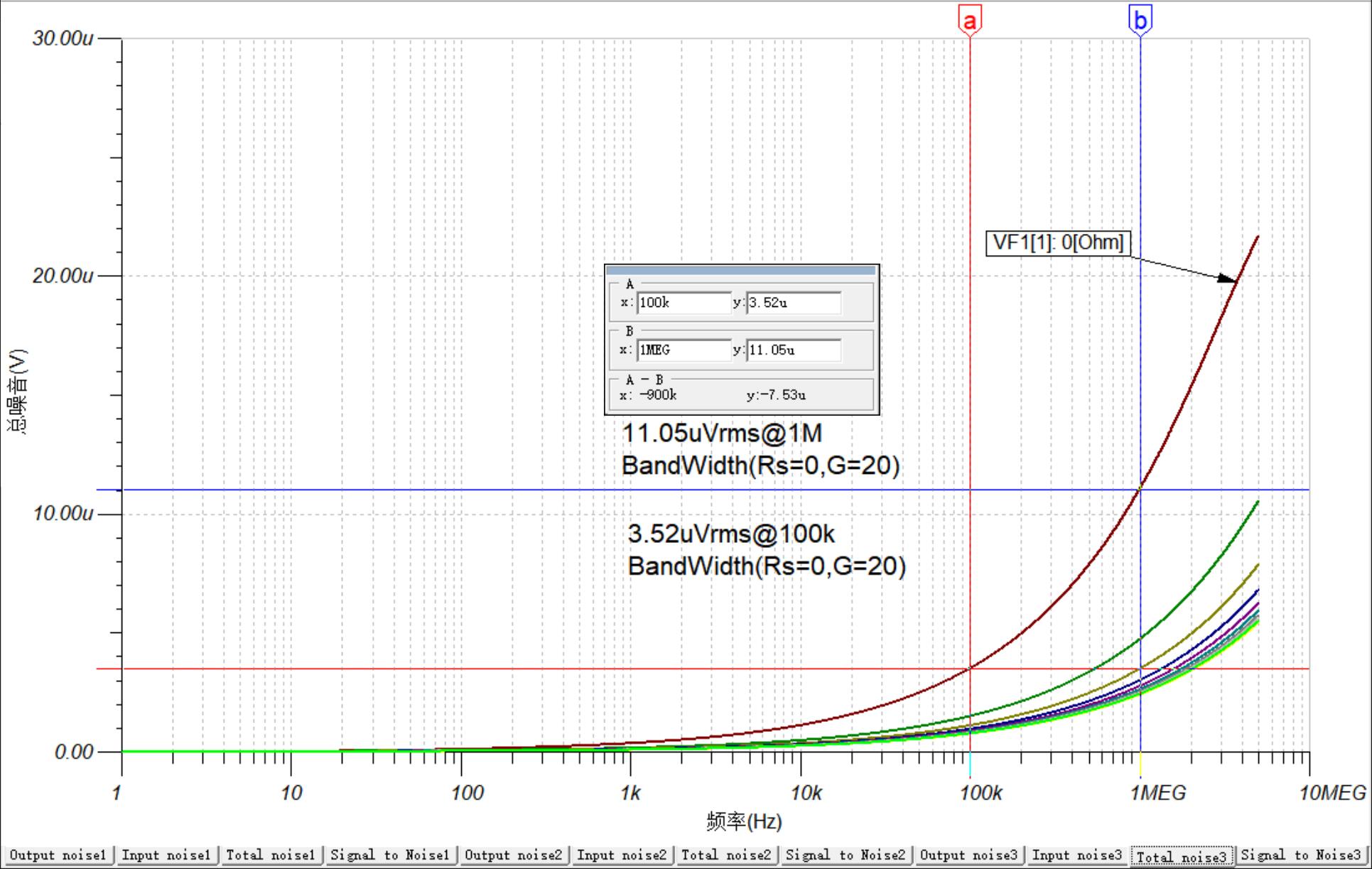

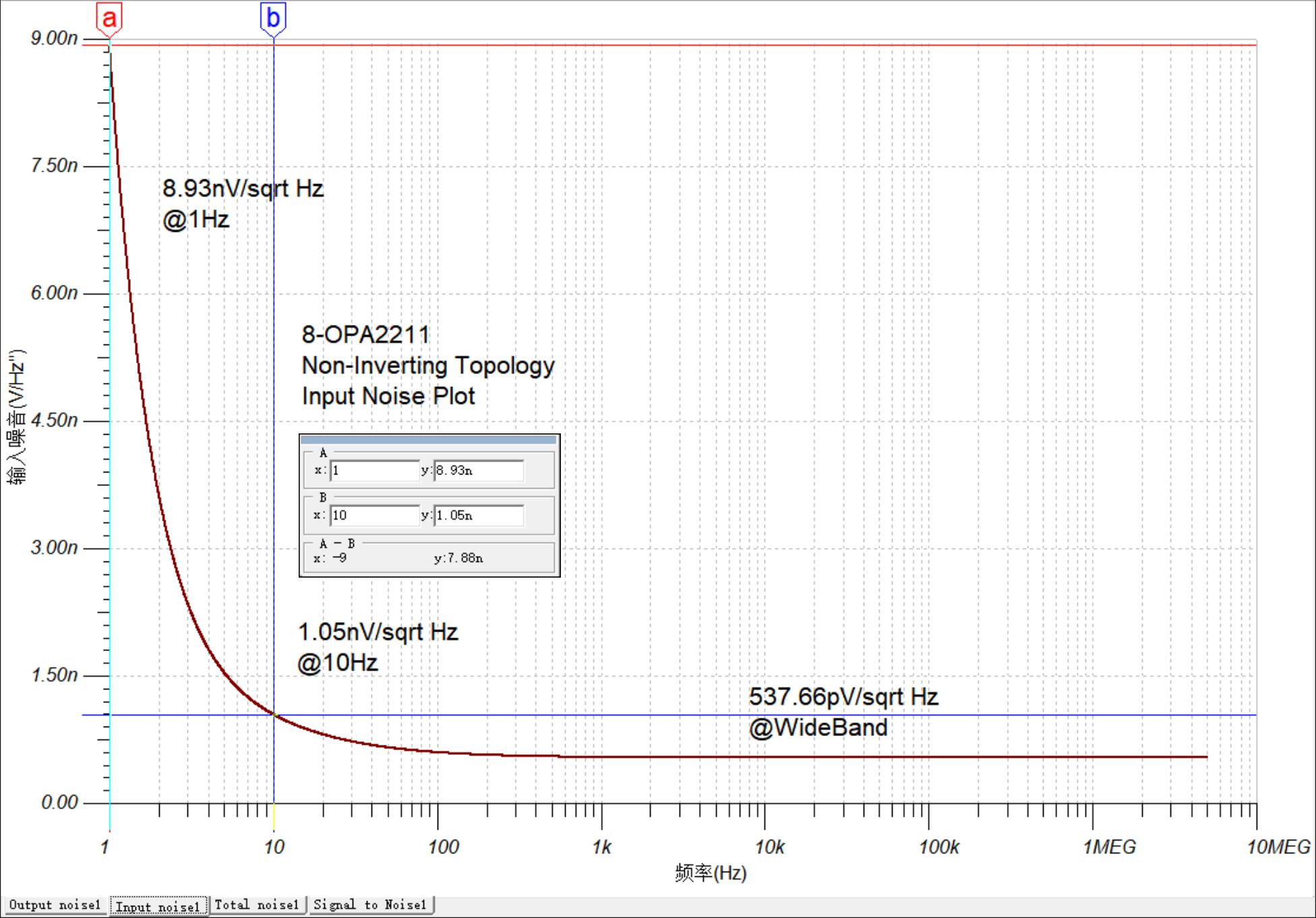

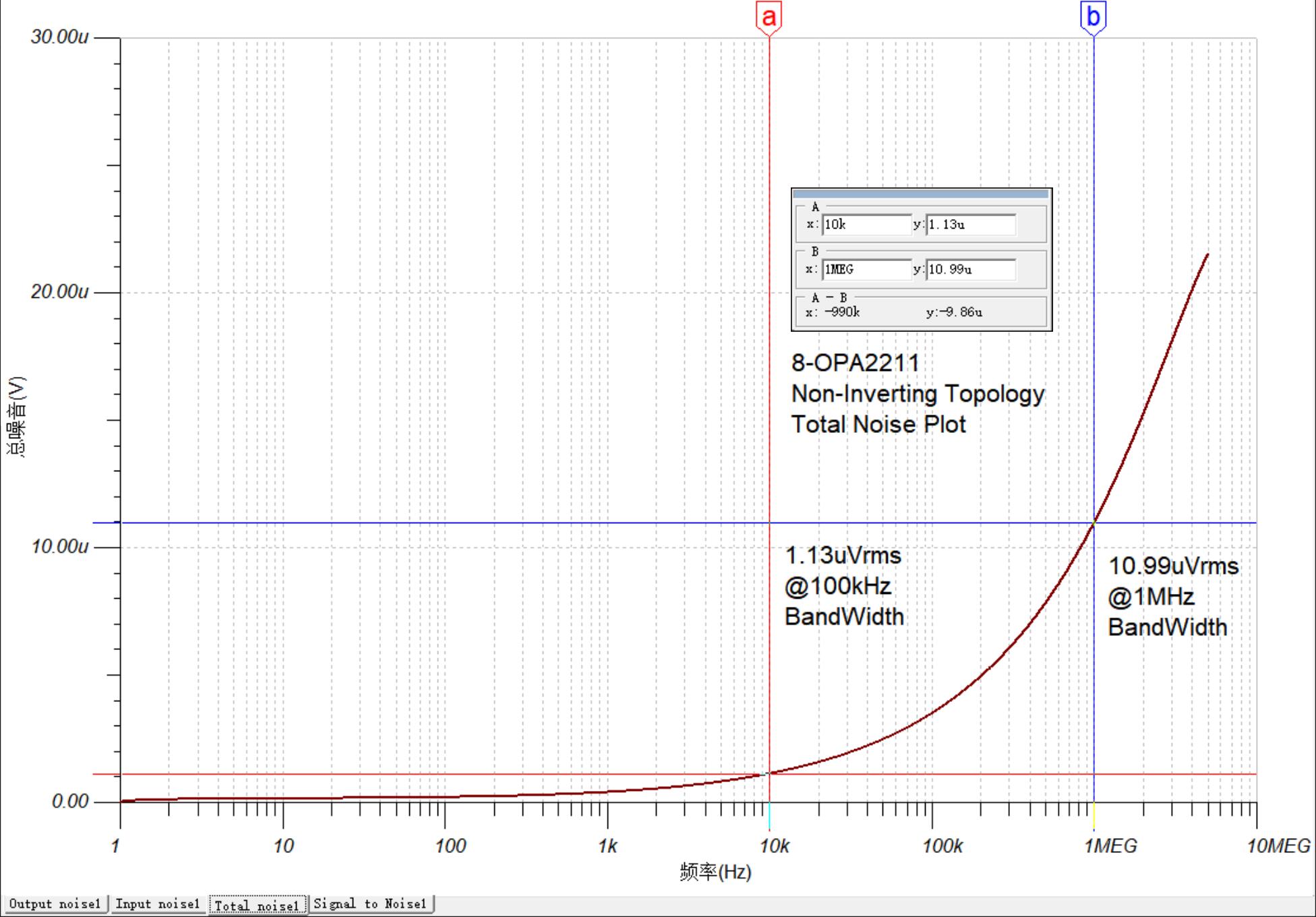

咱们先设置源阻抗为0欧姆,然后plot出输入、输出噪声电压谱密度、以及总输出噪声:

可以看到,正如我们预计的那样,配置为同样增益电阻的同相放大器的噪声性能是不如反相放大器好的。在1Hz频率处的1/f输出电压噪声谱密度竟然达到了166nV/sqHz!好在我们在输出端还有高通滤波器用以对10Hz以下的频段进行抑制。看看同相结构的总输出噪声,在100kHz带宽内输出噪声为1.13uVrms,该增益级增益约为20.6,再乘以500(总共10000),可以得到565uVrms的总输出噪声,折合为输入就是56.5nVrms,虽然不及源阻抗为0时的反相结构的性能,但仍然是非常nb了。

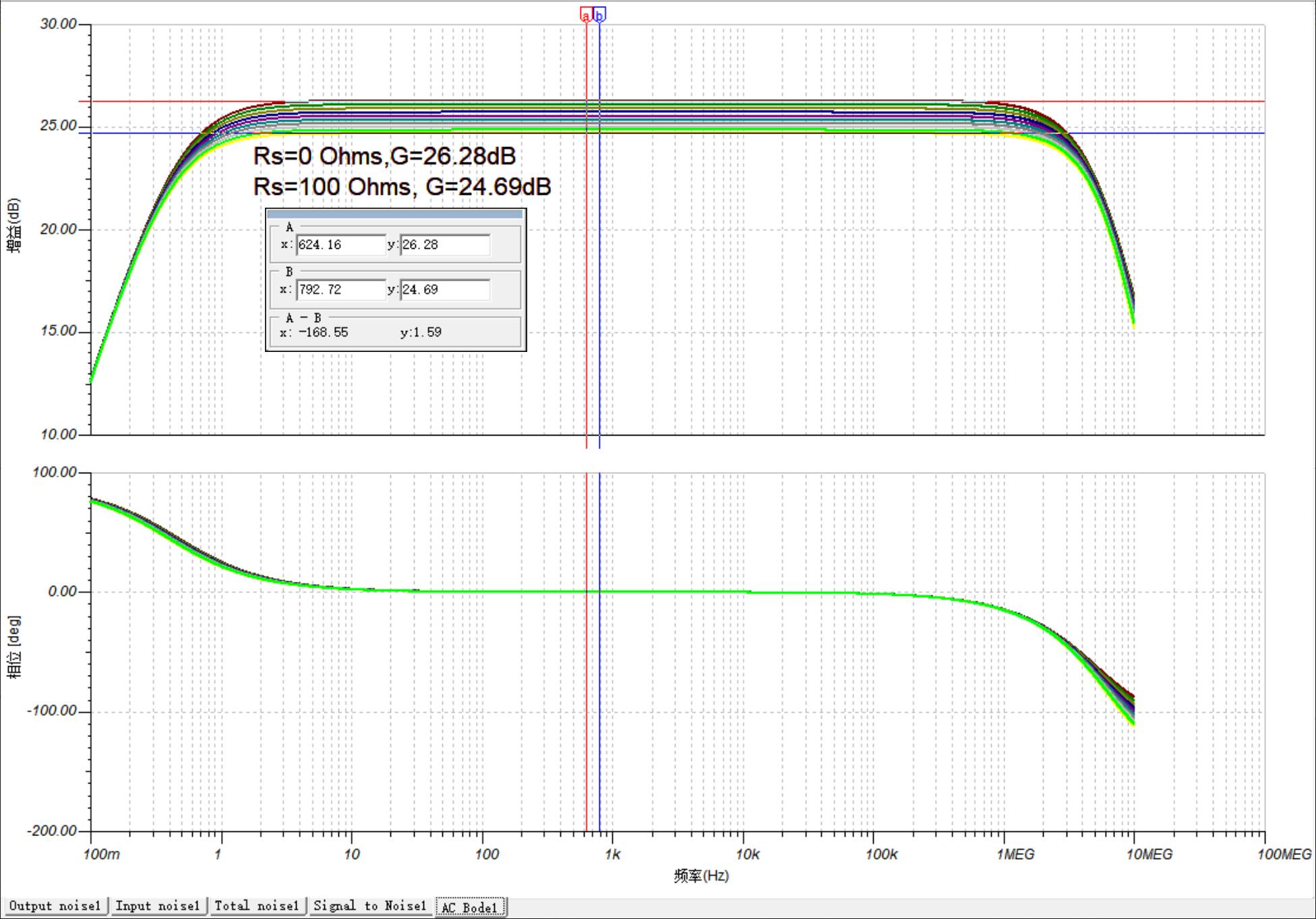

那么源阻抗对电路增益的影响如何呢?我们再执行一次参数扫描分析,得出以下增益曲线:

可以看到,即使源阻抗增加到了100欧姆,增益也没有降低超过2个dB。这里的增益下降并不是运放的问题,而是源阻抗和输入的RC高通滤波器网络中的电阻构成了分压器结构,运算放大器的同相输入端接在该分压器的输出,所以导致了增益下降。

You Complete me!

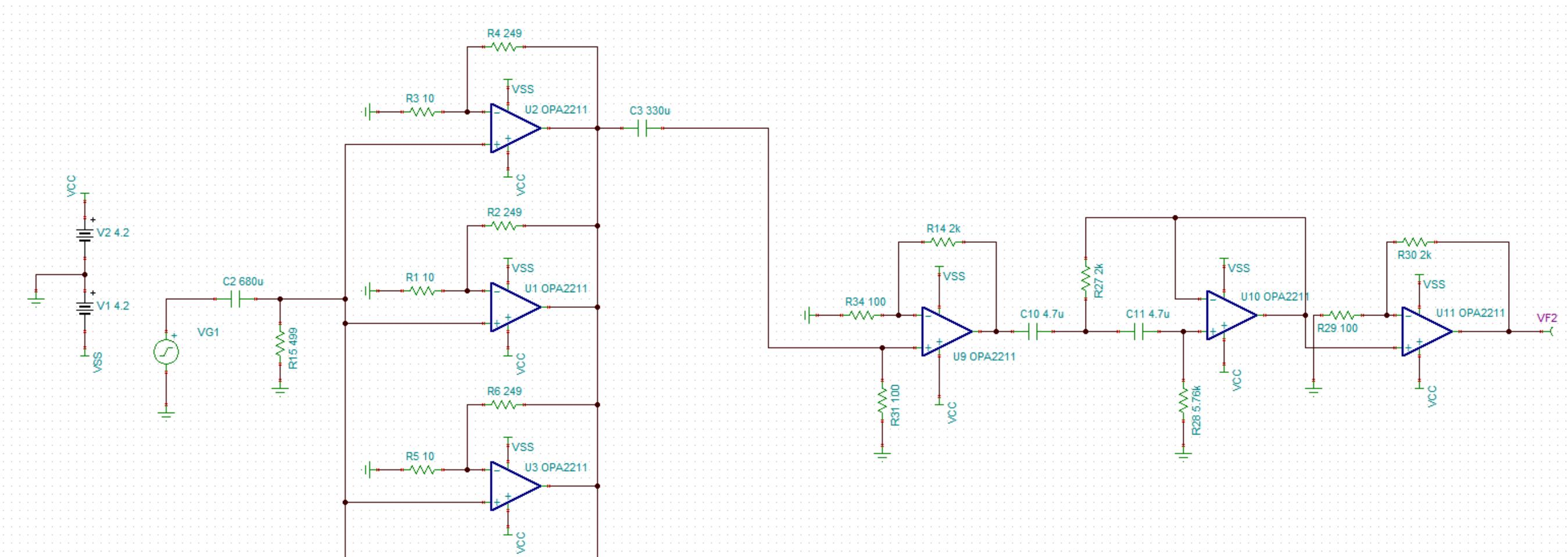

现在我们可以直接在Tina中验证NAP的系统性能了。直接搭建NAP的放大电路部分的仿真原理图:

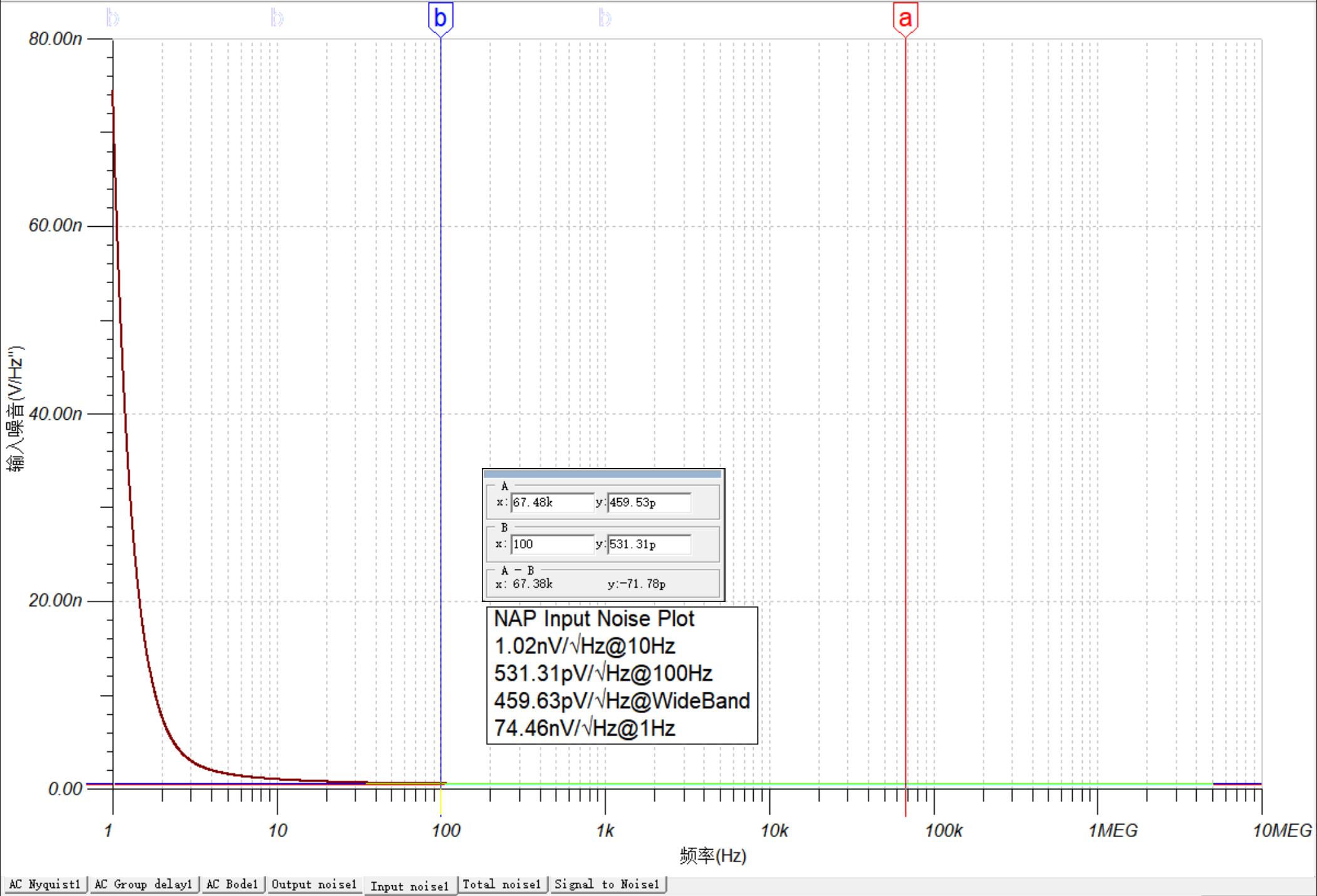

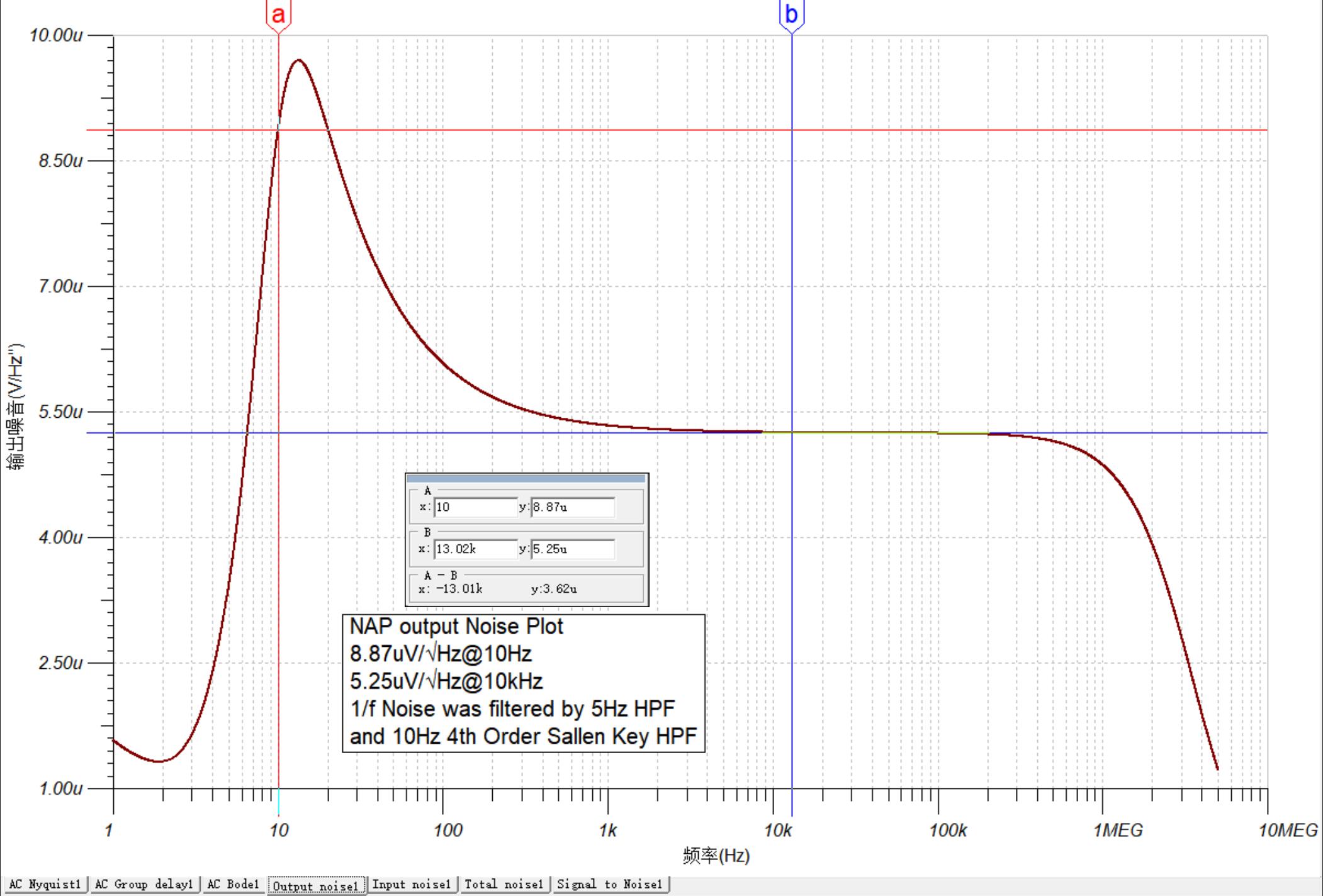

前面是8个同相放大器并联组成的超低噪声前放(G=25),后接了一5Hz RC高通滤波器后又经过了两级G=20的放大器放大,同时还经过了一个4阶 Sallen Key 高通滤波器,最后整个电路实现了10000倍电压增益(80dB)。然后对其交流性能进行仿真,得到结果如下:

交流增益,-3dB通带约为10Hz-2.17MHz

输入电压噪声谱密度,跟前面的仿真结果接近

输出电压噪声谱密度,我们本应期待在极低频处看到1/f噪声曲线的形状,可是这一段被2级高通滤波器抑制掉了很大一部分。

总输出噪声,我们可以大致从图中读出其噪声水平。

从最后的总输出噪声图中我们可以读出,在100kHz带宽内NAP的输出噪声为1.66mVrms,在1MHz带宽内NAP的输出噪声为5.12mVrms。由于100k和1MHz刚好跨越了一个倍频程,我们可以将5.12除以根号10,得到1.66的近似值1.62。

校准&验证

是的,我们仍然使用上一次我们展示的噪声放大器(V2.3)来进行这次的校测工作。(才不告诉你是因为新版(V2.4)还躺在我新建的文件夹里呢orz)

增益校准

校准的过程还是跟上次一样,不过注意一点就是衰减器的制作~

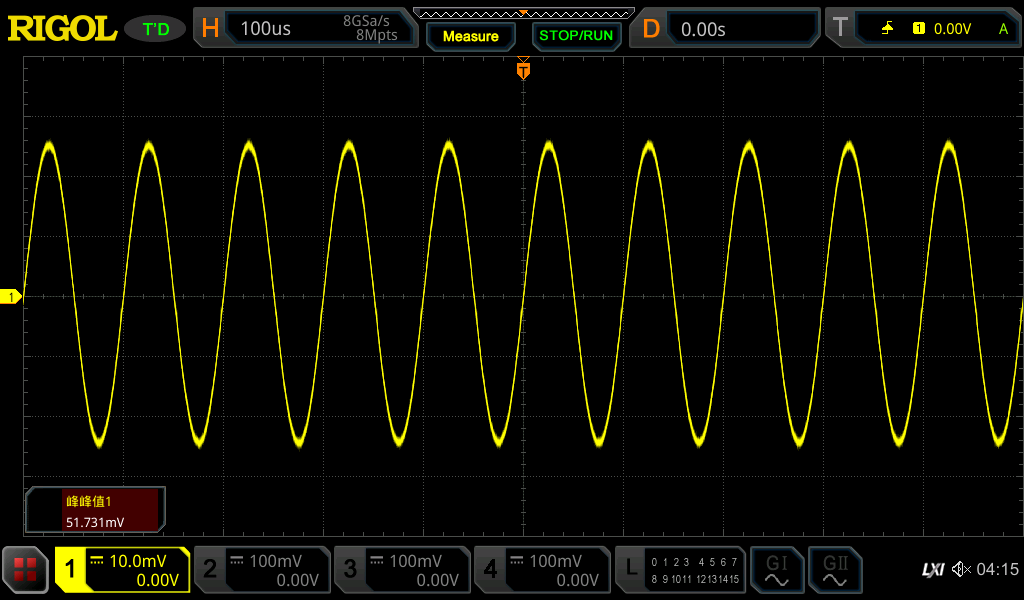

我上次使用的衰减器由100k和1k电阻构成,但其实可以用更小的电阻。这次我用100Ω和1Ω重新制作了一个用于增益校准。这时请注意设置信号源的输出阻抗,以匹配衰减器的输入阻抗。

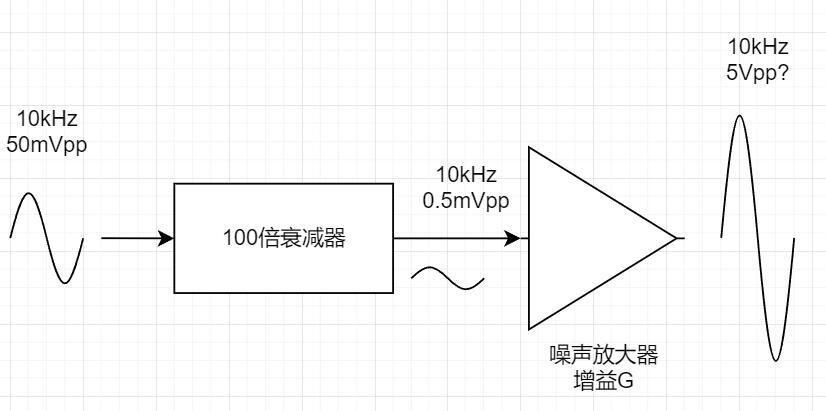

可以先用示波器看看信号源输出50mVpp的信号幅值是否准确,然后再进行校准工作。50mVpp信号衰减100倍然后放大10000倍,最后将输出5Vpp信号,perfectly matched。(要是500uVpp的信号都做不到无失真低噪声放大,那这NAP可以扔了…)

底噪测试

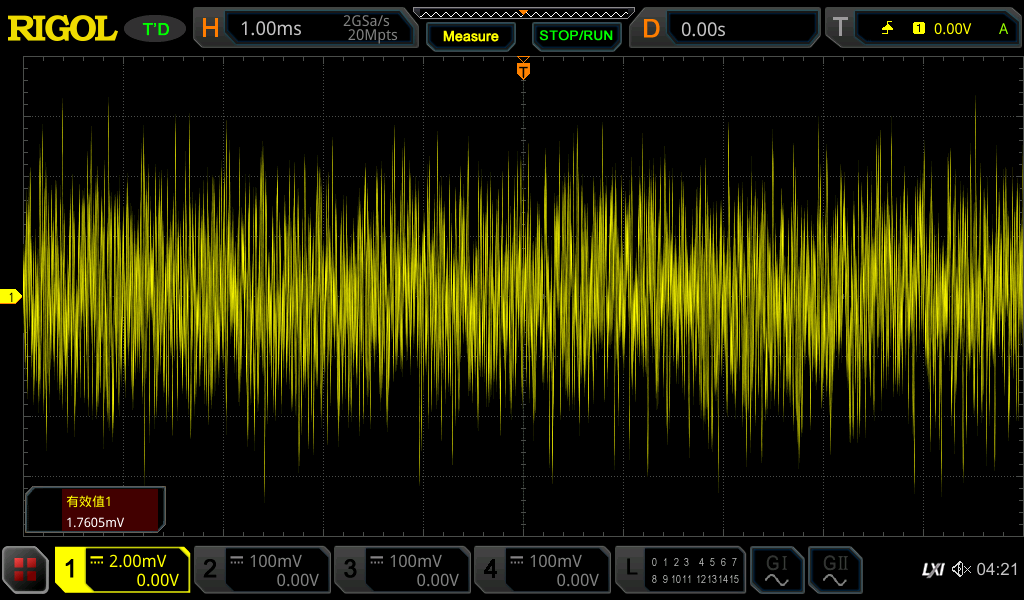

然后我们再次进行底噪测试。将输入使用一个短路的SMA座子短接,测量100kHz内的带限噪声:

测量的结果是1.76mVrms,而我们上面仿真的结果是1.66mVrms。从 运算放大器噪声分析 中我们学习过的 等效噪声带宽 理论我们可以得知,4阶低通滤波器的等效带宽系数是1.026,那么将1.66*1.026得到的值为1.703。ohhhhhhhhhhhhhhhhh!!!

考虑到示波器的测量和计算误差,所测得的1.76mVrms是真实存在的!

至于之前我为什么测出来约为4.几mVrms… 我只能说我也不知道啊orz,我把NAP带到北京来之后他就成这样了呃,可能是我之前的仪器有问题吧23333

当然是之前的示波器有问题啊!我回过头一看,之前测试用的示波器直流offset漂飞了,rms测出来及其不准确!(

热噪声测试

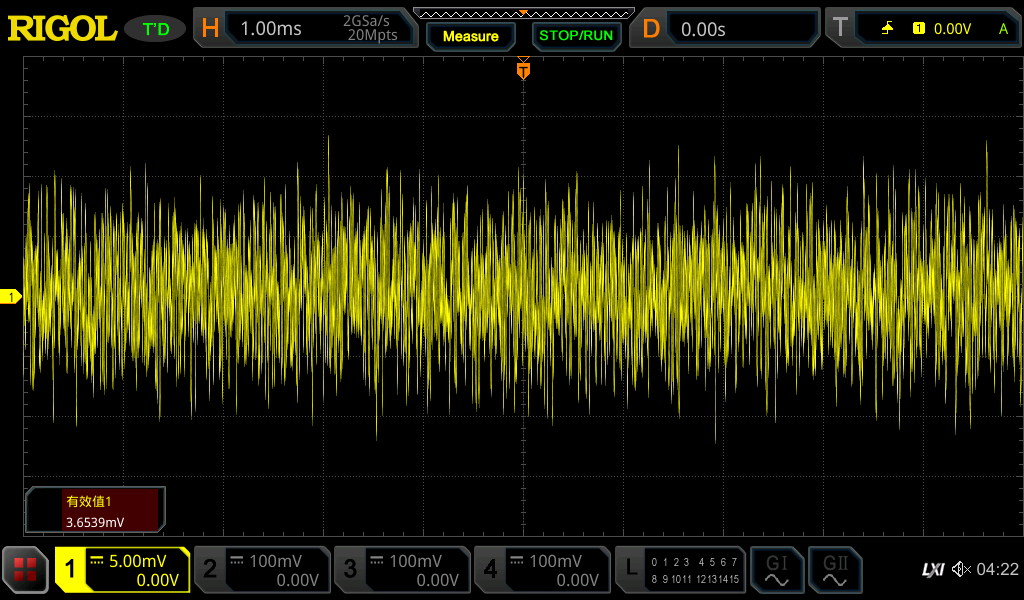

当然光验证这一个是不够的。我们将输入接上50Ω的SMA负载帽,这次我选了个质量很不错的负载帽。

测得的噪声真有效值为3.654mVrms。现在我们来do some math:

一个50欧电阻在25°C室温条件下,在100kHz带宽内产生的热噪声约为:

V_n = \sqrt{4k_BTR\Delta f} Vrms \\

代入数值,V_n = 287.74nVrms考虑到4阶低通滤波器的等效噪声带宽,我们将底噪与该计算值求方和根:

V_{out} = \sqrt{V_{noisefloor}^2 + V_{n}^2} = \sqrt{176^2+(287.74*1.026)^2} = 343nVrms理论计算得出,我们应该在100kHz带限输出端观测到3.43mVrms的噪声,实际测量值约为3.65mVrms,约有5%的误差,perfect。

LM399噪声测试

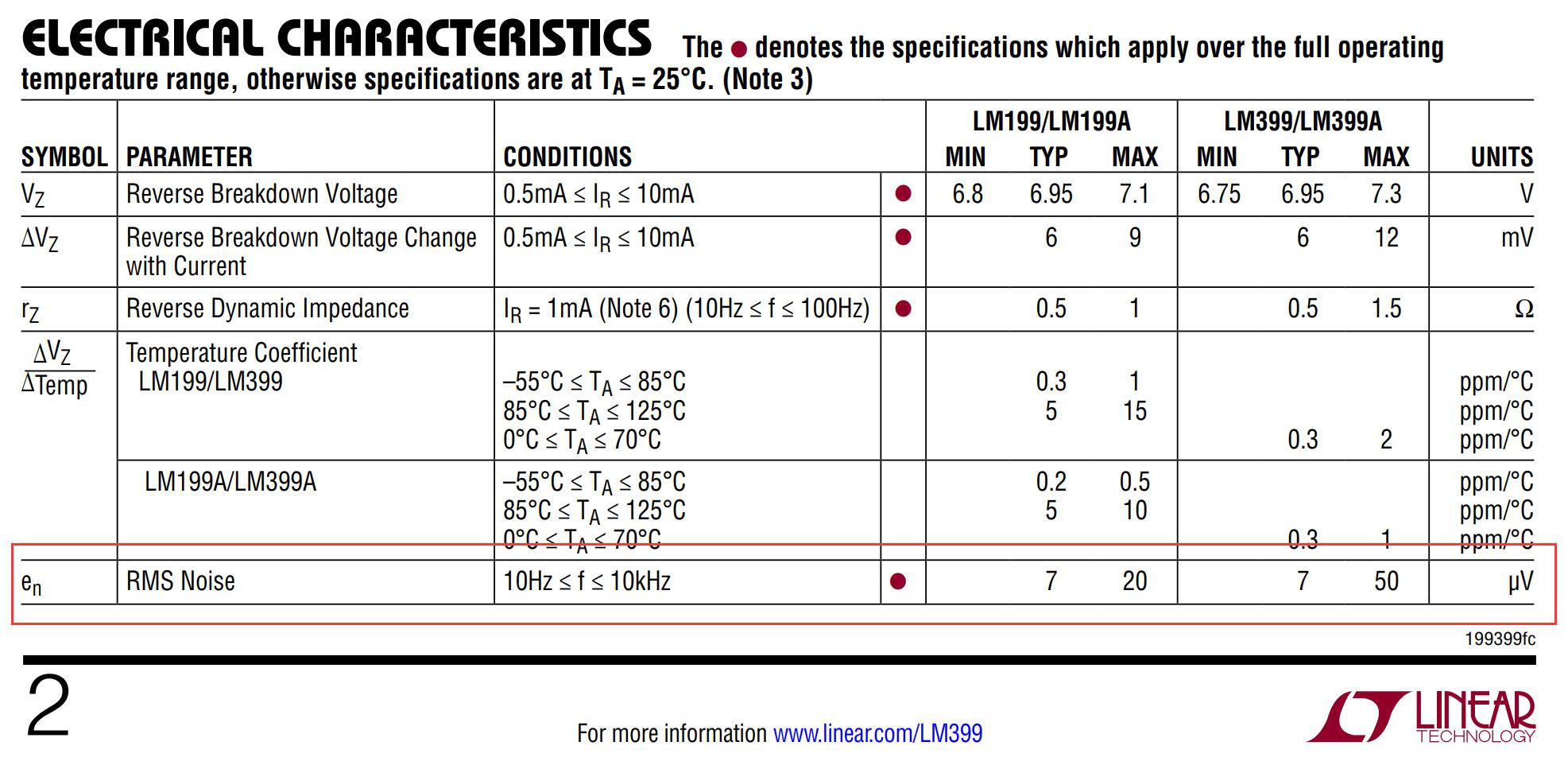

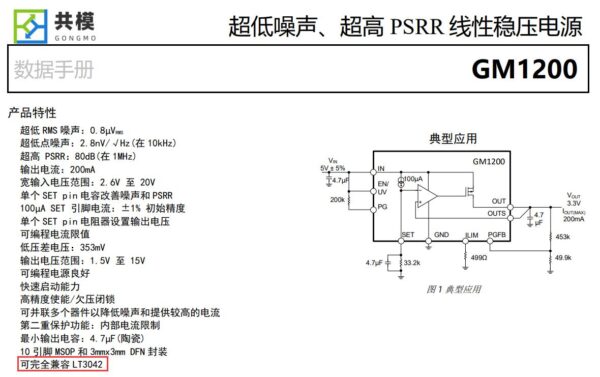

然后我们来测测LM399基准电压源的输出噪声。399的手册中标注其10kHz带限噪声不超过50uVrms,最低为7uVrms

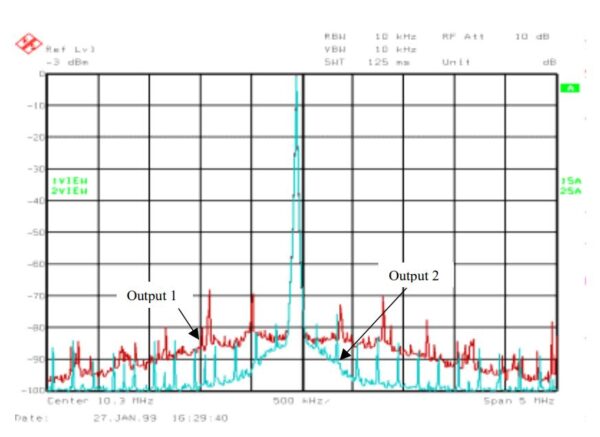

然后我们现在只能测它在100kHz带限内的噪声。。唔,还是先看一眼谱密度让俺心里有个数——

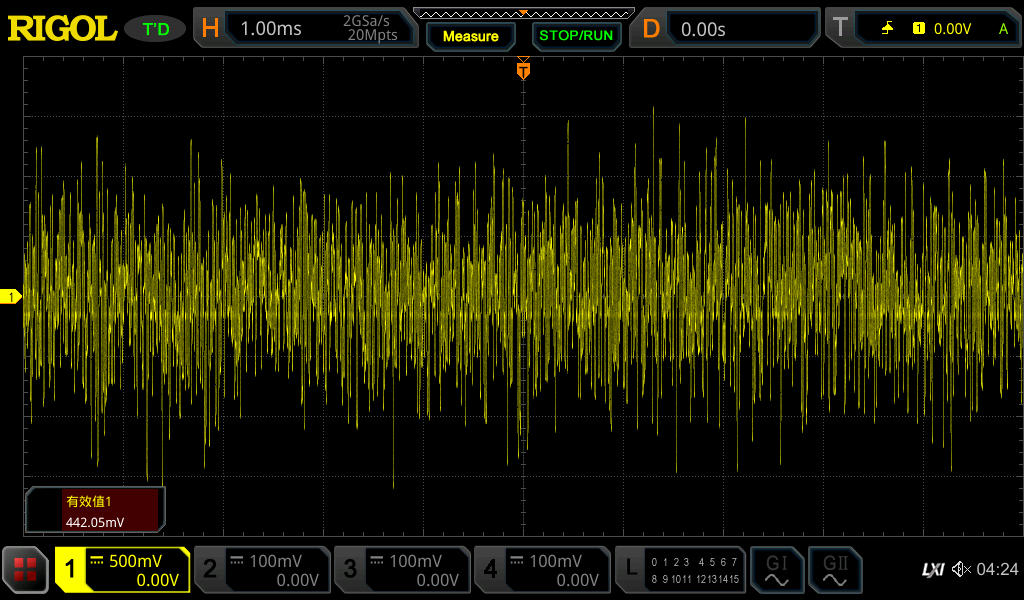

可以看到,其噪声电压谱密度在100-1k,1k-10k这两个倍频程中基本保持一致。在10k-100k这个倍频程中有所减小。忽略极低频段的1/f噪声,它们对10Hz以上的最终输出噪声贡献不是特别大,假设10kHz-100kHz段的电压噪声谱密度维持不变,现在所有噪声是对10Hz-100kHz积分,那么其大小理论上来说是手册中标定的标称值的根号10倍(3.16倍)。让我们来看测量结果:

测得442mVrms,此时可以不考虑底噪的影响,直接换算出真实噪声为44.2uVrms。除以3.16得到约14uVrms,刚好是手册标定的最小值的2倍,性能达标√

To be continued.

告一段落,等俺完善了NAP的设计,我会补完后面的内容的:)

本项目的github仓库在此: https://github.com/Floyd-Fish/Noise-Amplifier

此repo包含了工程文件和部分描述文件。

以及,我将这个项目扔到了Hackaday上,投稿了OpAmp Challenge: https://hackaday.io/project/190870-take-a-nap-and-enjoy-a-moment-of-silence

![雷达信号处理-[1]-噪声信号与雷达基带信号产生](https://www.emoe.xyz/wp-content/uploads/2021/11/4-2-600x316.jpg)

感谢分享。N级并联放大器并不会降低噪声,噪声实际上会增加sqrt(N)倍,并联放大器的后级一定要是加法器,不然没意义。

并不认同您的说法。文中有运放输出并联后接同相放大器的高阻输入仿真实例,您也可以试试在spice里搭建一个并联运放模型验证一下,后级并不需要加法器。

我觉得示波器测量应该用方差,而不是有效值。方差就是AC有效值。

可是示波器的AC有效值测量项就是方差啊(

额 但是 我看你图里好像用的是DC有效值啊。所以会受到示波器offset不准的影响。如果用AC有效值测量应该不会受到 offset飘飞的影响吧?

是的,DC offset不准会对测量结果造成很大的影响,第一版噪声放大器的测试就是因为DC漂了导致读有效值误差非常大…这一版测试的时候我在输入接地的时候验证过dc误差,基本在100uV以下级别,不影响有效值读数的。。当然最好还是用AC有效值测量项去测试