本文目录

PCB设计基础-退耦技术

在上一篇文章 PCB设计基础-常识篇 中,相信你已经对PCB设计有了初步的了解。这次我们来了解一个非常重要的知识——退耦技术。

无论是设计数字电路还是模拟电路、高速电路还是精密电路,退耦技术都是保证电路性能的有力技术保障。不过想要深入地理解退耦的原理,还是比较痛苦的…我们先从导线的物理模型讲起。

导线不是导线

看起来有些分裂的一句话,不过往后看,相信会略微颠覆一些你的认知。

拿起一截铜线,它在你眼里有哪些参数呢?

我相信你第一个想到的是它的 电阻。没错,我也是这么想的。但是这是对于直流信号来说的最主要的参数。但对于交变电流,它的身份一下子复杂了几个维度。

寄生参数

寄生参数(Parastic elements) 是一个电子元器件所拥有的除自身本应有的参数之外的参数,而这个寄生参数通常是我们 不想要的。比如一个电阻器,我们只希望它拥有电阻这一个属性,然而在真实世界中它同样会具有电感值和电容值,而多出来的电感&电容值就是寄生参数。

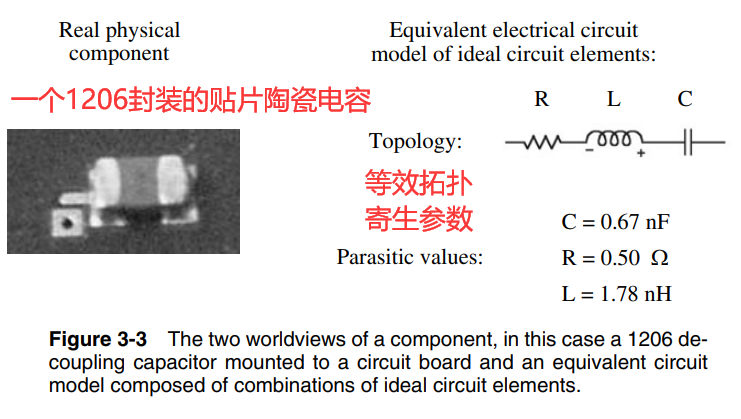

一个贴片封装的1206陶瓷电容,同时具有寄生电感、寄生电容和等效串联电阻(ESR)参数

(选自信号完整性与电源完整性分析-Eric Bogatin)

通常来说,我们的电路如果工作在较低频率段或者直流,这些寄生参数所带来的影响可以忽略不计,但一旦来到 高速及射频(300kHz数量级以上) 的领域,我们电路的性能往往由这些寄生参数所决定。

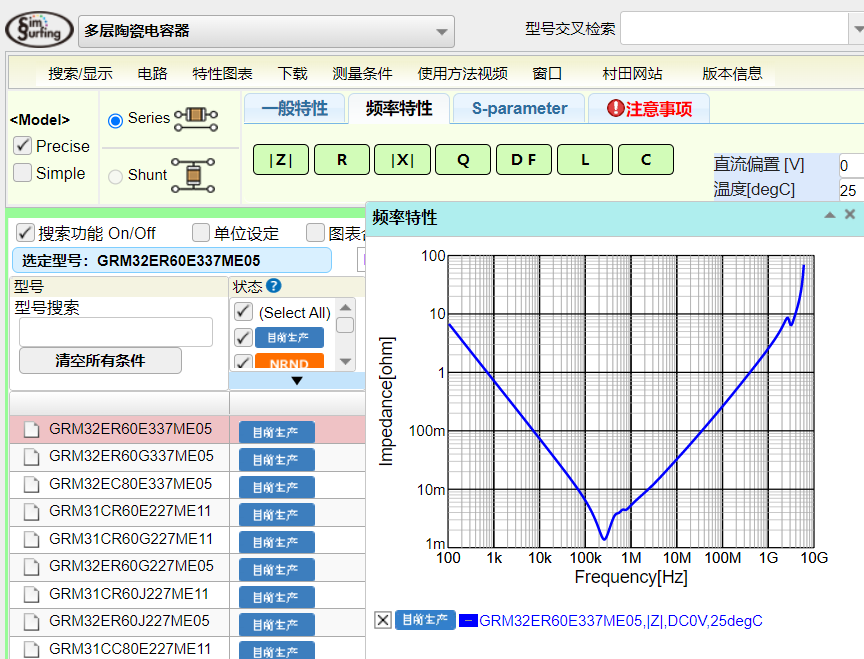

举个例子,我们去 村田(Murata)的官网 找到SimSurfing选型工具,然后随便点开一个电容的 阻抗-频率特性 图表,可以看到在低频区域(约250kHz以下)该电容呈现了电容的特性——频率越高,阻抗越小,而在该转折点之后,反倒呈现了电感的特性——频率越高,阻抗越大。

是不是有些违反常识?为什么会这样呢,当然是寄生参数在起作用咯。这个陶瓷电容的所有寄生参数等效出来的电路实质上是一个RLC谐振电路,阻抗-频率图表的转折频率点就是该等效谐振电路的谐振频率点,在该点前后,这颗电容所呈现的电气特性完全不一样。

不只是电容,电阻、电感、甚至一截平平无奇的铜导线都有这样的寄生参数。还要补充一个小知识——

集成电路的封装进步不仅仅是为了缩小集成电路的体积,以提高PCB空间利用率。早期的直插封装(如双列直插-PDIP)所引出的引脚实际上有着不小的寄生参数,在早期的低速电路中还不会形成太严重的影响,然而在高速电路中,这些PDIP封装的芯片再也难以使用。所以半导体厂商逐渐开始使用寄生参数更小的贴片封装,如SOIC、QFN、WSON、BGA、LFCSP等。所以你现在看到的高速运算放大器、FPGA等器件,基本没有直插封装的了。

怎么样,看完这些后,平日你眼里平平无奇的电阻电容电感是不是变得有些陌生且恐怖呢;)

顺便,用洞洞板和杜邦线做高速电路的朋友们,你们做的电路性能怎么样呢🤔

PCB导线(Trace)的寄生参数

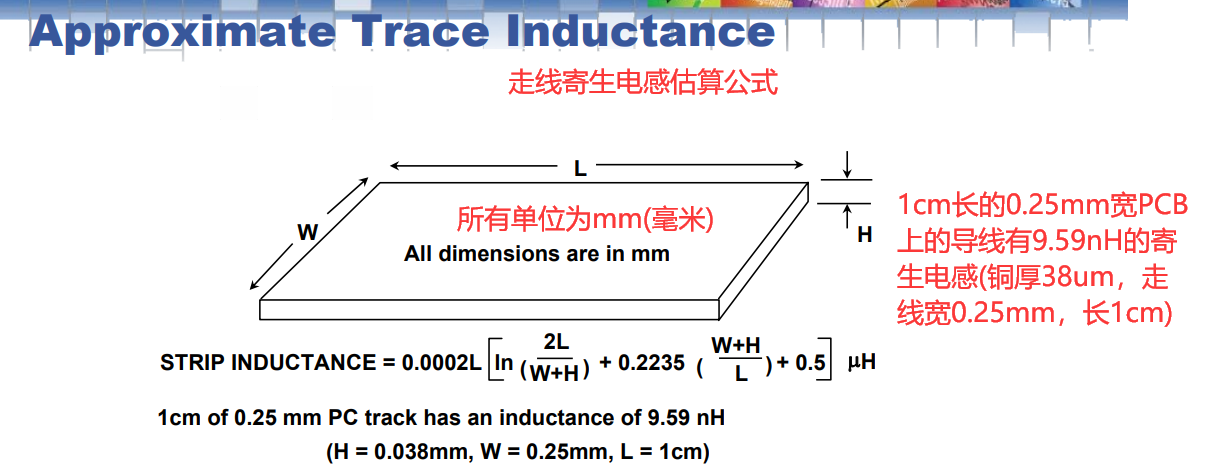

在这里我不作详细的数学&物理推导了(其实是我不会),直接给出ADI的PPT上的结论:

导线的寄生电感

我重写一下就是:

寄生电感= 0.0002 * L[\ln{ 2L \over (W+H)} + 0.2235({W+H \over L})+0.5] (uH)导线、焊盘的寄生电容

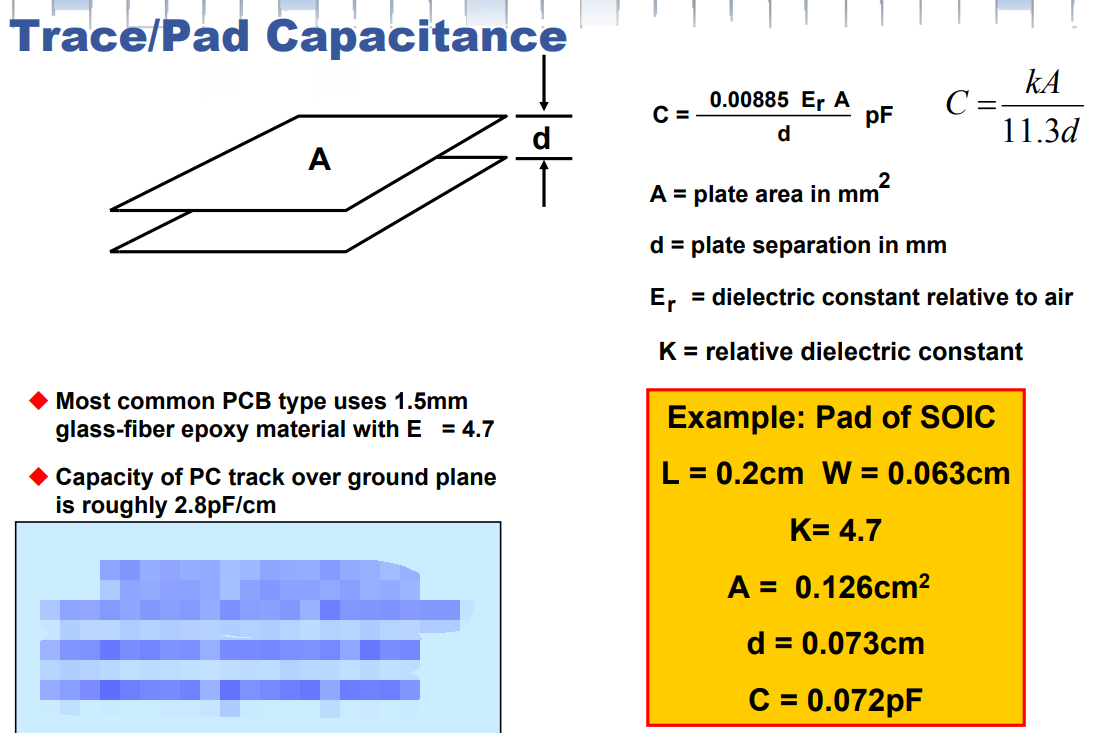

别忘了,任何两个彼此绝缘的导体之间都可以看作一个电容。对于PCB上的走线、焊盘都是如此。

重写一下这个估算公式:

电容C = {kA\over 11.3d} = {0.00885\Epsilon_r A \over d} (pF)尤其要注意布设在地平面上的PCB走线,由于跟地平面正对的面积非常大,寄生电容也会非常大,在高频电路中这可不是什么好事情.jpg

一定程度上减小寄生参数的方法

对于寄生电感,有如下三种方法:

- 在PCB中设计一层完整地平面,可以减小走线的寄生电感;

- 尽量走短线,将线长缩短一半,寄生电感减小44%;

- 增加线宽,不过收效甚微。加倍线宽只能减小11%的寄生电感。

而对于寄生电容,有些矛盾的点:

- 增加板厚度(或增加铜层之间的距离);

- 减小PCB焊盘的面积和导线宽度(减小正对面积);

- 移除关键导线正对的地平面(这就与寄生电感相悖了)。

而在设计时,需要根据具体的应用和需求来做决定。

去耦(decoupling)

如果电源引脚上存在纹波或噪声,大多数IC的性能将会有所下降:数字IC的噪声裕量会降低、时钟抖动可能会增加,如果纹波较为严重,甚至会达到不能正常工作的程度。而模拟IC(运算放大器等)则是会在输出中直接耦合了电源纹波或噪声。🐟之前写的 精密低噪声电源设计-理论篇 中对于这一块有详细的介绍。

退耦,又称 去耦(decoupling) ,意思是 去除电源轨上的耦合噪声。用于去耦的电容就被称作 去耦电容(decoupling capacitor)。本文的重点就要讲解如何去耦~

顺便,几乎所有的IC的参考设计中 都会添加去耦电容。至少🐟看了这么多数据手册,无论是opa、adc/dac、mcu、FPGA、flash、…,它们的reference design的电路图中无一例外地在电源轨上添加了去耦电容。

纹波&噪声从何而来?

我们来设想一个数模混合系统。在这个电路中,3.3V电源轨上接了一个工作频率160MHz的单片机,同时还接了一个低压运算放大器,用于调理某个传感器的信号,并将调理好的信号送入ADC进行采样。

通常我们的直觉是,用电器消耗的电流是恒定的——即从上电那一刻,电源输出的电流就不再变化。然而仅仅是美好的幻想。单片机在空闲时消耗的电流和执行计算任务或操作外设时消耗的电流有很大的差别。而工作在160MHz主频下的单片机的电源是时刻变化的:可能上一微秒需要1mA电流,下一微秒就会需要5mA。。而不断快速变化的电流就会在电源轨的导线(具有电阻和电感)上产生不断变化的电压,也就产生了高频 纹波(Ripple)。你可以拿示波器看看高速数字器件的电源轨,很dirty的。

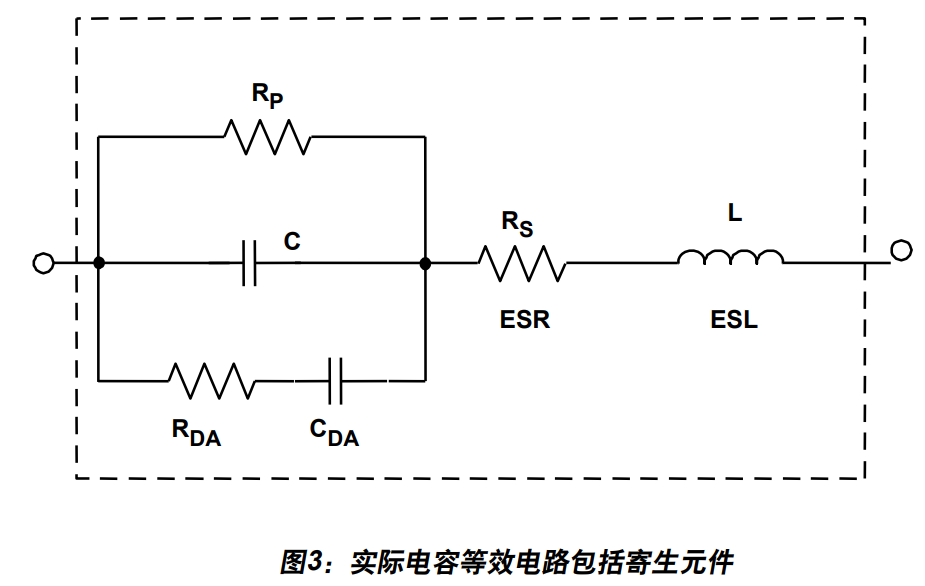

电容类型

我们首先来看一个实际电容的更为复杂的等效电路。它有寄生和等效参数如下:

- Rp – 绝缘电阻(泄漏电阻)

- Rs – 等效串联电阻(Equivalent Series Resistor, ESR)

- L – 等效串联电感(Equivalent Series L, ESL)

- RDA\CDA – 电介质吸收(Dielectric Absorption, DA)现象模型

在采样保持放大器等精密应用中,电介质吸收现象会造成显著误差,需要加以考虑,而在去耦应用中一般可以不考虑。

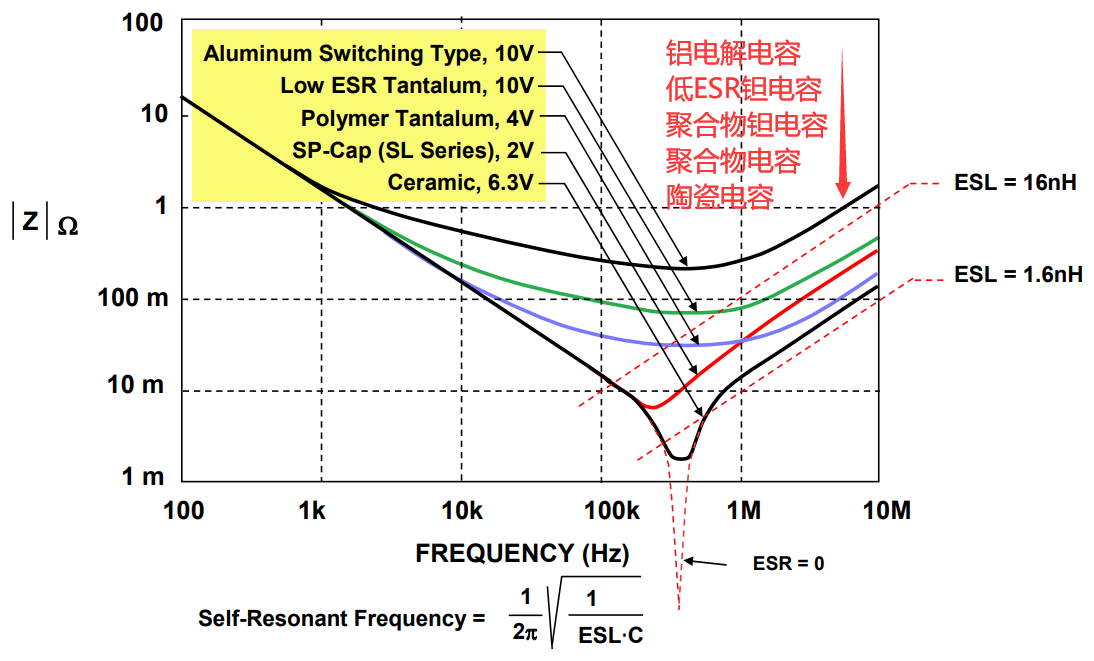

再来看一张之前看过的、喜闻乐见的图。该图显示了5种不同类型的电容器的阻抗-频率曲线。

这些阻抗-频率曲线的 谷处 的宽度、位置和凹凸程度都取决于电容的各项寄生参数。虽然不同电容的曲线不同,但都有着同样的规律——即低频区域由ESR主导,高频区域由ESL主导,转折点由自谐振频率决定。

铝电解电容具有较高的ESR,所以阻抗曲线随着频率从0慢慢升高,逐渐趋近于一个较大的值(约几百mΩ),而陶瓷电容的ESR较小,所以能降低到更低的值。下表是部分不同类型的电容的特性对比:

| 电容类型 | 优点 | 缺点 | 应用领域 |

|---|---|---|---|

| 高频铝电解电容 | 高性价比、大容值、高耐压 | 温升磨损严重、较高的ESR | 消费电子、工业 |

| 固态钽电容 | 高容积比、低温下稳定、无磨损 | 反压会boom、贵贵、耐压不高 | 军工、高可靠性应用 |

| 铝聚合物、特殊聚合物、PosCap、Os-con | 低ESR、阻抗温度稳定、相对小体积 | 105°C以上容值快速降低、相对高成本 | 最新技术、CPU核心电压稳压器 |

| 陶瓷 | 最低ESR、ESL,耐受高纹波电流、X7R介质能在宽温度范围内工作 | 容值与耐压不可兼得、压电陶瓷效应、偏压效应 | 高频去耦、有能力工作至1GHz |

| 薄膜电容(聚酯纤维、特氟龙、聚丙烯、聚苯乙烯等) | 大体积高Q值、无磨损、耐受高电压 | 容值与耐压不可兼得、贴片封装少见、高成本 | 高压、大电流应用、交流应用、音频应用 |

去耦电容选择

- 铝电解电容

多数去耦应用中不建议使用"通用型铝电解电容",但 高频型铝电解电容 被设计成可以在数百kHz的频率下处理高频脉冲电流,且具有低损耗特性,在某些场景下高频铝电解可以媲美固态钽电容,但通用铝电解电容不推荐。

- 钽电容

固态钽电容的耐压一般低于50V,容值低于500uF,对于相同的尺寸,固态钽电容比铝电解电容具有更高的电容体积比,且具有更高的频率范围和更低的ESR。也更贵(小声)。对于浪涌和纹波电流滤波去耦应用需要谨慎对待(怕超耐压boom了)

- 陶瓷电容

陶瓷电容,或多层陶瓷(MLCC)具有尺寸紧凑和低损耗特性,通常是数MHz以上的首选电容材料。但是陶瓷电容分为多种介质种类,不同介质的MLCC电气性能相差很大。下表是一些常见类型的陶瓷电容对比:

| 材质 | 容量范围 | 特性 | 温度稳定性 | 应用 |

|---|---|---|---|---|

| NP0(C0G) | 多数0.5pF至10nF | 容量稳定、介质损耗小,稳定性高 | 极佳 | 高频耦合电容、有源滤波器、振荡器 |

| X7R | 330pF至0.1uF | 同体积下容量更大、温度稳定 | 较好,±15% | 要求不高的消费电子PCB |

| Z5U | 10nF至0.47uF | 容积率高、容量不稳定、小尺寸低成本、低ESL和ESR,良好的频率响应 | 不是很好 | 去耦电容 |

| Y5V | 10nF至4.7uF以上 | 高介电常数(容量大)、有温度限制 | 不是很好 | 高密度PCB |

- 薄膜型电容

薄膜型电容一般要使用绕线和长引脚,这将极大增加ESL,因此不太适合用于电源去耦场合。相对的,薄膜型电容更适合用于音频场合。

电容去耦技术小结

多层陶瓷(MLCC)表面贴装电容的极低电感设计可提供近乎最佳的高频&射频旁路,因此在10MHz或更高频率下的去耦电容多数会选择使用MLCC。封装体积更小的陶瓷芯片电容工作频率范围 可达1GHz。对于高频应用中的这些及其他电容,可通过选择自谐振频率高于最高工作频率的电容,确保去耦电容的有效性。

当然,一般推荐的做法是—— 使用一个大容量(10uF-100uF)的电解电容并联若干小容量的陶瓷电容 来完成去耦。去耦电容的原理和使用方法如下:

- 大电容的作用是充当IC的动态电荷库,在芯片的输出功率动态变化时,电容就近给芯片提供能量,无需从远端的电源获取。

- 小容量陶瓷电容的作用是将电源轨上的&器件产生的高频纹波或噪声对地短路

- 去耦电容应该尽可能靠近芯片,同时具有最短的回流路径,这对PCB布局布线提出了要求

- Impotant: 所有的去耦电容都应该使用尽可能短的连接线连接到一块低阻抗地平面,以最小化引线电感(同时可满足最短回流路径)

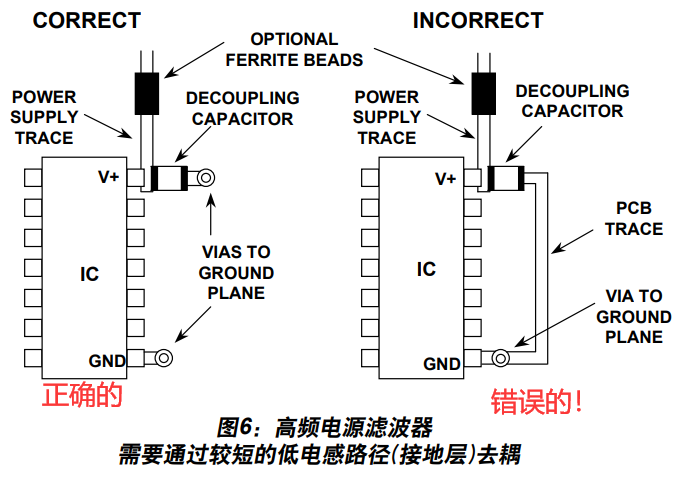

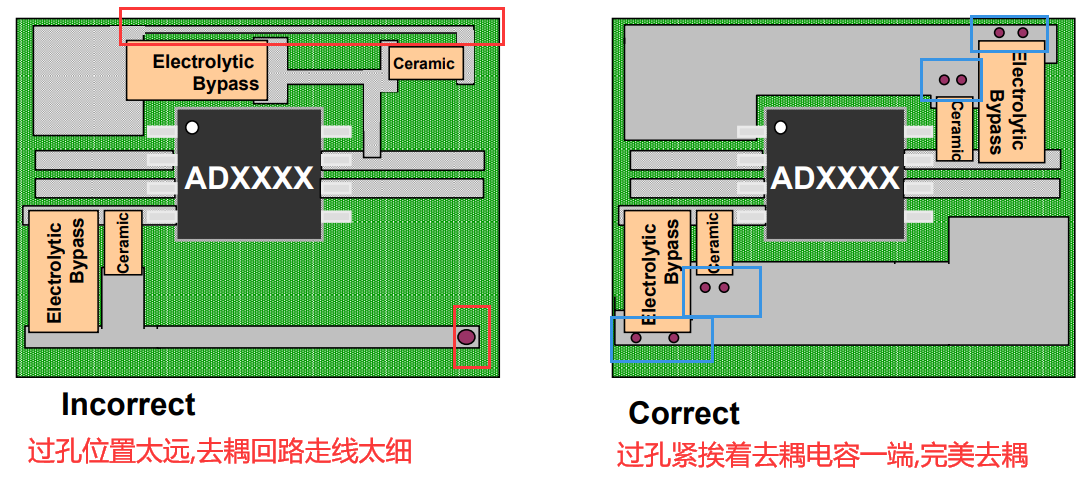

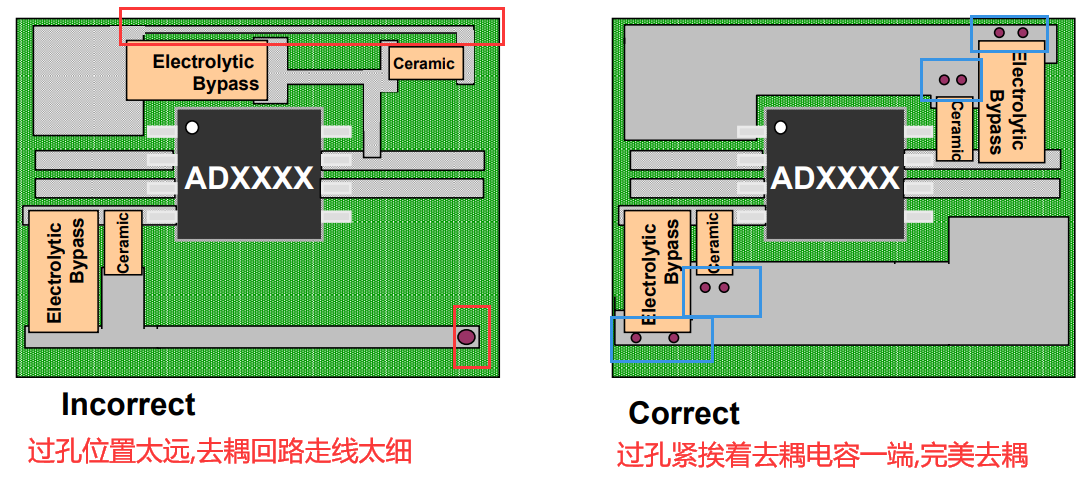

下图展示了电容去耦的正确布线技术。左图中,电容一端紧靠着IC的正电源引脚,另一端通过过孔直接接入PCB下方的完整地平面,这样就可以实现最短的去耦路径。而右图中,去耦电容的另一端通过一段导线连接到IC的GND引脚,看似是较短路径,实则这一段导线的ESL和ESR远不如完整地平面的小。并且,这样连接同时还形成了一个闭合的环路,这将使得该电源环路更容易被其他电路干扰,同时更容易导致各种信号完整性问题。

同时还有一张实物对比图。注意该PCB下方是有完整地平面的。

劲更大的LC去耦与磁珠

同样的,在🐟之前写的 精密低噪声电源设计-理论篇 中已经详细地介绍了无源LC滤波器在电源去耦中的应用。当时我使用LC滤波器的目的是为了滤除在LDO输出端由上级开关电源产生的纹波,其实也相当于去耦,不过去耦一般是相对于负载来说的,而电源芯片一般就叫滤波了~

磁珠与电感的区别

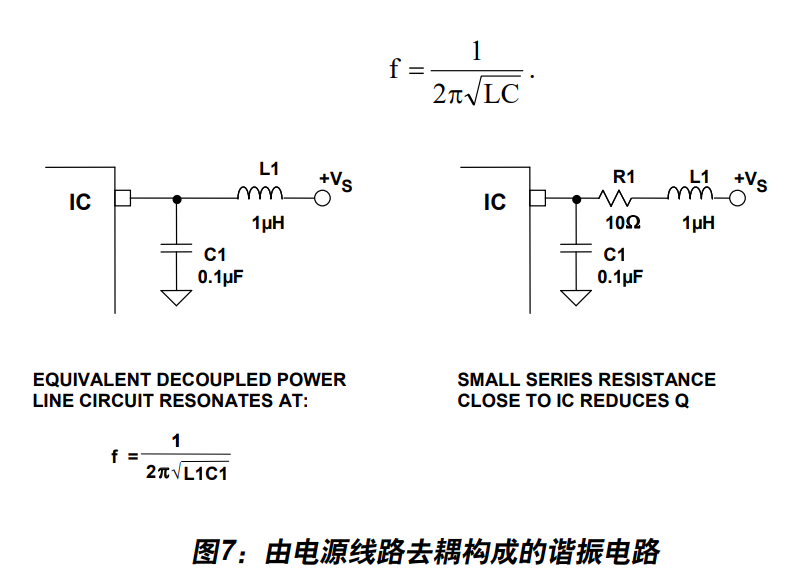

之前的文章中提到了,使用LC滤波器会导致该电路有谐振点。如果选择元件不恰当,反而会增强目标频段的纹波和噪声。

正常走线的寄生电感也会和电容产生谐振点。例如一个0.1uF的电容和具有1nH ESL的走线将在16MHz左右产生谐振。单纯地使用LC来完成去耦,可能会出现谐振增强的现象。具体增强与否与电路Q值有关,如果在电感后串入一个小电阻,可以有效降低Q值,避免这种增强现象。

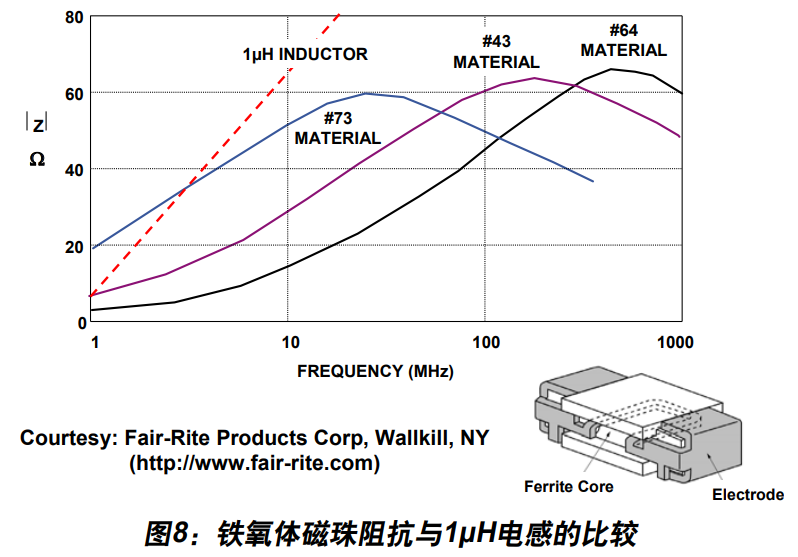

当然这个小电阻需要尽可能地小,以降低电阻的压降。也可以使用铁氧体磁珠来代替小电阻完成这一工作,磁珠的直流导通电阻接近于0。铁氧体磁珠在谐振频率下主要呈现为阻性,所以使用磁珠也会降低电路的有效Q值。典型铁氧体磁珠的阻抗-频率曲线如下图所示:

实战

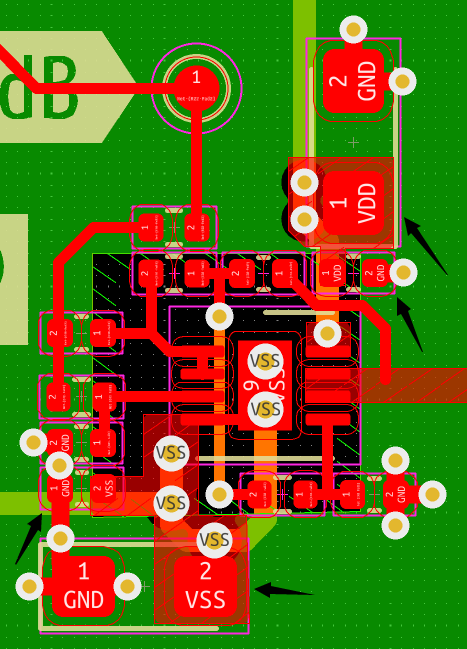

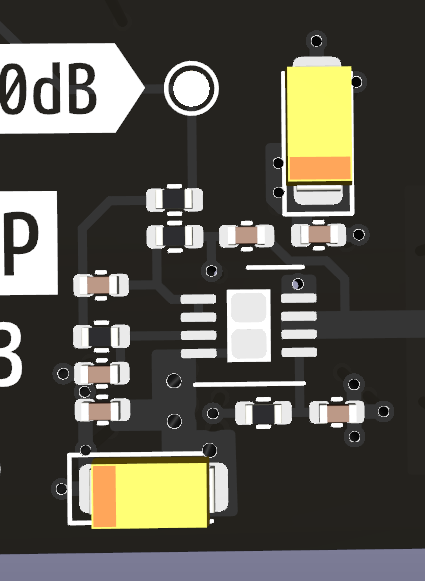

🐟之前画的NoiseAMP_V2.3的板子就很适合作为栗子。

绿不拉几的这张图是PCB设计图,绿色的部分是PCB背面的完整地平面,中间偏右下的大方块就是运算放大器,黑色箭头指出的4个元件分别是正负电源的去耦电容。

运算放大器下方的区域做挖空处理,以减小运算放大器敏感线路的寄生电容。我这里其实偷了个懒。PCB正面(红色的铜区)应该覆铜后打孔的,我懒得覆了就直接拉了2根线打过孔下去…这种是不对的!(虽然用着没什么问题,但是不建议这么用)

还是看看远方的ADI吧家人们。

![电子入门教程[04]—喂?zaima?](https://www.emoe.xyz/wp-content/uploads/2020/02/uart3-600x379.png)

![Read more about the article [Bonjour STM32] No.5-demo 2.GPIO外部中断](https://www.emoe.xyz/wp-content/uploads/2020/05/GPIO_EXTI-300x247.png)