本文目录

序

时间像一把无形的利刃, 无声地切开了坚硬和柔软的一切, 恒定地向前推进着,没有任何东西能够使它的行进产生丝毫颠簸,它却改变着一切。

转眼间,我毕业了(不是被企业优化了,是大学毕业啦)。

毕业论文对我而言算是一项里程碑意义的工作:承前启后,继往开来。对之前的工作做了大致的总结,并且较为完整地设计并制作了一个工程实物。在论文工作中包含了理论分析与设计考量的种种细节,最后也算是做出了个能拿得出手的简单作品。我想在此将这篇论文完整地分享出来,以供后来者参考。

在完成毕业设计论文之前,我在Emoe写了2篇关于DDS技术和1篇关于基础调制技术的文章,写论文时同时也回过头来参考了许多当时自己写的内容。

建议在阅读本文之前,看看之前的这三篇文章~

那么我们开始,全文长约4万字,还请耐心阅读。

摘要

中文

信号发生器作为一种可产生多种工程中常用的波形的现代化电子仪器,在通信、雷达与工业自动化测量等领域中具有重要的应用价值。数字频率合成(DDS)技术作为新一代频率合成技术具有低成本、高度灵活、信号质量高等特性,是现代信号发生器的主流解决方案之一。利用DDS芯片设计信号发生器可简化系统设计,便于集成到系统中,同时能够提升系统可靠性与长期稳定性。本文以数字频率合成技术、数字调制技术理论为基础,采用微控制器+AD9834芯片的架构,设计了硬件电路与软件开发,最终实现了一款能够产生多种波形同时具有调制功能的信号发生器,其具有输出信号质量高、参数调节灵活、低功耗与小体积等优点。本文的具体研究内容如下:

首先,论文分析了数字频率合成技术的原理及特性,包括采样系统的采样输出特性、DDS输出的重建滤波器选择。论文还分析了过采样、相位截断误差、参考时钟信号等因素对DDS杂散性能的影响,并且分析了如何根据DDS的特性去优化DDS设计以得到更高质量的输出信号。接着分析了DDS技术在数字调制领域的应用,包括线性与非线性调制、Chirp信号、多符号调制与QAM调制。

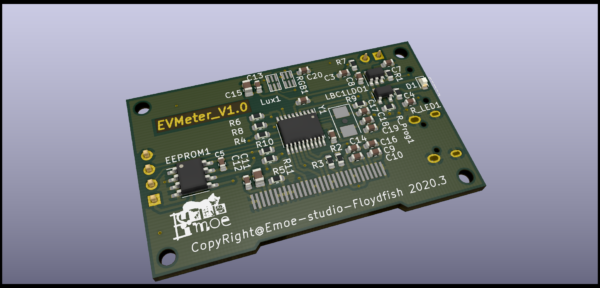

然后,论文完成了信号发生器的硬件系统设计。从设计需求出发,采用AD9834 75MHz完整DDS芯片+STM32L431RCT6微控制器的架构,使用KiCad EDA工具设计了信号发生器的原理图,完成了PCB Layout,进而完成了基于DDS芯片的信号发生器的设计。硬件系统由数字部分、模拟部分与电源拓扑结构组成,数字部分包含微控制器与外围电路、旋转编码器与液晶显示器电路、DDS时钟源电路;模拟部分包含DDS芯片及外围电路、DDS输出级与重构滤波器、DDS输出幅度控制电路;电源拓扑包括数字域电源与模拟域电源。

紧接着,论文完成了信号发生器的软件逻辑设计,通过对微控制器编程,采用有限状态机的逻辑设计方法完成了对系统的灵活控制与交互,最终实现了多符号FSK、PSK、ASK、Chirp信号、单频正弦及三角波信号的输出。

最后,论文对该信号发生器产生的单频正弦信号、Chirp信号等进行了测试与分析,同时进行了系统功耗测试。结果表明本文设计的信号发生器具有输出信号质量高、参数调节灵活、低功耗等特点,达到了设计的要求,并且在实际工程中能够得到较好的应用。

关键词:数字频率合成, 信号发生器, 数字调制, 易于集成, 低功耗

English

请不要吐槽我的 Chinglish 😀

As a modern electronic instrument,the Signal Generator plays a more and more important role in communication, radar, and automatic industry measurement fields, which can generate multiple waveforms that are commonly used in engineering areas.Direct digital synthesize(DDS) represents a new generation of frequency synthesize technics to achieve a low cost,highly flexible,high signal quality solution for signal generation.With DDS chips, it becomes more easy to perform a system level design, also improves system reliability and long-term stability.This thesis has completed the hardware and software design based on AD9834 DDS chip and Microcontroller Unit, established on direct digital synthesize technic and digital modulation theory.In the end, this device is able to generate multiple waveforms and is capable of performing several digital modulations with high output signal quality, flexible adjustment methods, low power consumption and small-sized features.The specific research content of this thesis is as follows:

First of all, this thesis has a deep dive into direct digital synthesize technology about its operating theory and features, including the sampling output characteristics of the sampling system and the reconstruction filter design of the DDS output signal.This thesis also analyzed factors which affects DDS output spurs such as oversampling, phase truncation error and reference clock signal.Furthermore, this thesis analyzed how to optimize DDS design according to the characteristics of the DDS to get higher quality output signals.Then the application of the DDS in digital modulation is analyzed, including linear and non-linear modulation, chirp signal, multi-symbol modulation and QAM.

Afterwards, this thesis finished the software logic design of the signal generator.The flexible control and interaction of the system is achieved through Finite-State-Machine logical design method, which realized multi-symbol FSK,PSK,ASK, Chirp signal, single tone sine signal and triangle waveforms output capabilities.

Finally, this thesis has a detailed analysis of the generated single tone sine signal, Chirp signal and so on.In the mean time, power consumption test is also conducted.It turns out that the signal generator designed in this thesis possess the features including high output signal quality, flexible adjustment methods, low power consumption and so on.The signal generator designed in this thesis has met the design requirements and can be better applied in practical engineering fields.

Keywords: Direct Digital Synthesize, Signal Generator, Digital Modulation, Easy to Integrate, Low Power Consumption

第一章:绪论

1.1-研究背景及意义

这一部分有一些胡诌的成分。。毕竟。。写过论文的都懂啦

信号发生器(Signal Generator)是一种能提供各种频率、波形和输出电平电信号的设备。在测量各种电子系统或通信设备的振幅特性、频率特性、传输特性及其它电参数时,以及测量元器件的特性与参数时,信号发生器通常被用作测试的信号源或激励源。

在设计、开发通信系统的硬件电路时,工程师往往需要一个灵活捷变的信号源来加速电路与算法验证的过程,它能够产生工程中常用的调制信号类型,具有基带信号、时钟信号、同步信号的输入输出接口,同时可以方便地调节各项信号参数与指标。传统的信号发生器以振荡器配合部分模拟电路作为信号源,难以实现在灵活调节各项参数时保证输出信号的高质量,相比于数字型频率合成器(DDS),模拟式信号发生器虽然杂散可以做到较低,但在频率控制灵活度和频率稳定性上表现不佳,且难以实现相位连续。全数字化的DDS也非常便于集成到数字系统中,可以显著降低系统复杂度,同时提升系统可靠性和长期稳定性。因此有必要对基于DDS的信号发生器进行研究。

目前快速发展的通信技术对信号源的要求越来越高,从商用的通信基站到雷达系统、精确制导武器的控制系统等电子系统都需要高精度与高度灵活、小体积、低功耗的信号发生源,而DDS的发展正迎合了这些需求,DDS已然是通信电子系统中必不可少的一环。

这项研究有利于全面认识DDS器件的特点及其应用,也可以丰富目前关于DDS及信号发生器的研究,同时也能促进相关技术的进一步深入研究和发展。

1.2-信号发生器的研究现状

最早商用的信号源诞生于1928年,它能够输出500Hz到1.5MHz的信号。20世纪40年代出现的晶体管大大促进了信号源的发展。随着电子技术的发展进步,信号源现在已经衍生出很多种类型,包括函数发生器、任意波形发生器、射频、微波信号源、矢量信号源、数字序列发生器等。而信号源的带宽也大大扩展,从极低频至高达毫米波段都有相应的产品诞生。国外的知名电子测试测量仪器公司如Keysight、Tektronix、Rohde $\&$ Schwarz所设计的信号源达到了相当高的水平,如Keysight公司的PSG系列信号发生器,可覆盖100kHz至70GHz的频率,具有极低的相位噪声,同时具有高达4GHz的IQ调制带宽,配合频率选件可将输出频率拓展至1.1THz。同时Keysight使用定制的DAC-ASIC,实现了高达256GSPS采样率的RF DAC,以此为核心构建出的M8199A任意波形发生器具有256GSPS采样率、高达80GHz模拟带宽。

国内此方面的研究起步较晚,目前国内利用新技术设计并制造的高性能信号发生器已能追赶上国际先进水平,比如中电科仪器仪表公司设计的1465型信号发生器能实现100kHz至67GHz的宽频率覆盖,同时具有极低相位噪声。普源精电公司设计的DG70000系列任意波形发生器具有最高12GSPS的可变采样率,5GHz带宽,16bit垂直分辨率。但是距离国外先进技术仍有不小差距。

现代信号发生器多数依赖于DDS技术,在低频段可用DDS直接输出,在射频与微波段可利用DDS搭配PLL产生GHz以上的信号。目前,各大模拟芯片厂商都有高度集成化的DDS芯片产品,所以可以直接将DDS芯片集成进信号发生器中,作为核心信号源。 应用最广泛的DDS芯片是Analog Devices公司生产的AD983x、AD985x、AD995x等DDS系列芯片。最近推出的AD9177是一款具有宽带信道选择器的四路、16 位、12 GSPS RF DAC,通过具有JESD204C高速接口的FPGA与此类DAC组合就可以很方便地实现高速任意波形发生器。而其他标准型DDS芯片如AD9854/AD9852等,只需通过低速串行接口(SPI)为其写入配置和工作模式即可完成DDS的全部功能。

现阶段的数字信号源的最大的缺点是频谱纯度不高,由于相位截断误差、DAC器件的非线性误差、数字波表的量化误差等因素影响,输出波形难免会有非线性失真,从而难以得到高纯度频谱的输出信号。未来的信号源将对于细频率步进、低相位噪声、高频谱纯度与频率捷变提出更高的要求,采用单一直接数字频率合成技术是无法完成满足这些需求的信号源设计的,所以未来的信号发生器将在架构上革新,采用多种频率合成技术(如PLL、DDS、倍频/分频、混频与数字变频)组合使用以此产生相位噪声和杂散成分更小、跳频速度更快的信号。

1.3-论文研究内容

本研究以通信电子电路与雷达发射机为背景,为了得到可用于通信发射机系统测试用的调制信号,需要一个能够产生ASK、FSK、PSK、Chirp等调制信号和单频信号,同时具有扫频、快速跳频功能的信号发生器。

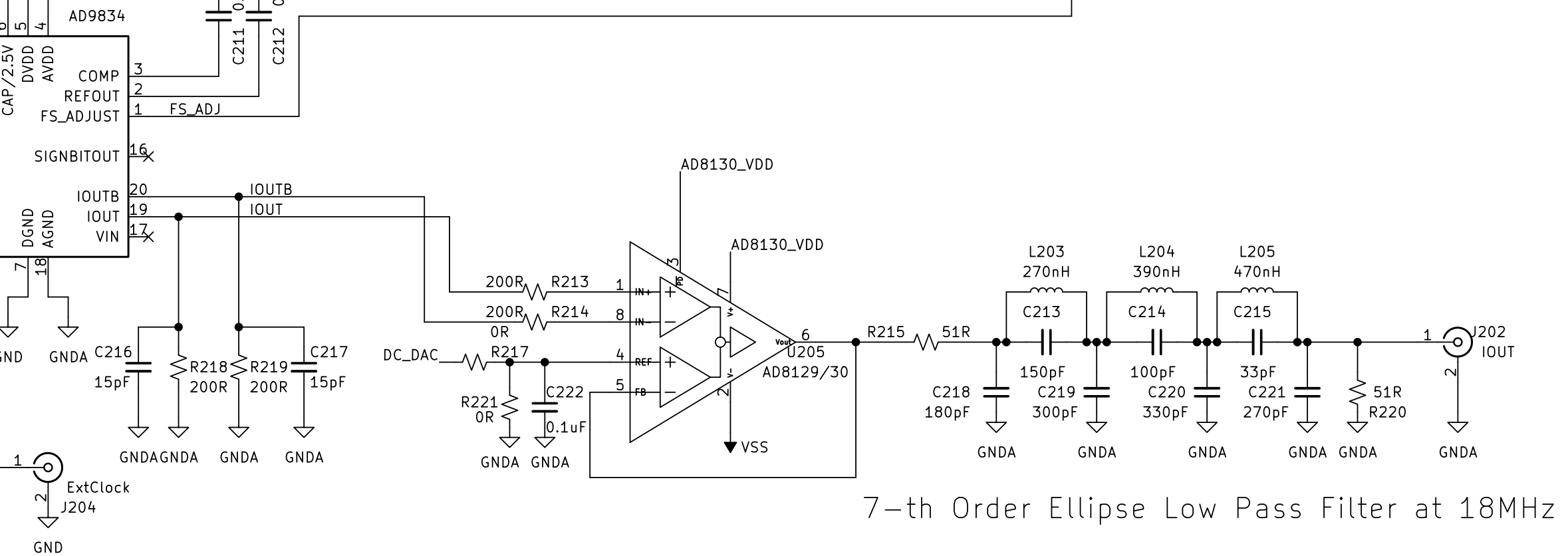

在分析了常用的几种基带调制信号原理和直接数字频率合成原理等相关内容后,本研究利用Analog Devices公司的AD9834 DDS芯片和32-bit ARM Cortex M4核心的MCU设计并实现了一个可输出多种调制信号,满足上述需求的信号发生器。AD9834是一个低功耗(3V供电时仅20mW)、75MHz完整DDS芯片,能够产生高性能正弦波和三角波输出,片内集成比较器,可用于方波输出。同时AD9834支持相位调制和频率调制功能,其内部相位累加器长度为28位,即在75MHz下运行时频率分辨率为0.28Hz。在1MHz运行时,其频率分辨率为0.004Hz。AD9834提供三线标准SPI接口,可以方便地与MCU连接,同时具有硬件休眠控制功能,不用时可以禁用AD9834以节约能耗。在AD9834输出后设计一七阶无源椭圆滤波器,-3dB带宽18MHz,输出信号最高hz,频率可达15MHz,后接一低失真运算放大器缓冲器,可以输出高品质频谱性能的信号。使用电压输出DAC器件控制AD9834的Full-Scale范围,可以轻松实现幅度调制。

单片机外设主要有:LCD显示器、旋转编码器、按键键盘与DDS、DAC,用户可方便地使用键盘或旋转编码器输入信息,设定指定的输出模式和信号参数。同时显示器负责将当前的工作模式与信号参数显示,以便用户查看、修改。DDS作为主要的信号源,而DAC负责控制DDS的输出峰峰值幅度,同时也在振幅调制模式下作为振幅调制源。

第二章:DDS频率合成技术

2.1-DDS技术原理

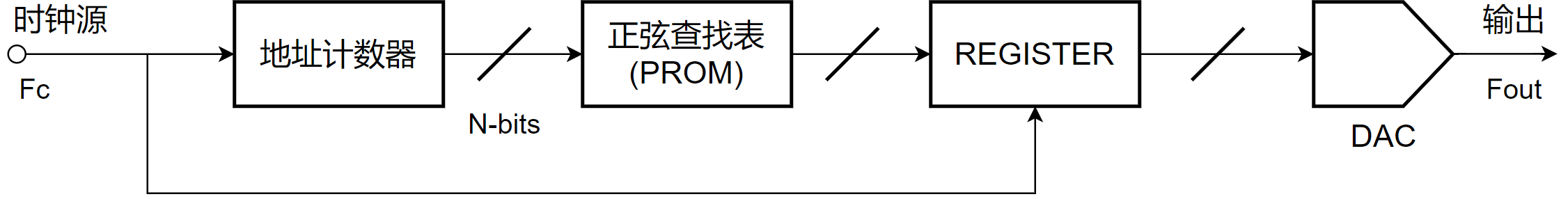

DDS(Direct Digital Synthesizer)是一种频率合成技术,用于从单一(或混合)的频率源中产生任意波形。目前,从低频到百MHz的正弦波与三角波的生成,多数都采用DDS芯片完成;在成熟的信号发生器中,DDS架构也是其核心技术。一个简单的DDS架构如图2.1所示:

图2.1-简单DDS架构

一个正弦波的单个完整周期的幅度字数据被存储在可编程ROM中(PROM),即 图2.1 中的正弦查找表;地址计数器在时钟作用下递增计数并遍历正弦查找表中存储的数据(等效正弦幅度字),然后该数据被送入高速D/A转换器执行数模转换,输出与查找表中幅度字对应的完整的正弦波信号。虽然这样的简单结构能够输出性能优异的模拟信号,但是这样的结构并不能灵活地改变频率和相位,如果需要改变输出信号频率,只能通过更改时钟频率或者重新烧写PROM中的正弦查找表。

在该数字信号链中使用相位累加器便可解决灵活调节频率和相位的需求。这种架构使其变成了一个数控振荡器,成为了高度灵活的DDS核心结构,如 图2.2 所示。在该架构中,寄存器在正弦查找表之前接入信号链来代替地址计数器,反馈回路可让此结构形成DDS中的“相位环”。当相位累加溢出时,相位寄存器索引自动转入原点后重新开始累加,实现循环查找输出。

图2.2-高度灵活的DDS架构

在这种架构中,输出频率的计算公式由下式给出:

F_{out} = (M(REFCLK)) / 2^N其中:

F_{out}为DDS最终输出频率M为二进制调谐字REFCLK为内部参考时钟(也即系统时钟)N为相位累加器的位长(24-48 bits)

2.2-DDS的采样输出特性

2.2.1-DDS的输出特性

由于DDS的输出器件为DAC,而DAC是采样转换系统,所以DDS也是典型的采样转换系统。分析DDS的输出信号特性时,采样理论分析是必不可少的。

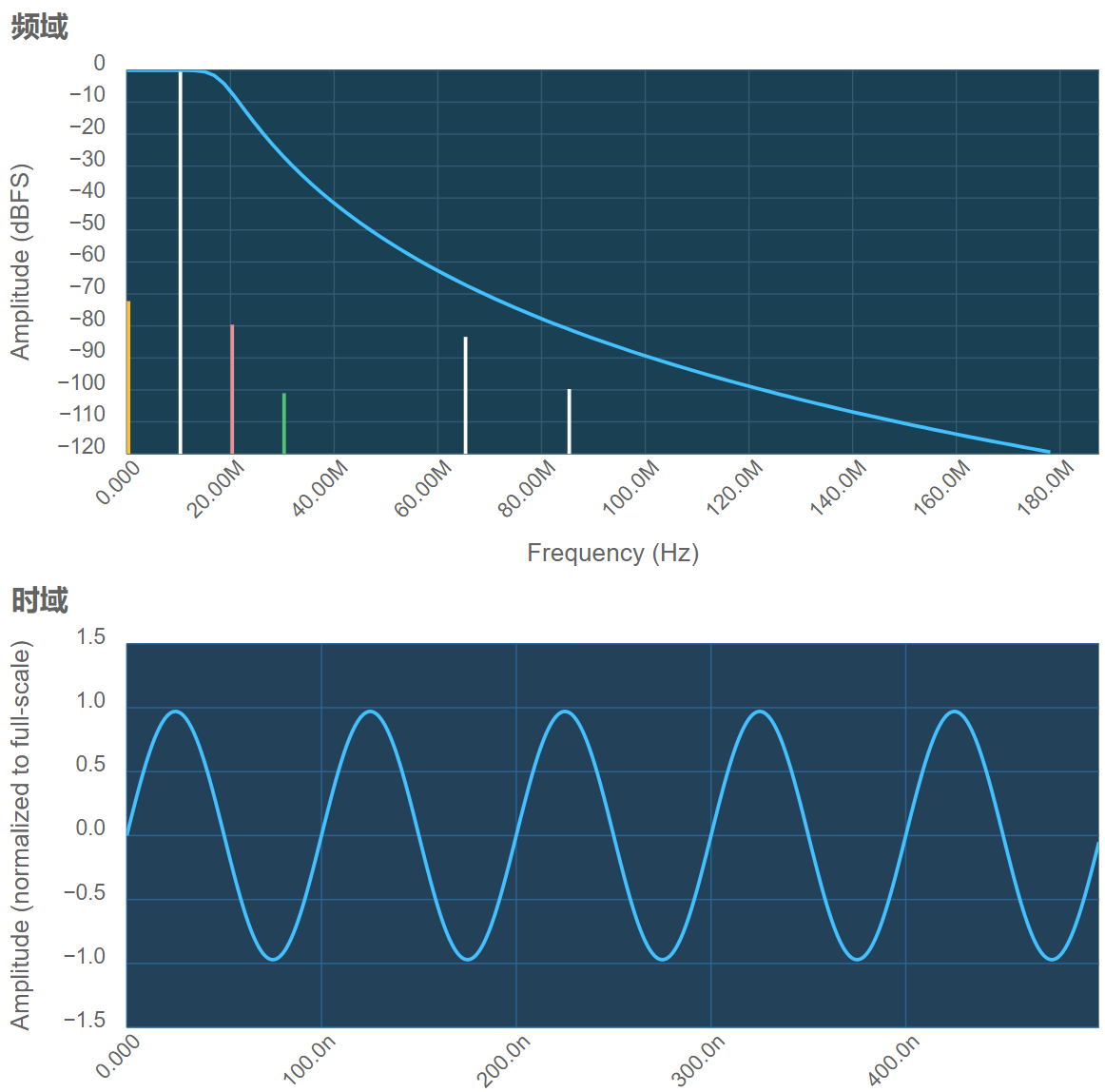

图2.3-采样输出的频谱成分

采样输出的信号频谱如图2.3所示。在这个例子中,假设采样时钟 f_{CLOCK} 是300MHz,输出信号的基波频率 f_{OUT} 是80MHz。可以看出,输出信号的频谱结构具有 \sin x/x 包络形状,奈奎斯特极限频率是时钟频率的一半,也就是150MHz,左边阴影区域为奈奎斯特带宽。

奈奎斯特采样定理指出,在DDS这样的数据转换器系统中,一个周期内至少需要2个采样点才可能重建出期望的输出波形。DDS的输出频谱中含有镜像频率,镜像频率的值由 f_{CLOCK} ± f_{OUT} 决定。第一镜频响应在 f_{CLOCK} - f_{OUT}=220MHz处出现,第二、三、四、五镜频在380MHz,520MHz,680MHz,820MHz处出现。频谱图中,采样频率的整数倍处出现零点。当输出频率超过了时钟频率时,第一镜频将作为混叠镜像出现在奈奎斯特带宽内(DC-1/2f_{CLOCK}),混叠镜频将不可能使用传统的奈奎斯特抗混叠滤波器滤除。

在上面的频谱图中,f_{OUT}和各个镜频的幅度分布符合 \sin x/x 滚降响应,这是由于采样输出的量化性质(采样信号是一个冲激信号,其频谱为sinc函数)。输出的基波和任意给定的镜像频率的幅度均可使用 \sin x / x 公式来直接计算得出。根据滚降响应函数,基波输出的幅度将与设定的调谐频率的增加成反比——DDS系统的输出从直流到奈奎斯特带宽的幅度滚降是-3.92dB。所以在设计以DDS为核心器件的信号源时,需要注意在奈奎斯特带宽内的幅度滚降。有的DDS器件内预置了反SINC滤波器,它可以在数字域中针对DDS的采样输出特性作出预补偿,从而在输出的 80\% 奈奎斯特带宽内得到非常平稳的幅度滚降响应(滚降起伏小于0.1dB)。

2.2.2-DDS输出后级滤波器

在典型的DDS应用中,通常在DDS输出接上一个低通滤波器(LPF)来衰减输出频谱中的镜像频率成分。为了确保低通滤波器的截止频率在合理的范围内(通常设计滤波器时需要综合考虑滚降速率和带内起伏等因素)。约定俗成的规则是将DDS输出带宽限制在 0.4倍时钟频率 内。(如果时钟频率为300MHz,那么输出频率范围对应为 300*0.4=120MHz ),这有助于使用低成本的低通滤波器实现。图2.4是一个在DDS输出应用低通滤波器的示例,系统时钟频率为75MHz,设定输出信号频率为10MHz,滤波器为6阶巴特沃斯响应型低通滤波器,截止频率为18MHz,可以看出,DDS输出的高频镜像频率和后级差分驱动器产生的非线性失真成分(2次、3次谐波)得到了很大的衰减,时域波形也无明显失真。

图2.4-为DDS输出应用低通滤波器

2.3-DDS的杂散性能

一个DAC器件的分辨率由其输入的数据位数决定。由于DAC器件分辨率有限,在执行数字域到模拟域的转换过程中不可避免地会引起量化误差,并引起量化失真效应。DAC输出中存在快速变化的边沿信号,这些快速的边沿信号引入了相对于输出信号基波的高频成分,这些高频成分是量化失真的主要原因。在频域中,量化失真误差在奈奎斯特频带内与有用信号混叠,在DAC输出频谱中显示为离散的杂散成分。

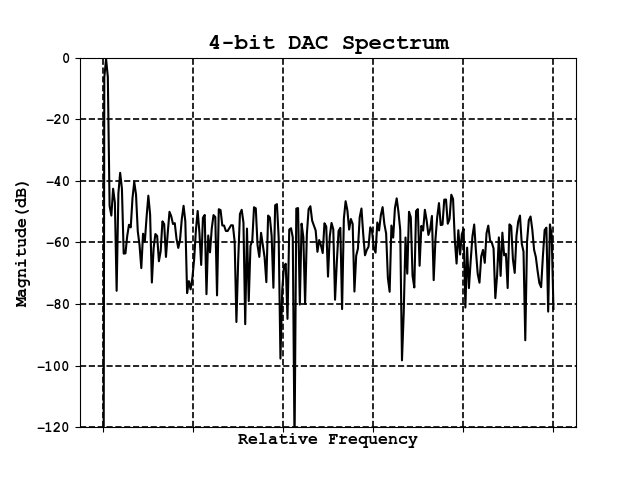

随着DAC分辨率的提高,量化失真效应随之降低,也就是DAC输出频谱中的杂散成分降低。图2.5 与图2.6对比了4位和8位DAC输出单频正弦波时的频谱成分,可以看出DAC转换分辨率提升带来的杂散性能提升是非常显著的。

图2.5-4-bit DAC输出频谱

图2.6-8-bit DAC输出频谱

实际上,DAC分辨率和杂散之间的关系可以精确量化。若DAC工作在满量程输出情况下,那么输出信号的功率与量化噪声信号功率之比(SQR)可由下式给出:

SQR = 1.76 + 6.02B(dB)其中, B是DAC的分辨率位数。8位DAC的 SQR=49.92dB。但SQR计算公式仅仅描述了由量化误差引起的噪声,并不提供任何关于杂散分布或最大杂散电平的信息,只有所有杂散相对于基波的总功率。同时,该公式成立的条件是DAC工作在满量程输出状态。关于SQR第二点需要考虑的是,它仅仅描述了DAC工作在满量程输出时的性能,当DAC工作在小于满量程输出的情况下时,基波幅度将减小,而量化误差却保持不变。这样引起的后果是量化噪声相比于基波信号变得更为显著。DAC工作在非满量程时的误差可以量化为:

SQR = 1.76 + 6.02B + 20 \lg(FFS) (dB)其中,FFS是DAC工作的满量程的分数(几分之几),如果一个8位DAC工作在满量程输出的70\%,那么这将导致SQR降低3.1dB,变成46.82dB。

2.3.1-过采样对杂散性能的影响

在一般的数据转换器系统中,使用比奈奎斯特定理所要求的采样频率更高的采样频率被称为过采样(OverSampling)。奈奎斯特采样定理要求被采样信号的带宽不得超过采样率的1/2。如果故意使采样信号的带宽限制为奈奎斯特要求的一小部分,则采样率超过奈奎斯特要求,这时便为过采样。

图2.7展示了过采样如何提高SQR。量化噪声总功率大小取决于DAC的位数,也就是分辨率。它是一个固定的量,与阴影面积成正比。过采样时,总的量化噪声功率与奈奎斯特采样时的总量化噪声功率是相等的,既然总量化噪声功率在所有情况中是相等的(是常量),而且“噪声矩形”与噪声总功率相对应,那么“噪声矩形”的高度随着采样率的升高而降低,过采样时噪声矩形的高度远小于奈奎斯特采样时的高度,这样才能保持矩形面积不变。

于是在使用过采样时,落在奈奎斯特频带内的噪声功率大幅下降,这样就提升了总信噪比。

图2.7-使用过采样提高SQR

在实际使用DDS时,如果对输出波形的杂散性能和频谱纯度有较高要求,可使用支持高频参考时钟输入的DDS芯片,参考时钟的频率相对于输出信号越高,过采样倍率越高,对量化噪声的衰减就越大。

2.3.2-相位截断误差对杂散性能的影响

相位截断误差是非常复杂且难以分析的,这里我为了控制篇幅,只简单介绍了一下。

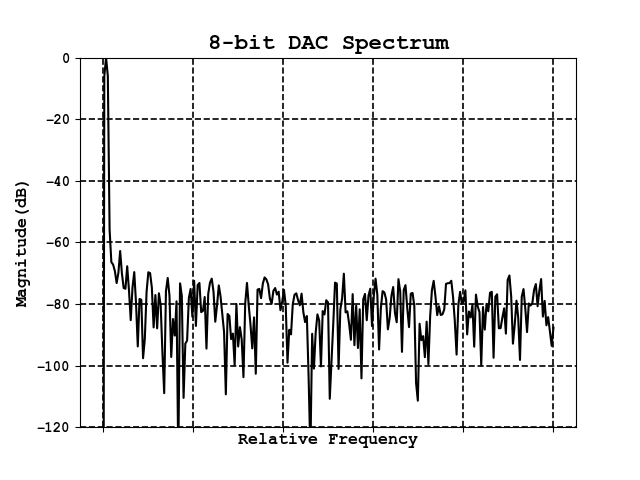

相位截断是DDS中重要的概念之一。如果使用32位的相位累加器,那么直接将32位相位查找表转换为幅度信息,需要2^{32}个存储单元。假设每个相位存储数据是8位字长,那么总共需要消耗4GB的存储空间,很显然在单个DDS芯片中设计4GB的存储器是不现实的。解决方法是使用相位累加器的最高有效位的截断结果,比如在32位DDS的设计中,每个32位中仅仅最高12位作为提供相位信息的有效位,低20位被截断。

为了便于图示,假设一个简单的8位DDS架构,用高5位截断信息来表示数字相位信息,数字相位环如图2.8所示。采用8位相位累加器的DDS的相位分辨率是一整圈的1/256,也就是360°/2^8=1.41°。在图2.8中,外圈细密的点之间的角度差表示相位累加器的相位分辨率,内圈稀疏的点之间的角度差表示相位累加器被截断后的相位分辨率。被截断后,相位分辨率变为360°/2^5=11.25°。

图2.8-8位数字相位环与相位截断(5位)

现在假设我们将相位调谐字设置成6,即在数字相位环中每次计数增长6,如图2.8所示,相位累加器的累加精度由外圈3个相位值标住,同内圈截断后的5位数字相位值相比,误差分别表示为E1,E2,E3,其数值分别为1.41*6=8.46°,1.41*4=5.64°,1.41*2=2.82°,而在第4个相位值处,相位累加器的相位值和截断后的5位数字相位值刚好相等,此时没有误差。以此类推,这些误差随着相位累加器不断增加计数而周期性变化。很显然,对相位累加器作截断必然会导致与DDS密切相关的相位-幅度转换环节出现误差。相位截断误差是可预测的,因为无论选择了什么相位调谐字,随着数字相位轮的不停转动,截断前后的数字相位值总会在零相位点,也就是相位环的原点出现重合,因此这些幅度误差在时域中是周期性的。所以在频域中,这些误差会表现成固定频谱成分的杂散信号,也即相位截断误差。相位截断误差由3个参数决定:

- 相位累加器大小(A bits)

- 相位调谐字大小(P bits)(相位累加器截断后的大小)

- 相位调谐字(T)

部分调谐字完全没有相位截断误差,而其他的调谐字或多或少地存在着相位截断误差。如果A-P的值(相位累加器截断后丢弃的位数)大于4(通常DDS都满足此条件),那么最大的杂散幅度非常接近于-6.02P (dBc)(低于输出基波的幅度)。例如一个相位调谐字为12位的32位DDS器件所产生的相位截断误差总是小于 -72dBc。

当调谐字与相位累加器大小满足下式时,将使DDS输出的相位截断误差达到最大值:

GCD(T, 2^{(A-P)}) = 2^{(A-P-1)}其中,GCD(X,Y)函数代表X和Y的最大公约数。当调谐字与相位累加器大小满足下式时,将使DDS输出的相位截断误差达到最小值:

GCD(T, 2^{(A-P)}) = 2^{(A-P)}2.3.3-参考时钟对信号质量的影响

由于我写论文时没有能测试时钟相位噪声和抖动的仪器设备,所以论文工作中没有详细的该部分分析。我copy一些ADI的工作放上来。

为了在模拟域中精确地定位数字相位步长,所使用的数模转换器必须满足2个条件:

- DAC输出幅度准确

- DAC在正确的时刻输出正确的信号

其中,令DAC器件满足输出精度要求是容易达到的;使DAC在正确的时刻输出正确的信号,这取决于DAC参考时钟的质量,所以DDS输出的信号质量直接取决于DDS的参考时钟信号。参考时钟信号的重要的参数有如下:

- 频率稳定性,单位

ppm(百万分之一) - 边沿抖动,单位

ps/ns - 相位噪声,单位

dBc/Hz

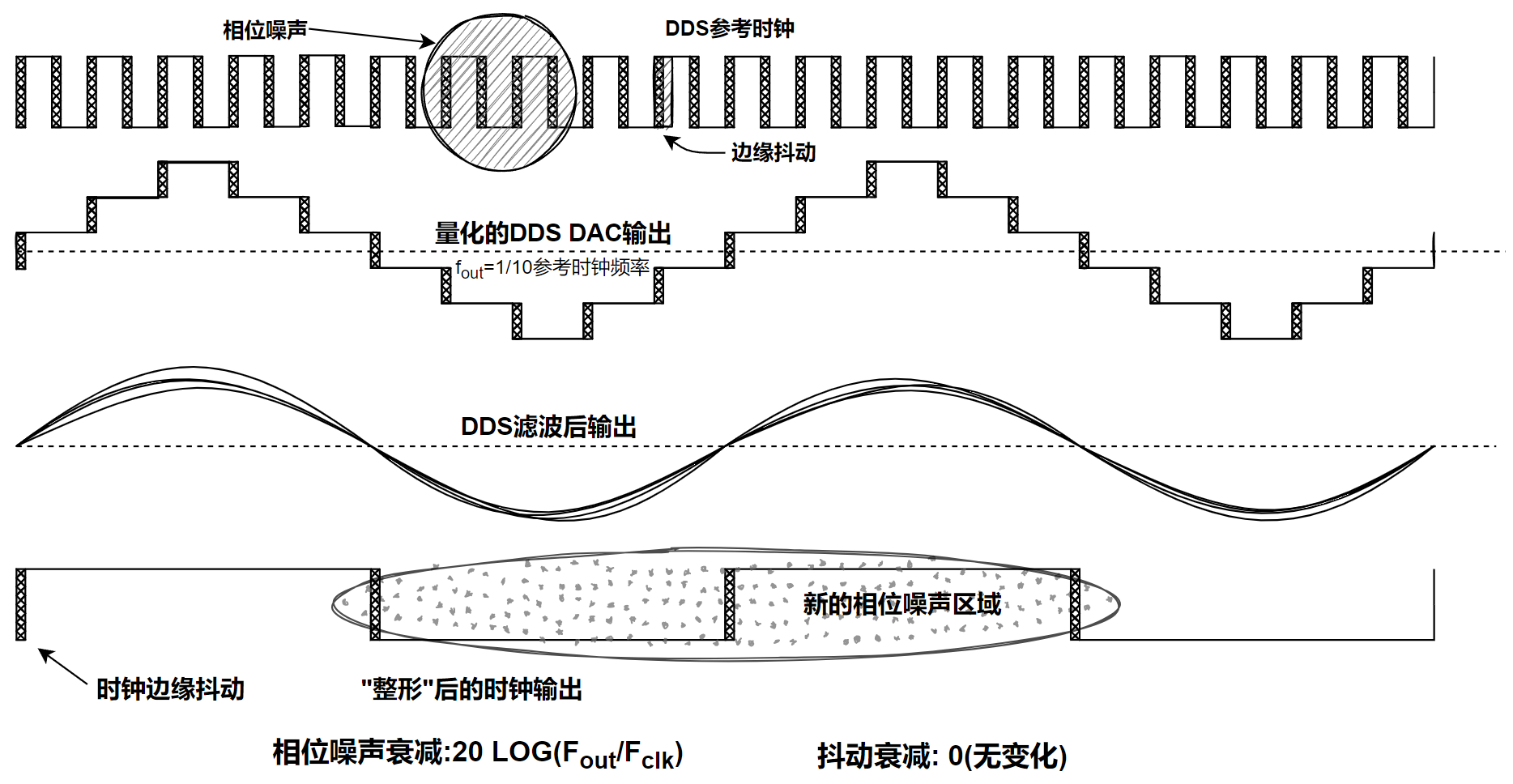

其中相位噪声实际上是根据 20\lg(F_{OUT}/F_{CLK}) 降低的。比如10MHz的输出信号的相位噪声将比"创造"它的100MHz的参考时钟的相位噪声少20dB

图2.9-参考时钟对DDS信号质量的影响

图2.9展示了相位噪声(时域中表示为以百分比为单位的周期抖动)与波形周期的关系,并且绝对边沿抖动不受频率或周期变化的影响。比较"DDS参考时钟信号"与"整形后的时钟输出"信号,可以发现边沿抖动在前者的一个周期中所占的比例远高于后者。这说明了通过分频改善相位噪声的原因,即分频前后的信号周期中都存在着相同量的边沿抖动,而该边沿抖动对高频信号的影响远大于对分频后的低频信号的影响。

由于相位累加器的步进长度由频率调谐字(Frequency Tuning Word)设定为定值,并且无论时钟质量如何,都以极高的精度进行"数学"加法操作,所以参考时钟的边沿抖动不会影响相位累加器的相位步进精度。

2.3.3-ext-扩充内容-频谱测量实例

ADI的完整DDS芯片提供一个大致精确的DAC将数字相位步长转换为模拟电压或电流输出。但这仅仅是一部分工作,另外的还有——为了重建完整的正弦波,需要精确的时钟步进来为DAC提供时钟。而这里的时钟就需要满足我们之前提到的种种需求了:超低边沿抖动、低相位噪声…

在频域中,DDS输出的相位噪声相对于参考时钟的相位噪声的提升则更为明显了。下图(Fig.5-2)是频谱分析仪测量的2种不同的DDS参考时钟的相位噪声。其中参考时钟2的相位噪声与边沿抖动性能远比参考时钟1要好。

/6.jpg)

Fig.5-3展示了使用上述2种不同的时钟作为同一DDS器件的参考时钟(100MHz),所测量得到的输出信号(10MHz)的频谱。输出1表明了其输出信号的相位噪声相比于参考时钟信号有20dB的提升(10倍)。输出2展示了相比于其参考时钟信号更小的相位噪声,但由于测量仪器的本底噪声性能不太够,想要像信号1一样测量出20dB的提升有些力不从心了~

有没有注意到输出信号2的频谱中的小幅度的 毛刺?这些杂散信号是由DDS的 相位-幅度转换级 中的相位截断效应和相位-幅度转换的算法误差所致。这些杂散信号同样也存在于输出信号1中,只不过在输出信号1中过多的相位噪声掩盖了他们的存在。这说明了 相位噪声 在输出高质量、高信噪比信号时为何如此重要。

但有时候DDS无法反映输入时钟的质量。比如说,一般 DDS&DAC 贡献的相位噪声大约是 -130dBc/Hz(1kHz载波频偏)。如果参考时钟的相位噪声比-130dBc/Hz更小,那么器件所贡献的相位噪声将会让这个参考时钟的卓越性能白白浪费掉。这项DDS的性能指标叫 "残留相位噪声"(Residual Phase Noise)。无论使用多好的参考时钟源,DDS的相位噪声性能永远也不会超越这个指标。所以不要浪费那么好的晶振哟~

DDS输出信号的总相位噪声是参考时钟 在被DDS分频且增强之后的相位噪声 与 DDS自身的残留相位噪声 之和。再举个栗子,一个参考时钟(振荡器,100MHz)的相位噪声是 -110dBc/Hz@1kHz频偏, F_{OUT} / F_{CLK} = 1/10,因此输出相位噪声被衰减20dB。被衰减了相位噪声之后的参考时钟所贡献的相位噪声的量就变成了 -130dBc/Hz(此时输出频率为10MHz),与DDS器件的残留相位噪声相等,将 -130dBc/Hz 与 -130dBc/Hz相加,结果是相位噪声加倍,变为 -127dBc/Hz。即使你使用相位噪声为 -200dBc/Hz 的参考时钟,最后DDS输出信号的相位噪声也无法比DDS器件本身的残留相位噪声(-130dBc/Hz)更低。

2.3.3-ext-使用DDS内建的倍频器为参考时钟倍频

许多ADI的DDS和数字调制器芯片都有片上的参考时钟倍频电路。这些可以被接入或旁路掉的倍频器,允许使用一个低频外部时钟源来为DDS芯片提供一个高得多的参考时钟信号。这些倍频器可以通过数字编程倍频系数(从4倍至20倍)。这样设计是很有好处的,因为这样就可以使用一个低频时钟来同步多个高速DDS芯片,这有助于简化高速时钟分配与同步问题。如果直接使用一个高频时钟源,系统的复杂度和成本将大幅上升,而在芯片内集成倍频器则可以避免这种问题。

但是参考时钟倍频器并不适用于所有的应用场景。当涉及参考时钟倍频时,都需要在输出信号的质量方面进行权衡。倍频将在PLL环路带宽内以 20 \lg(F_{OUT} / F_{CLK}) 恶化参考时钟的相位噪声(F_out是倍频输出的高频时钟频率,F_clk是参考时钟信号的频率)。又举个栗子,一个6倍倍频器将使一个相位噪声为 -110dBc/Hz的振荡器的相位噪声恶化15.5dB,倍频后的高频信号的相位噪声仅有-94.5dBc/Hz。并且,PLL环路滤波器的特性可能导致在靠近其截止频率时的相位噪声 "突起"。下图展示了典型DDS(AD9851)的输出相位噪声恶化,该器件具有片上完整的PLL环路滤波器。其他的带有片外环路滤波器的DDS设备通常不会在滤波器响应中表现出峰值。

/7.jpg)

2.3.3-ext-DDS的无杂散动态范围(SFDR)性能

使用参考时钟倍频器同样会对 SFDR(Spurious-free dynamic range) 性能产生影响。Figure.5-5展示了同一DDS器件分别使用倍频器和不使用倍频器时输出同一频率信号的频谱图,对比窄带SFDR(±1MHz,其实不窄),使用倍频的输出信号SFDR约为-68dBc,不使用倍频的输出信号SFDR约为-78dBc。同时注意到,前者的本底噪声相比后者也同样升高了不少。

/8.jpg)

即使考虑到性能折衷,片上参考时钟倍频器的良好性能、便利性和节约成本的特性也让其在许多DDS中得到应用(但不是大多数)。然而,为了得到最好的SFDR和相位噪声性能,使用外部高频高质量(低相位噪声)时钟直接作为DDS的参考时钟仍是必须的。

2.3.4-其他影响

在DDS输出信号中还存在其他的微小误差,比如说DAC器件的积分与微分非线性误差、与DAC相关的脉冲(毛刺)能量、时钟馈通噪声等。这些误差通常无规律可言,而且并不遵从\sin(x)/x滚降响应。这些误差分量将在输出信号频谱中以谐波和杂散的形式出现,并且具有比镜频分量低得多的幅度。DDS器件自身的本底噪声(Noise Floor)通常由衬底噪声、热噪声、接地耦合和各种由其他小信号引起的信号质量恶化共同决定。同样的,PCB布局布线、电源质量与电源退耦同样会对DDS输出信号的质量造成很大影响。

2.4-DDS在调制中的应用

得益于DDS器件的高度灵活性,在调制与数据编码系统中使用DDS器件来产生调制信号相比于传统的模拟方法要更为方便。

2.4.1-AM调制

幅度调制(AM)是让载波的幅度跟随基带信号的幅度而变化的模拟调制方法,现推导其数学形式。载波信号频率为f_c,幅度为A,载波信号可表示为式

c(t) = A\sin(2 \pi f_c t)令m(t)表示调制波形(也就是基带信号),载波的频率要远大于基带信号的频率,基带信号可表示为式:

m(t) = M \cos(2 \pi f_m t + \phi)其中,M是归一化的调制幅度,需要保证M始终小于1以使1+m(t)总是正数。若M>1则会出现过调制,一旦出现过调制,将无法从传输信号中重构完整的原始基带信号。幅度调制的最终结果就是载波c(t)乘以正数1+m(t)。

y(t) = [1+m(t)]·c(t) = \\

[1+M·\cos(2 \pi f_m t + \phi)]·A\sin(2 \pi f_c t)运用积化和差恒等式,可以用3个正弦波的和表示AM调制信号,如下式所示:

y(t) = A·\sin(2\pi f_ct)+ \\

{AM\over 2}[\sin(2\pi(f_c+f_m)t +\phi) + \\

\sin(2\pi(f_c-f_m)t -\phi)]因此,调制信号有3个组成部分,分别是载波c(t)、频率略高于载波频率的上边带和频率略低于载波频率的下边带。然而,真正携带信息的只有上下两个边带成分,载波本身并不携带信息,所以标准AM调制的频谱利用率和效率并不高。

在上面的推导中,M等效于调制系数。调制系数表示调制变量在未调制水平附近变化的范围,定义式如下式所示。通常调制系数m以百分比作为单位,若 m=100\%,已调信号的包络线会降到0,也即完全调制。通常为了获取理论上最搞的信噪比,调制系数应该尽可能接近1但是不能超过1。

m = {m(t)_{p-p} \over A} = {M \over A}如果要使用DDS进行AM调制,有两种方法。第一种是控制DDS输出的满量程范围从而实现幅度控制,将基带信号用作幅度控制信号即可实现AM调制。第二种是将频率寄存器写0,然后建立起相位-幅度映射表,将DDS当作一个普通DAC来使用。在微控制器或微处理器中计算AM调制信号的波表,然后对DDS的相位寄存器进行连续写入,也可实现AM调制。

2.4.2-FM与PM调制

频率调制(FM)与相位调制(PM)同属于角度调制。前者使用载波的瞬时频率变化表示信息,后者使用载波的瞬时相位变化表示信息。考虑一FM信号:若基带信号为x_m(t),正弦载波为x_c(t)=A_c\cos(2\pi f_c t),其中f_c为载波的基频,A_c是载波的幅度,调制器将基带数据与载波结合起来得到FM调制信号:

y(t) = A_c \cos(2\pi \int_0^t f(\tau)d\tau) = \\

A_c \cos(2\pi f_c t + 2\pi f_\Delta \int_0^t x_m(\tau)d\tau)上式中,f(\tau)是振荡器的瞬时频率,f_\Delta是频偏,代表在一个方向上相对f_c的最大频率偏移量。数学上,基带调制信号可以通过用频率为f_m的连续正弦信号来近似(单频调制时成立),这个信号的积分可以表示成式(2-12)的形式。这样可将FM调制信号简化表示为式(2-13)的形式。其中,调制正弦信号的幅度A_m通过峰值频偏(又称频率偏移) f_\Delta = K_fA_m表示。

\int_0^tx_m(\tau)d\tau = {sin(2\pi f_m t) \over 2\pi f_m} \cdots (2-12)y(t) = A_c \cos(2\pi f_c t + {f_\Delta \over f_m}\sin(2\pi f_m t)) \cdots (2-13)在模拟域中实现FM调制通常有直接调制和间接调制两种方法;直接调制可以通过将基带信号加载到一个压控振荡器(VCO)上,直接产生FM信号;间接调制则更为复杂。若要在数字域中实现FM调制,通常是在数字信号处理器中进行数字运算后,通过高速DAC将数字FM信号转换到模拟域中。

相位调制的数学表达式由式(2-14)给出。相位调制与频率调制具有相似的数学形式,并且可看作FM的一种特殊情况。

y(t) = A_c\sin(\omega_c t + m(t) + \phi_c) \cdots (2-14)DDS器件由于结构限制,不能直接产生复杂的模拟调制信号。要由DDS器件直接产生FM信号,只能用前述AM的另一种方法,将DDS当作普通DAC使用,在数字域中合成FM或PM信号,建立起相位-幅度映射表后通过DDS的DAC输出调制信号。本研究由于时间限制,没有利用DDS芯片完成FM与PM调制,只完成了AM调制。

2.4.3-数字幅度调制

以ASK(Amptitude shift Keying)信号为例。幅度偏移调制又称幅移键控、幅度键移。ASK通过载波的幅度变化来表示数字基带信号,当基带信号为0时,令载波的幅度为A0;当基带信号为1时,令载波的幅度为A1。如果要在DDS上实现ASK调制,需要能够控制DDS的输出幅度。控制DDS输出信号幅度通常有以下几种方法:

- 改变DDS的DAC的参考电压

- 在DDS数字信号链中,在查找表和DAC输入之间添加数字乘法器

- 在输出级设计程控增益放大器

- 控制DDS的DAC的满量程输出范围

其中前两项是否可行取决于具体的DDS芯片,有的DDS芯片并不支持外部基准,简单DDS芯片也并不具备数字乘法器。

设计连续调节增益的程控增益放大器可采用数字电位器配合运算放大器,或直接用压控放大器实现,但前者要满足对应的带宽需求,对数字电位器提出了较高要求。也可使用模拟开关和运放设计步进调节的程控增益放大器,但灵活性较低,不利于调试与改进。较好的方法是直接控制DDS内DAC的满量程输出范围。多数DDS的DAC都是电流型DAC,因此只需要控制DAC的满量程电流范围即可控制输出的电压范围,间接地实现了幅度控制。这可以利用一个外部DAC器件来实现。

2.4.4-数字角度调制

通常角度调制包括调频与调相2种,以FSK(Frequency shift Keying)信号为例。频率偏移调制,又称频率键移,是一种利用频率差异的信号来传送基带信号的调制方式,FSK和FM类似,不过FM的频率变化是连续的,而FSK则是具有固定频率差异的一系列离散频率值。如果使用键控开关来完成FSK调制,那么需要在电子开关的2个选通端加载2个不同频率的载波信号,然后使用数字基带信号控制电子开关的公共端接通哪一端。这种方法需要2个独立的载波信号,且很难保证FSK调制信号的相位连续性,除非将2个载波信号的相位严格同步。

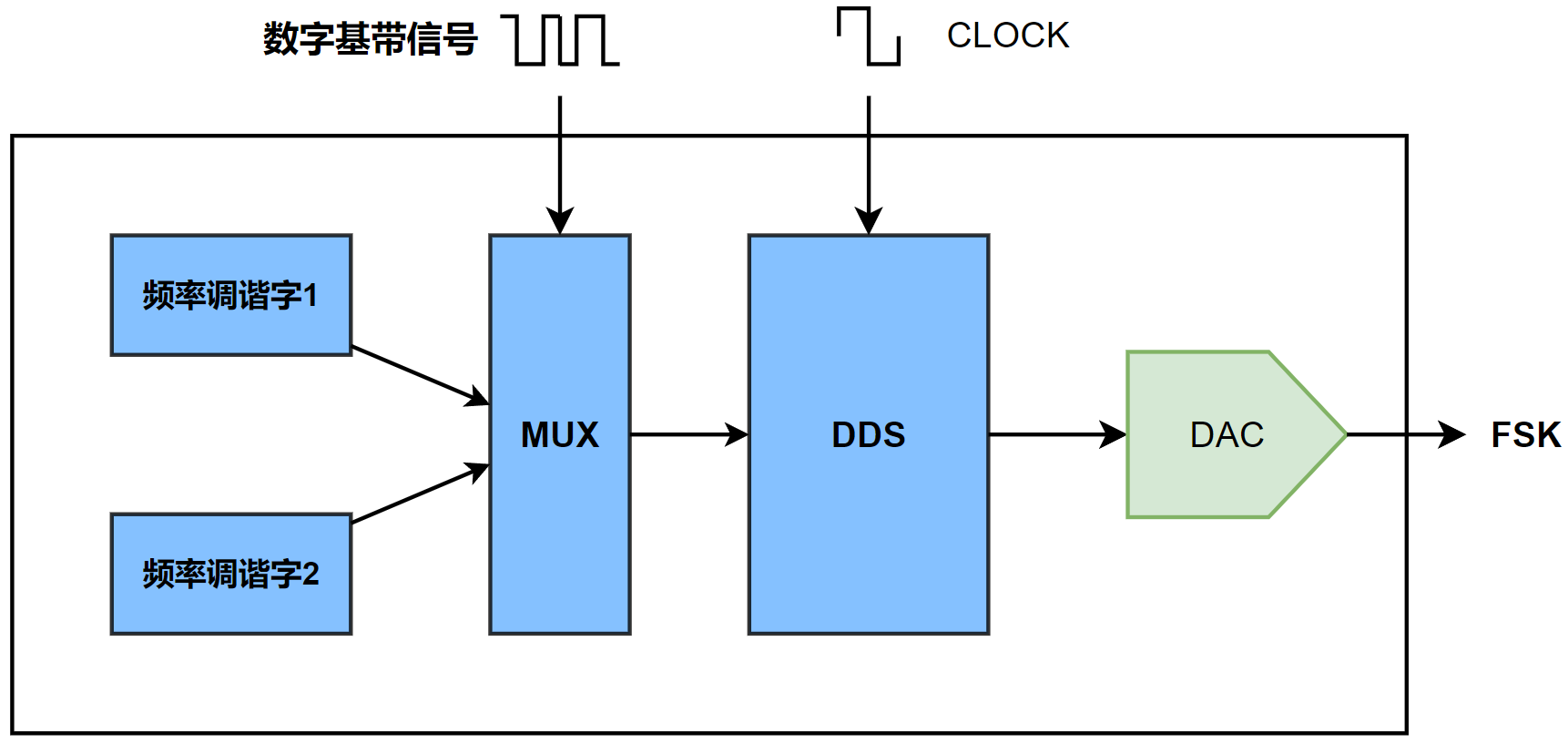

图2.10-使用DDS器件产生FSK信号

DDS器件具有2个甚至更多频率调谐字寄存器,可以预设几个不同的频率调谐字在其中,然后通过MUX来切换使用哪一个寄存器接入DDS信号链中。如果使用DDS器件产生FSK信号,那么只需将2个频率字写入DDS,然后用数字基带信号控制频率字选通MUX,即可输出相位连续的FSK信号。相比于使用键控开关的方法,使用DDS更为简单,更能节省电路板空间、减少电源消耗、简化系统设计。图2.10 展示了DDS器件如何产生FSK调制信号。

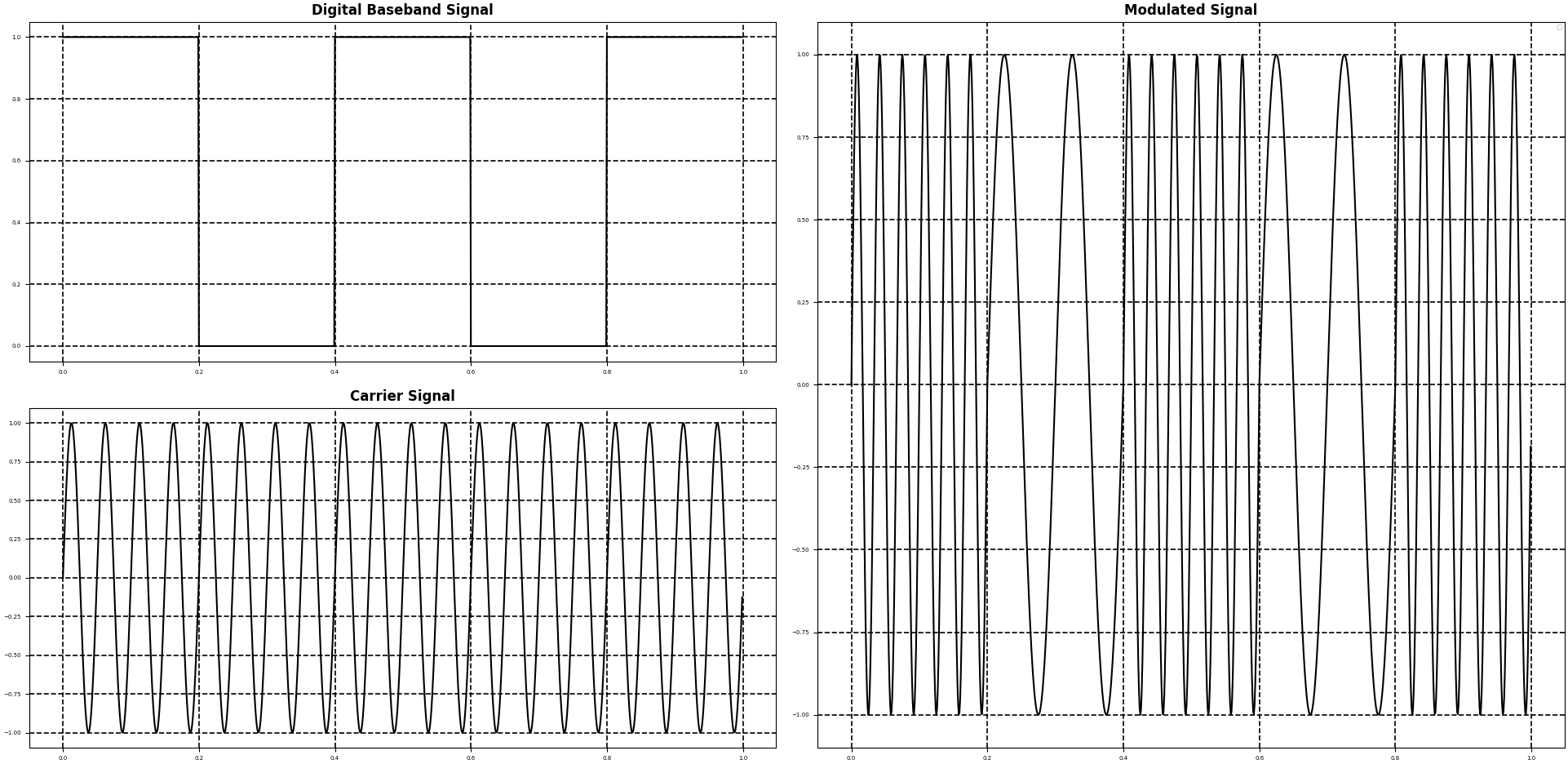

一个相位连续的FSK调制信号如图2.11所示。

图2.11-FSK调制信号

相位偏移调制,又称相位键移(PSK),利用相位差异的信号来传送基带信号,它的特点是载波频率恒定,通过改变载波的相位来传输信息。对于PSK信号,使用DDS产生FSK信号与PSK的区别仅仅在于:前者使用频率调谐字寄存器,后者使用相位调谐字寄存器。

2.4.5-Chirp信号

啁啾(Chirp)是指频率随时间而改变(增加或减少)的信号。其名称来源于这种信号听起来类似鸟鸣的啾声。Chirp信号由于其跟脉冲信号的相关性,非常适合用于无线电和声波探测技术中的脉冲压缩技术上,使用Chirp信号能够使这些系统测量长距离的同时又保持高时间分辨率。所以如何利用DDS器件产生Chirp信号也是非常有价值的研究方向。

传统的Chirp信号产生可以在VCO(压控振荡器)上加载锯齿波产生;也可以在数字域中合成Chirp信号,比如在DSP中直接运算出波形数据,借助DAC器件将其转换为模拟信号;对于DDS来说,改变频率调谐字即可立即改变输出信号频率,所以要利用DDS产生Chirp信号,只需对其频率调谐字寄存器连续写入即可。一个简单的线性增长Chirp信号如图2.12所示。

图2.12-Chirp信号及其时频图、频谱图

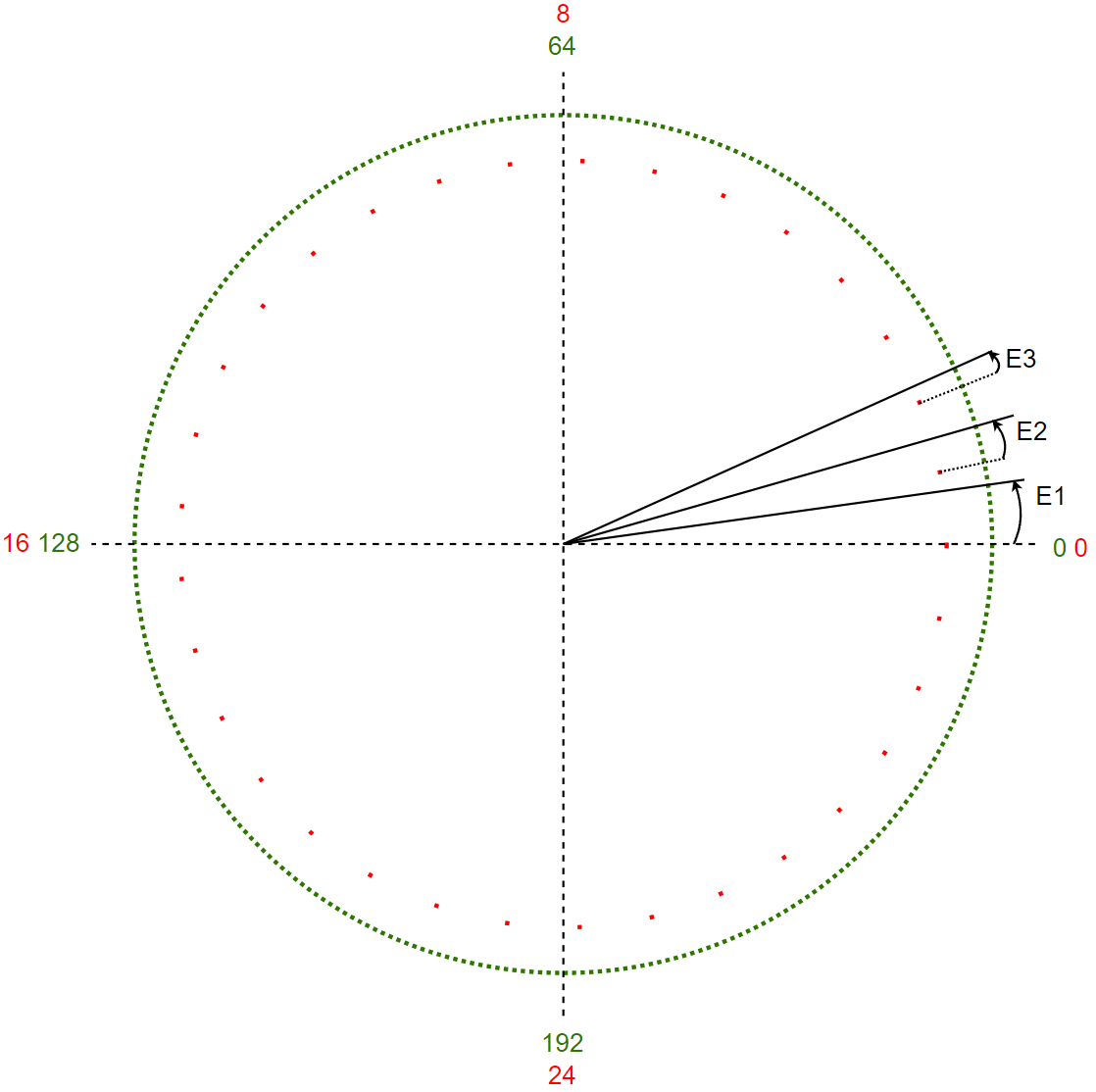

2.4.6-多符号调制与QAM

假如能够连续控制DDS的输出幅度与相位,那么要实现4进制及以上的高阶调制也不再困难。对于2进制PSK,也就是BPSK,相位取值点有2个,它使用两个相位差180°且正交的信号表示0和1;而4进制PSK,即QPSK,通过4个相位并采用格雷码编码信号;QPSK用格雷码对映的方式调制,其误码率将和BPSK一样,所以目前常用的只有QPSK。更高阶的PSK由于其误码率(BER)快速上升而不再实用,更高阶的调制转而由QAM(正交幅度调制)来执行调制工作。

多符号PSK可以用单个DDS通道来实现,可以连续写入DDS的相位调谐字寄存器来不断更新输出信号的相位。如果要实现正交幅度调制,则需要2个DDS通道。有的具有双通道输出的DDS芯片支持正交调制应用,如ADI公司的AD9854,可直接输出I、Q基带信号,借助外部IQ调制器(混频器、90°相移器与加法器)即可实现包含QAM在内的IQ调制。如果采用单通道DDS芯片,可以使用2片同样的DDS芯片,让其被同一外部时钟源驱动,并且同步复位、同步更新调谐字寄存器内容,也可做到让其相位保持严格同步,从而可用于IQ调制应用。使用两片AD9834 DDS芯片实现IQ调制的应用方案如图2.13所示。

图2.13-2片AD9834实现相位同步,进而用于IQ调制

本章小结

哼,最讨厌这种东西了,不写不写就不写。

第三章:硬件方案设计

3.1-设计要求

本研究的目的是制作一基于DDS芯片的低功耗信号发生器,要求能够产生如下信号:

- 单频正弦信号、三角波信号(0-10MHz)

- FSK、PSK、ASK信号(可支持多符号,载波频率可调)

- Chirp信号(线性、对数)

信号发生器需要可以显示当前的设置信息,同时提供用户输入设备以便调节信号发生器的工作模式及工作参数。

3.2-系统架构

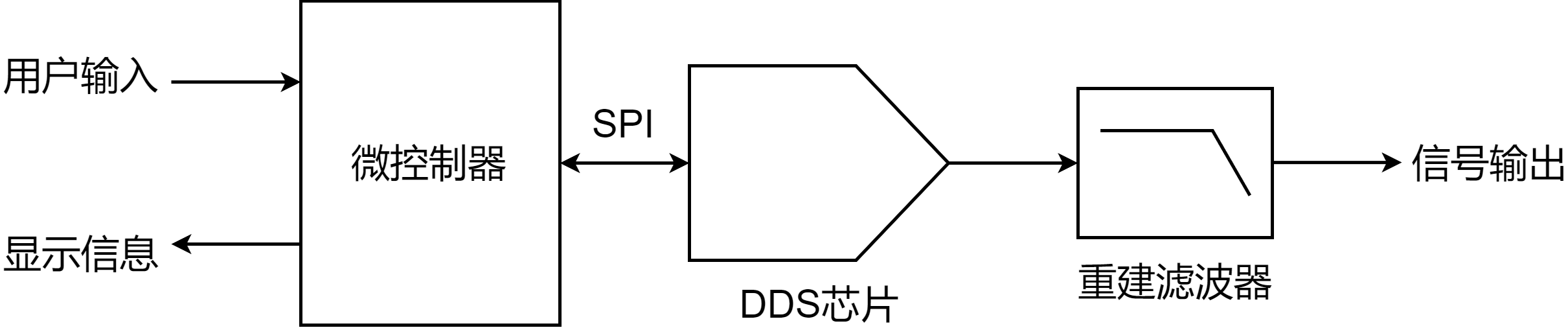

根据论文的要求,信号发生器的设计思路非常清晰简明。微控制器负责控制DDS芯片工作、为DDS芯片输入数据,同时负责人机交互的工作。DDS芯片作为核心信号产生器件,用于将数字波形转换至模拟域,并通过重建滤波器(低通滤波器)重建模拟信号,得到信号输出。图3.1即为简化的系统架构图。

图3.1-简化系统架构

3.3-主要芯片选型

3.3.1-微控制器选型

开始水字数(

划掉)

在现代电子仪器系统中,往往可能包含多个微处理器及微控制器。例如高速示波器中可能包含FPGA和SoC、微控制器等芯片,前者用于采集、存储、处理高速ADC的数据流,后者用于驱动显示屏、接收用户输入信号、控制仪器工作、计算各项参数等;本研究目的是设计一低功耗、小体积的信号发生器,且使用高度集成化的DDS芯片作为信号源核心器件,无需直接驱动高速DAC,仅仅需要通过SPI通信协议配置DDS芯片。故本研究选用一片Cortex M4内核的微控制器(MCU)——STM32L431RCT6作为信号发生器的主控芯片。STM32L431xx系列芯片是基于RISC指令集的ARM Cortex M4内核的超低功耗微控制器产品线,主频高达80MHz。Cortex M4内核带有一个单精度浮点单元(FPU),同时可以执行一整套数字信号处理指令集,并且具有内存保护单元,可增强芯片应用安全性。STM32L431RCT6具备256kByte FLASH存储器、64kByte SRAM内存,片上带有的模拟外设包括1个12位ADC(采样率高达5MSPS)、2通道12位带有输出缓冲器的DAC、1个带有内置程控增益放大器(PGA)的运算放大器、2个超低功耗模拟比较器。通信接口包含3个通信速率高达40MHz的全功能SPI接口及众多I2C和USART等串行通信接口,还包含了14通道的DMA控制器,可以在不阻塞CPU的情况下利用上述模数转换外设进行高速转换及利用通信接口进行高速通信。

STM32L431RCT6的工作电源范围是1.71V至3.6V。功能强大种类丰富的外设、极强的处理器性能、超低功耗的特性使其非常适合应用于本研究的工作中。

3.3.2-DDS芯片选型

若要产生低频到10MHz的信号,那么DDS的主频时钟应该至少大于奈奎斯特频率的2倍即20MHz。同时考虑到采样输出系统的特性,为了确保在工作频带内的幅度平坦度,最高主频应留有一定裕量。在Analog Devices的DDS芯片产品目录中选择下来,比较合适的型号是AD9834。AD9834是20mW低功耗、2.3V至5.5V供电、75MHz的完整DDS,其片上DAC分辨率为10位,窄带SFDR(无杂散动态范围)达到了72dB,提供标准SPI接口,具有休眠功能,非常适合用作低功耗信号发生器的核心器件。

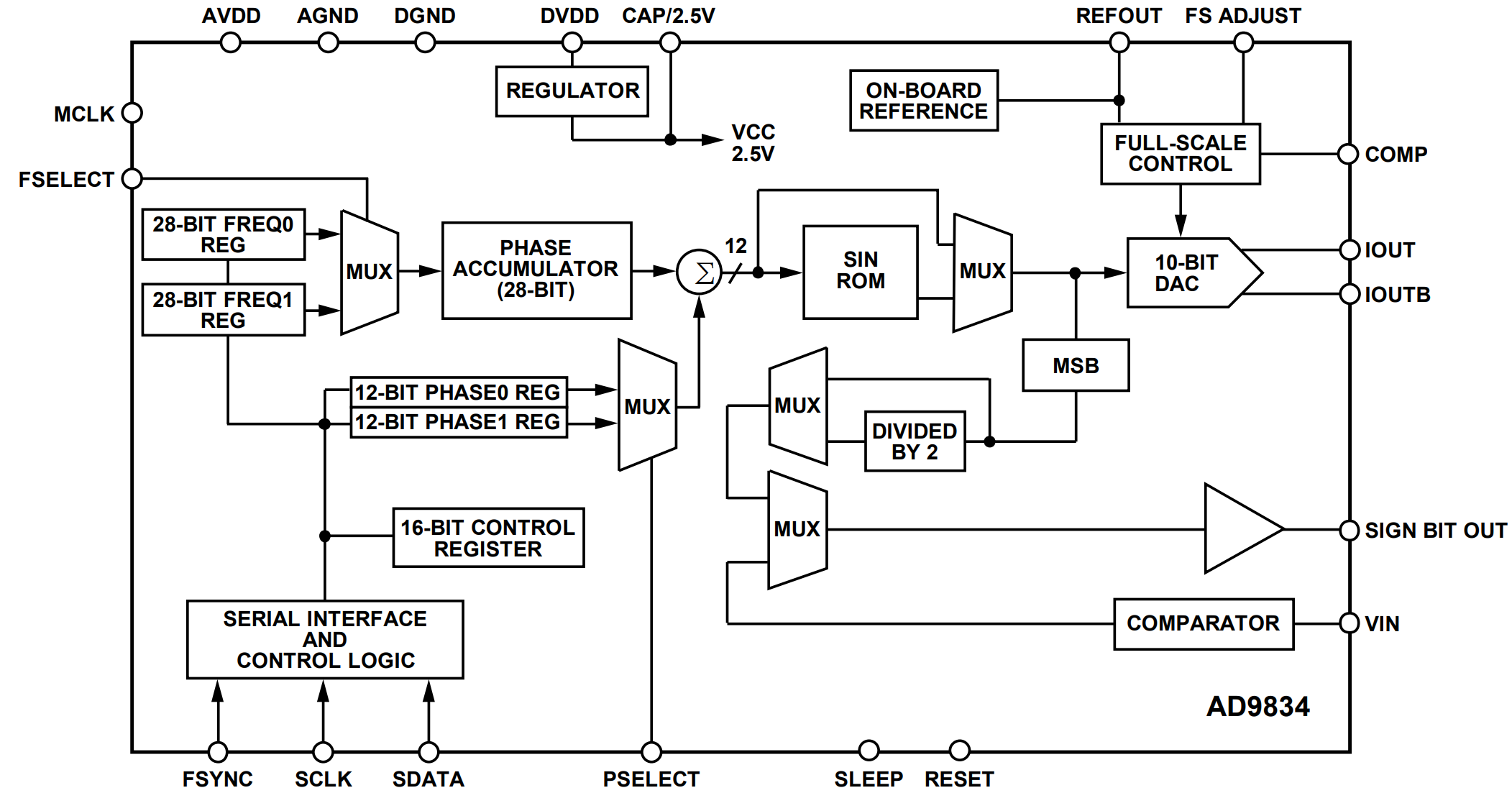

AD9834具有2个28位的频率控制字寄存器和2个12位的相位控制字寄存器,在75MHz主频工作时可实现0.28Hz的分辨率,在1MHz主频工作时可实现0.004Hz的分辨率。该2类寄存器选通MUX同时支持外部信号控制和软件控制,可以方便地利用数字基带信号直接产生FSK、PSK调制信号。AD9834的模拟与数字部分彼此独立,可以采用不同的电源供电,借此可以提高数字域与模拟域的隔离度,提高输出信号质量。AD9834的内部框图如图3.2所示。

图3.2-AD9834功能框图

3.4-硬件电路设计

3.4.1-DDS幅度控制电路

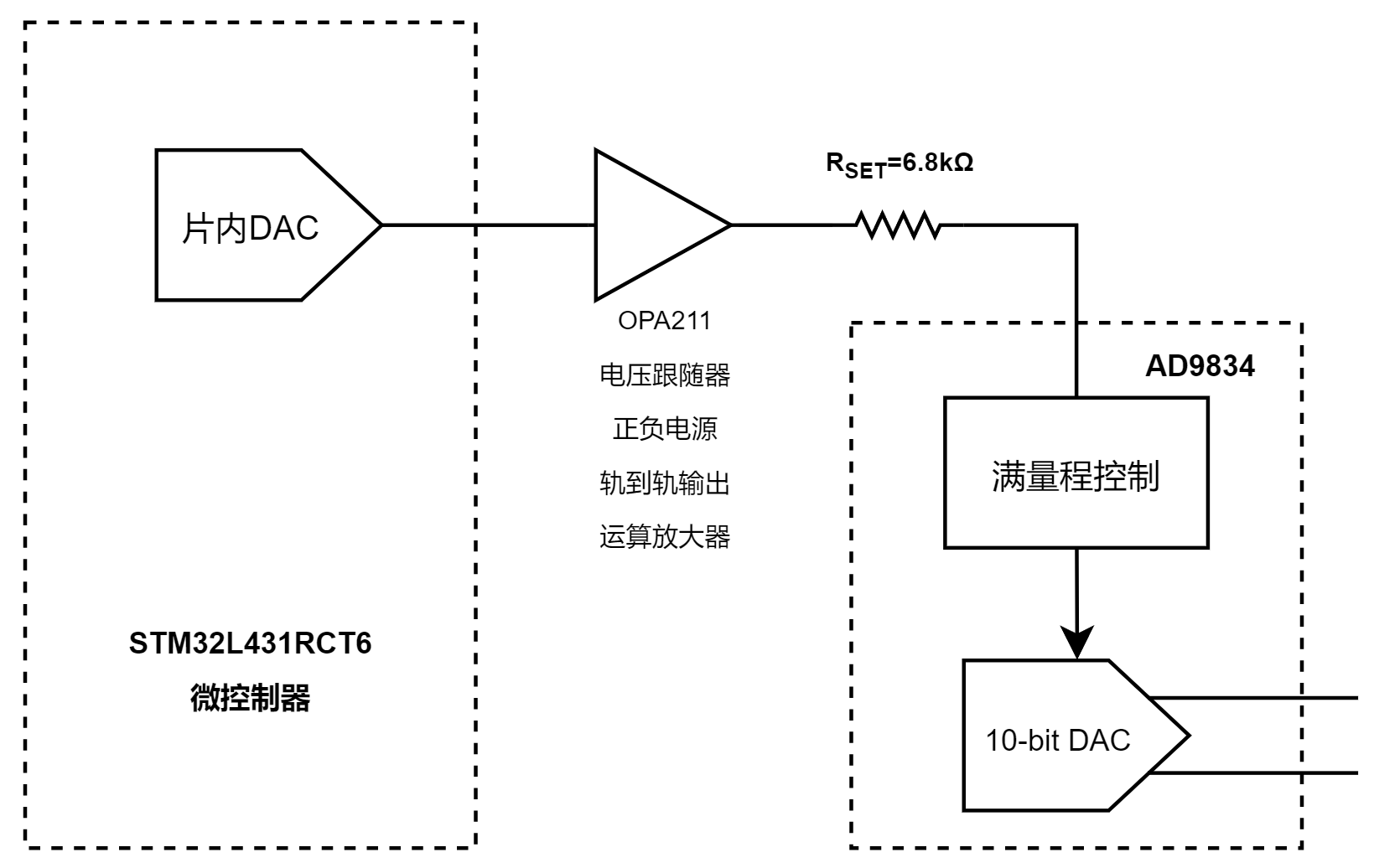

AD9834内置的多控制字寄存器组合可以使其支持频率调制和相位调制功能,但为了调制输出信号的幅度,需要一个低功耗DAC或数字电位器来设置AD9834片内电流型DAC的满量程电流。可以利用一个电压输出DAC,通过串联一个电阻来驱动AD9834的FSADJUST引脚,从而决定满量程DAC电流的幅度大小,进而间接地控制DDS输出幅度。

AD9834的DAC的基准电流是芯片内部基准电压V_{REF}和外部电阻R_{SET}的函数,该电阻一般从DAC FSADJUST引脚接地,基准电流等于V_{REF}/R_{SET},其中V_{REF}是AD9834内的基准电压,典型值为1.20V。R_{SET}电阻的典型值为6.8kΩ。DAC的满量程电流是基准电流的倍数,例如AD9834的满量程电流为:

I_{FULLSCALE} = 18 * (V_{REF} / R_{SET})如果FSADJUST连接到一个可变电压V_{DAC},则满量程电流为:

I_{FULLSCALE} = 18 * (V_{REF} - V_{DAC}) / R_{SET}改变V_{DAC}即可改变满量程电流,从而改变DDS器件的电压输出。

本设计使用STM32L431RCT6微控制器内自带的12位电压型DAC作为AD9834的满量程输出控制DAC,由于该DAC自带的缓冲输出运算放大器并不支持轨到轨输出,所以在微控制器中配置禁用内部缓冲放大器,采用外部运算放大器OPA211作为DAC输出缓冲。控制电路示意如图3.3所示。

图3.3-电流型DAC输出满量程控制

3.4.2-DDS输出驱动器设计

由于DDS输出端的电流和电压顺从范围有限,因而需要一个缓冲器向低通滤波器提供较高的电流驱动能力。另外,缓冲器提供了DDS芯片与滤波器之间的隔离,并将DDS的输出阻抗转换成驱动后级滤波器所需的特定阻抗值。

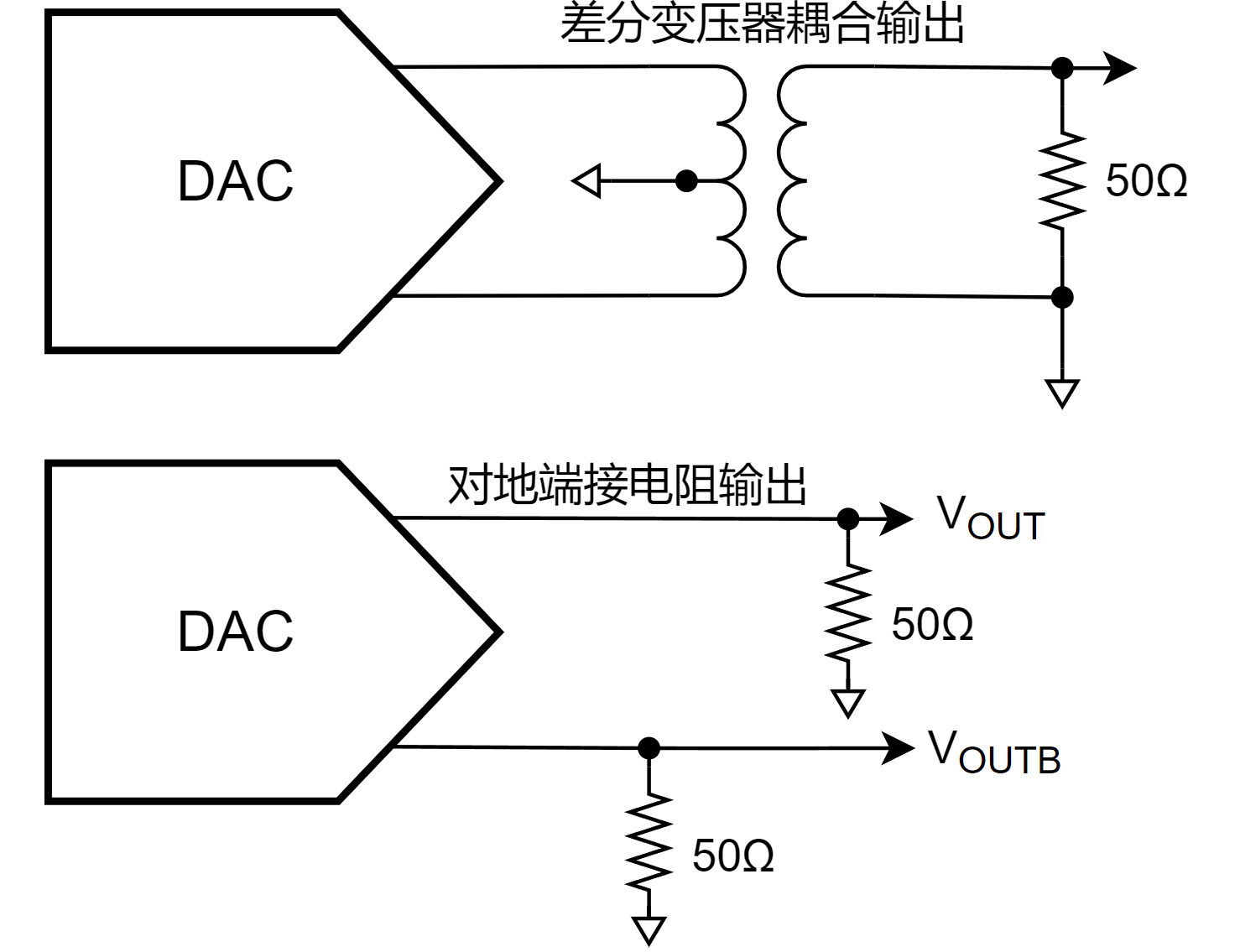

在DDS应用中一般避免使用电压输出型DAC,电压输出型DAC内部的欧姆热损耗导致其不适用于高速输出的DDS应用场景。电流型DAC在高数据速率时一般有更好的表现,AD9834的DAC就是电流输出型,其满量程电流通过FSADJUST引脚外接电阻设定。AD9834的DAC实际上由2个互补输出组成,可以用一个中心抽头接地的射频变压器将DAC的互补输出转换为单端输出;如果在2个输出端分别对地端接一个电阻,可得到2路互补输出;但前者要远远好于后者,因为使用中心抽头的RF变压器得到的输出幅度是后者的2倍,而且具有更短的电流路径。同样的,使用变压器可以有效提升系统的共模抑制比。如果DAC的2个输出中包含一些共模成分,比如时钟馈通、电源纹波成分或其他的杂散信号,那么使用RF变压器耦合时这些共模成分不能通过变压器传输到输出端,从而提升信号质量。两种输出方式如图3.4所示。

图3.4-使用差分变压器输出

然而,射频变压器并不总是最佳选择。本系统所工作的频率范围是DC-10MHz内,射频变压器在低频工作区的非线性很可能限制系统的低频性能。除此之外,还可以将运算放大器配置成差分转单端模式,或者直接使用高速差分运算放大器。本研究选用Analog Devices生产的AD8130高速差分接收器作为AD9834的DAC互补输出转换至单端输出的驱动器。AD8130是一款低成本,270MHz带宽差分接收器放大器,其在DC-25MHz内增益平坦度小于0.1dB,同时具有低噪声与低失真特性。使用AD8130差分接收器设计差分转单端转换电路无需昂贵的精密匹配电阻,并且能够使用更少的元器件来实现更高精度的输出(相较于普通运算放大器)。AD8130同时具有极高的交流共模抑制比(在10MHz时为70dB)。高共模抑制比可以让AD8130隔绝不同地平面(数模混合系统中的模拟地与数字地)上的交流噪声,同时抑制DDS芯片输出成分中的共模成分。

3.4.3-DDS输出滤波器设计

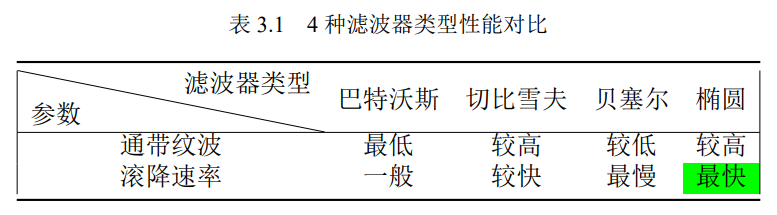

由于DDS是采样输出系统,其输出信号中将含有镜像频率与时钟馈通成分,同时还有DAC器件和差分接收器产生的非线性失真(2次与3次谐波)成分。抗镜像低通滤波器,即重构滤波器必须对这些高频成分进行衰减处理。有四类基本滤波器可以用作重构滤波器:

巴特沃斯滤波器具有最平坦的通带区间,过渡带下降速率一般,但是设计方便;切比雪夫滤波器具有较为陡峭的过渡带,但是在通带内它的增益曲线有隆起部分,Q值越大起伏越严重;贝塞尔滤波器的过渡带滚降最为缓慢,但是它具有最大的线性相移区间,可以有效减少复合波形的相位失真;椭圆滤波器又称考尔滤波器,它相比前3种滤波器在阶数相同的条件下具有最快的通带-阻带滚降速率,但缺点是它在通带和阻带内都有纹波。作为重构滤波器,我们希望用尽可能少的阶数达到期望的滤波性能,所以选择椭圆滤波器作为AD9834输出滤波器。

椭圆滤波器是一种具有零点的滤波器,它实现的滤波器具有如下特点:

- 具有最窄的过渡带,与砖墙式滤波器的响应最为近似;

- 通带与阻带内增益均有起伏;

- 偶数阶滤波器的阻带增益很小但不会随频率增大而趋于0,奇数阶滤波器的阻带会随着频率增加以一阶衰减模式趋于0。因此多数情况下椭圆滤波器都以奇数阶形式设计。

奇数阶椭圆滤波器的通用频域表达式为:

A(\jmath \omega) = { {\prod_{i=1}^n (1+(\jmath {\omega \over \omega_{si}})^2 )} \over {(1+\jmath {\omega \over \omega_{00}}) \prod_{i=1}^n(1+{1\over Q_i}\jmath{\omega \over \omega_{0i}} + {\jmath {\omega \over \omega_{0i}}})^2 } }其中,\omega_{00}是一阶低通的特征角频率(也是其截止角频率)。确定n后,即可实现2n+1阶椭圆滤波器。椭圆滤波器有如下关键参数:

\theta角,定义为:

\theta = \sin ^{-1} {1 \over \omega_s}仅当\omega_s = 1时,\theta = 90°,此时增益具有极强的陡峭下降,但阻带增益会很大。而当\theta接近0°时,也就是\omega_s特别大时,增益下降会极为缓慢,但阻带增益会有极大的衰减。

- 反射系数

\rho与通带纹波R_{dB}

反射系数\rho直接反映了通带内纹波的大小,反射系数越大,纹波越大:

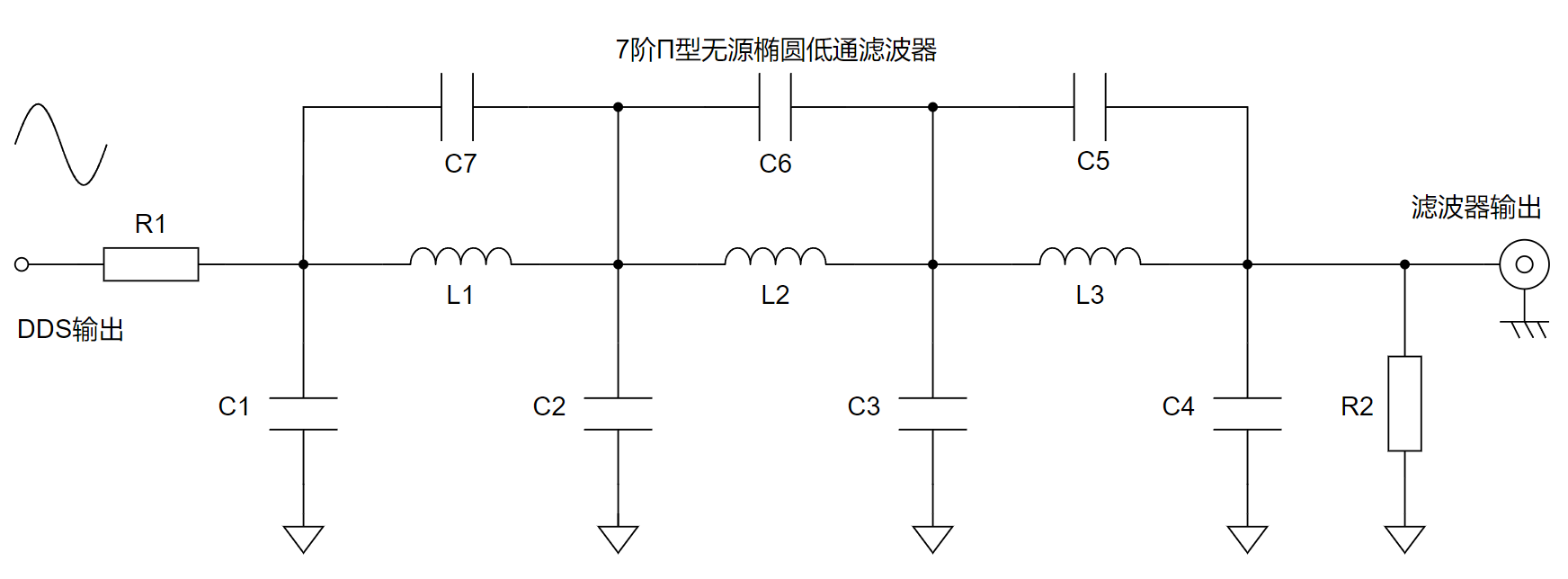

R_{dB} = -10\log_{10} (1-\rho^2)在高频段(>10MHz),想要实现有源滤波器是较为困难的,因为运算放大器的带宽已经无法满足有源滤波器的需求,这时一般采用无源电感和电容实现无源椭圆滤波器。无源椭圆滤波器的结构种类很少,只有"T型单元"和"Π型单元"组成两大类。T型单元中,电感多电容少,Π型单元中电容多电感少,图3.5所示是一个7阶无源椭圆低通滤波器。

图3.5-7阶无源椭圆低通滤波器

通过查找椭圆滤波器设计系数表可以计算出一组合适的滤波器参数如下:

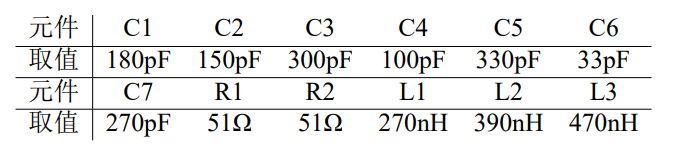

3.4.4-椭圆滤波器仿真

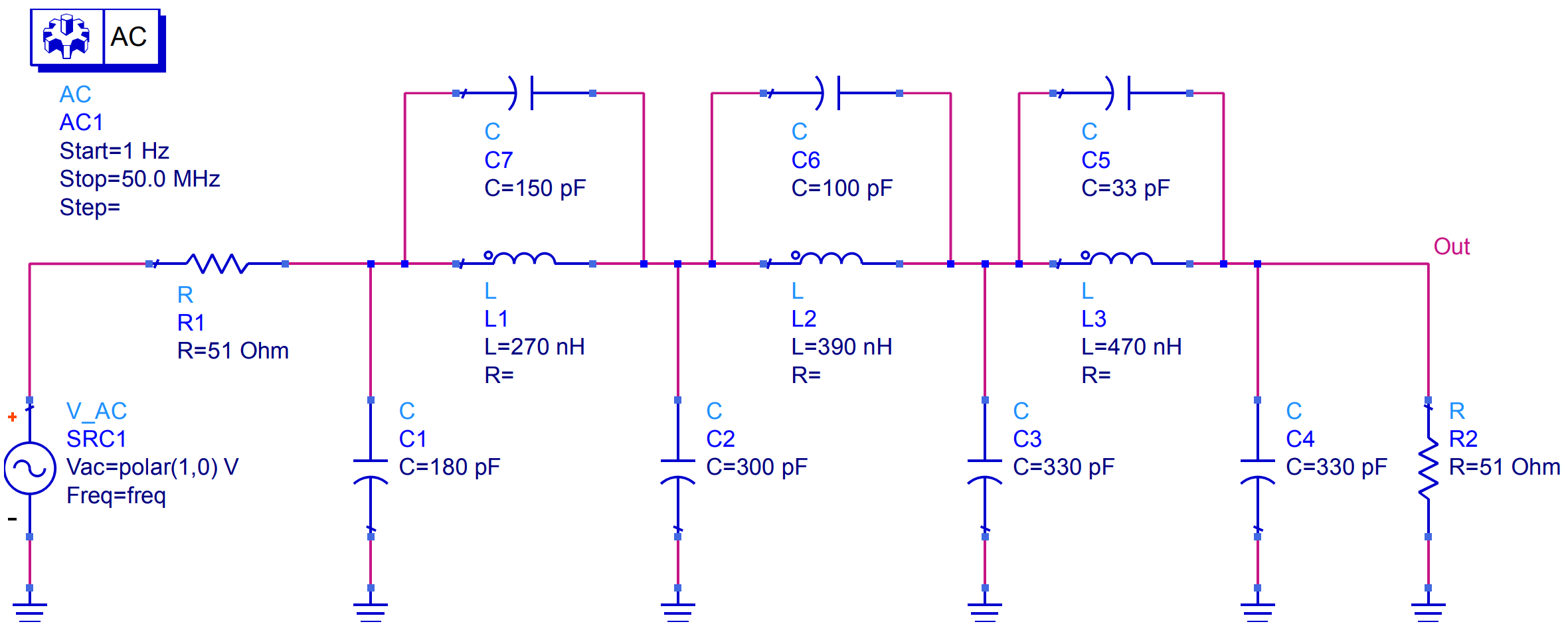

在是德科技公司的产品Advanced Design System中对设计的上述椭圆低通滤波器仿真,图3.6为仿真电路图及参数设置,全部采用理想元器件模型。图 3.7为仿真出的该滤波器的幅频特性曲线,可以看出其截止频率(-3dB频率)约为19MHz左右,满足设计需求。

图3.6-7阶无源椭圆低通滤波器仿真电路图

图3.7-幅频特性曲线图

搭建好电路,设置交流激励源作交流参数扫描,起始频率为1Hz,终止频率为50MHz,足够覆盖DDS芯片正常工作的频率范围。在此频率段内作线性扫描仿真,每隔10kHz设置一个测试点,扫描得到的结果如图3.7所示。所得到的幅频特性曲线图显示,该椭圆低通滤波器在通带内稍有起伏,起伏幅度约在1dB范围,通带增益约为-6.5dB(中位值),截止频率约为19MHz,在20MHz时的增益约为-20dB,在24MHz时的增益就已经达到了-70dB,具有很快的滚降速率,符合设计要求。

在KiCad中绘制原理图,其中完整的DDS输出驱动级和低通滤波器电路如图3.8所示。

图3.8-DDS输出级

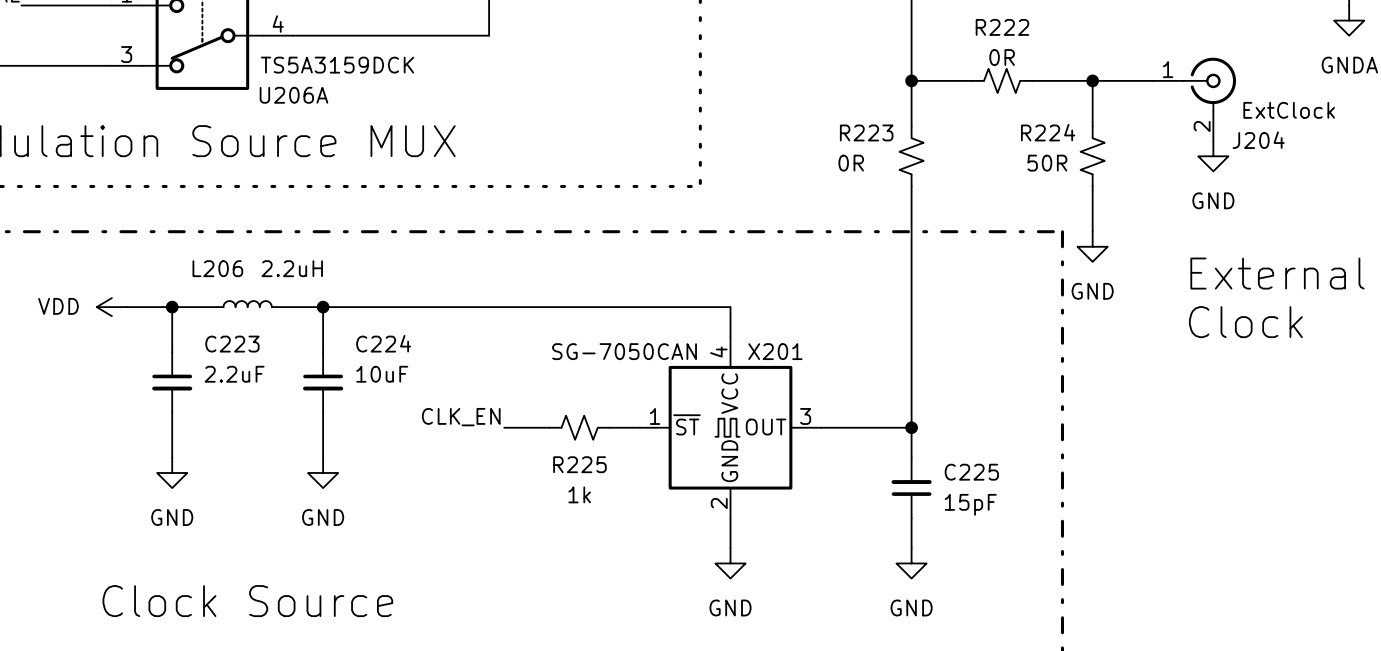

3.4.5-时钟与电源电路设计

整个系统中有2个相互独立的时钟系统,分别是微控制器的工作时钟与DDS芯片的主时钟。微控制器对时钟要求不高,所以STM32L431的工作时钟选用其内部的RC振荡器产生的频率为16MHz的HSI时钟作为时钟源,经由其内部的锁相环(PLL)倍频器倍频分频到80MHz后作为内核主时钟及各个外设和总线时钟。

DDS芯片对时钟要求较高,因为DDS芯片的工作时钟质量直接影响了DDS输出信号质量;考虑到AD9834器件本身的残留相位噪声限制,也不必使用极高精度的温度补偿晶振。选用一75MHz、总频差±20ppm的有源晶体振荡器作为DDS的工作时钟源。为其设计Π型CLC滤波器以退耦并防止其在电源轨上产生高频串扰,耦合到电路板上的其他电路上。同时设计一外部时钟接口,便于测试并验证不同质量的时钟信号对输出信号质量的影响。电路图如图3.9所示。

图3.9-DDS时钟源

整个系统的电源分为模拟部分与数字部分2个部分。系统使用+5V单电源供电,可选用XH2.54接口或USB-C接口接入电源。其中,数字部分主要负载有微控制器、有源晶振、LCD显示器以及AD9834的数字IO,负载电流在100mA以下,这些负载都能工作在3.3V电压下,所以选用一个3.3V的正压低压差线性稳压器——TLV70233,在100mA负载下,TLV70233输入输出压降最小为75mV,同时具有较高的电源抑制比(68dB@1kHz),该芯片提供SOT23-5PIN封装,适合需要紧凑的电路板空间的应用场景使用。

模拟部分对电源的要求更高,应尽量选用低噪声、高电源抑制比、负载调整率指标优秀的线性稳压器。最终选用德州仪器公司生产的LP5907低噪声低压差线性稳压器作为模拟电源的正电源稳压器。LP5907具有10uVrms以下的宽带输出噪声与极高的电源抑制比(60dB@100kHz,I_{out} = 20mA),同时提供SOT23-5PIN封装,十分适合本应用场景。

由于在模拟信号链中,AD8130需要处理双极性信号,所以还需要与模拟正电源等幅的负电源。MAX889是一款高频、稳压型、最大200mA输出的反相电荷泵,可以将LP5907输出的3.3V电源转为等幅的-3.3V电源。不过需要注意的是,MAX889的开关频率为2MHz,负电源轨上将带有2MHz的开关纹波。电源抑制比(PSRR)指某一设备对电源噪声的抑制能力。其定义是电源电压变化导致设备输出电压相应变化的比例,一般用分贝(dB)作为单位表示,其定义如下式所示:

PSRR(dB) = 20\log_{10}({\Delta V_{supply} \over \Delta V_{out}}) dB如果在放大器电路中,由于整个电路有闭环增益A_v,电源噪声将被放大,从而可以得出放大器电路的PSRR为:

PSRR(dB) = 20\log_{10}({\Delta V_{supply} \over \Delta V_{out}} * A_v) dB上式说明如果不谨慎处理开关电源带来的纹波,那么该纹波会被放大,从而导致精密信号链路中的信号质量恶化。多数运算放大器的PSRR性能在MHz频段表现不佳,所以需要使用后级滤波器对高频纹波成分加以充分衰减。

完整的电源拓扑结构如图3.10所示。完整的系统电路图详见附件。

图3.10-系统电源拓扑结构

第四章:软件设计与系统测试

论文前部分讲述了DDS芯片的原理与特性,以及本研究的硬件设计方案,本章将介绍基于DDS芯片的信号发生器的软件设计与系统调试、参数测试部分。本研究采用C语言为ARM内核微控制器进行编程从而实现设计要求的功能,同时结合有限状态机的编程思想设计多级菜单界面,方便通过旋转编码器和按键调节系统各项参数。STM32微控制器的硬件底层驱动库调用意法半导体官方推出的 STM32 HAL 库完成,同时自行编写了AD9834及液晶屏控制器ST7789的驱动程序。最后经过软硬件联合调试,在示波器和频谱仪上观测了本研究所设计的信号发生器的输出信号及其杂散指标。

4.1-AD9834驱动程序设计

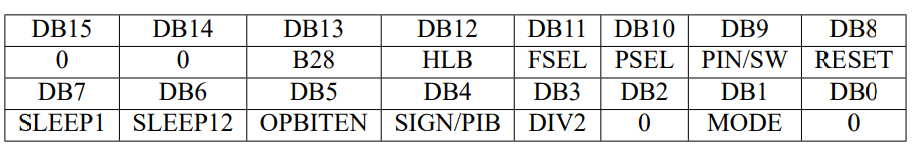

AD9834内包含一个16-bit的控制寄存器,可以使用该寄存器来配置AD9834的所有工作模式,该控制寄存器各位如下表所示。

AD9834有2个28位的频率调谐字寄存器和2个12位的相位调谐字寄存器。如果要对频率寄存器进行写入操作,首先需要设置控制寄存器的DB15和DB14位以分别对应频率寄存器的高14位、低14位地址。如果需要改变频率寄存器中的全部内容,则需要将控制寄存器的DB13位置1,同时对同一地址执行两次连续写入,第一次写入包括14位LSB,第二次包括14位MSB。一个完整的频率寄存器写入操作如下表所示。

相似的,写入相位寄存器时,DB15和DB14位应置11,DB13位确定将写入的寄存器序号。AD9834的初始化过程和工作流程图如图4.1所示。

图4.1-AD9834初始化和工作流程图

4.2-基于状态机的软件框架设计

通常为微控制器编程可选择裸机编程,或使用诸如FreeRTOS、RT-Thread等嵌入式实时操作系统。本研究的目的是设计能够产生多种数字调制信号的信号发生器,需要该系统在工作时能够快速切换不同的工作模式,同时能够灵活地调节参数。要完成该软件逻辑编写,既可以使用嵌入式操作系统,也可基于裸机自行编写有限状态机的软件控制逻辑。因为信号发生器仅涉及简单的输入-输出操作,可将其简单抽象成有限状态机模型来完成软件开发工作。

有限状态机(Finite-State-Machine, FSM)又称有限状态自动机,简称为状态机,是表示有限个状态以及在这些状态之间的动作和转移等行为的数学计算模型。状态机存储了从系统运行开始时到现在时的变化,并且根据当前的系统输入来决定下一个工作状态。状态机的动作是在给定的时刻要进行的操作或活动的描述,状态机有多种类型的动作:

- 进入动作(entry action),在进入某状态时执行

- 退出动作(exit action),在退出状态时执行

- 输入动作(input action),依赖于当前状态和输入条件执行

- 转移动作(transfer action),在进行特定转移时执行

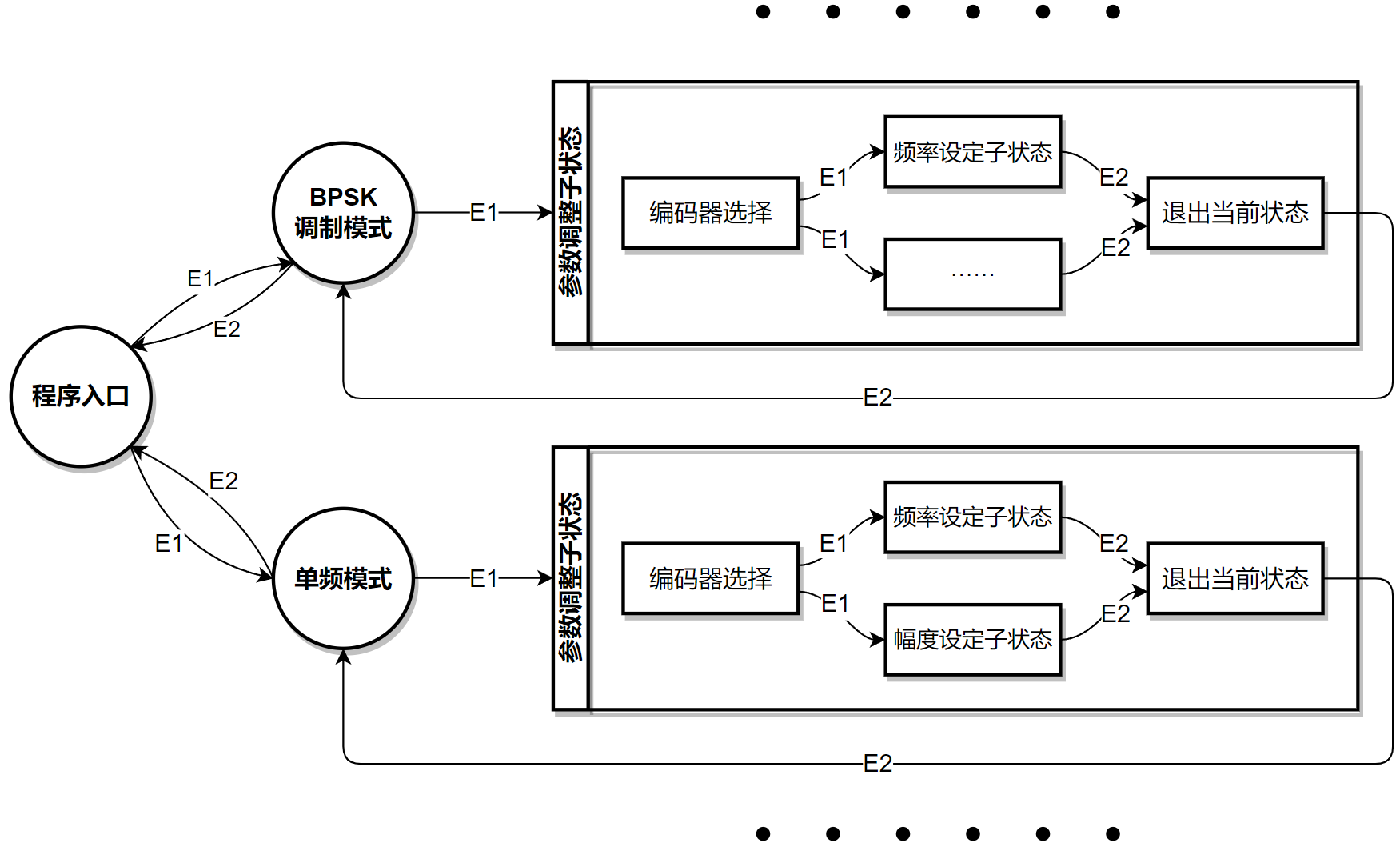

信号发生器的简化状态转移图如图4.2所示,系统启动后在程序入口处选择要进入的工作模式,每个工作模式内又包含2层子状态机,方便进行参数调节与工作参数切换。而每个模式的运行逻辑是十分简明清晰的,图中仅画出了BPSK调制模式和单频模式,其他模式可仿照该框架进行并行排列,从而使该系统的软件开发变得高度灵活,可扩展性大大加强。

图4.2-信号发生器的简化状态转移图

4.3-系统测试

在完成了信号发生器的硬件和软件设计之后,采购元器件并打样PCB板,焊接PCB完成后即可进行整体系统的软硬联合调试工作。结合设计要求并依据DDS芯片工作原理,编程控制DDS芯片产生单频正弦波、单频三角波、BPSK、BFSK、ASK、Chirp信号等其他复杂数字调制信号,以此来测试信号发生器的电气性能。

4.3.1-单频正弦波

理想正弦信号是频率成分最为单一的一种电信号,也是电子系统与通信系统中最常见的信号之一,通常单频正弦信号被用作载波,结合调制器实现对基带信号的调制。DDS器件最常规的用途就是产生单频正弦信号,AD9834内的SIN ROM将来自频率和相位寄存器的数字相位信息转换为数字幅值信息,并利用DAC器件将数字信号转换成模拟信号,从而在输出端产生正弦信号。输出信号的频率由式(4-1)决定,其中 FTW 代表频率调谐字, f_{REFCLK} 代表DDS主时钟。

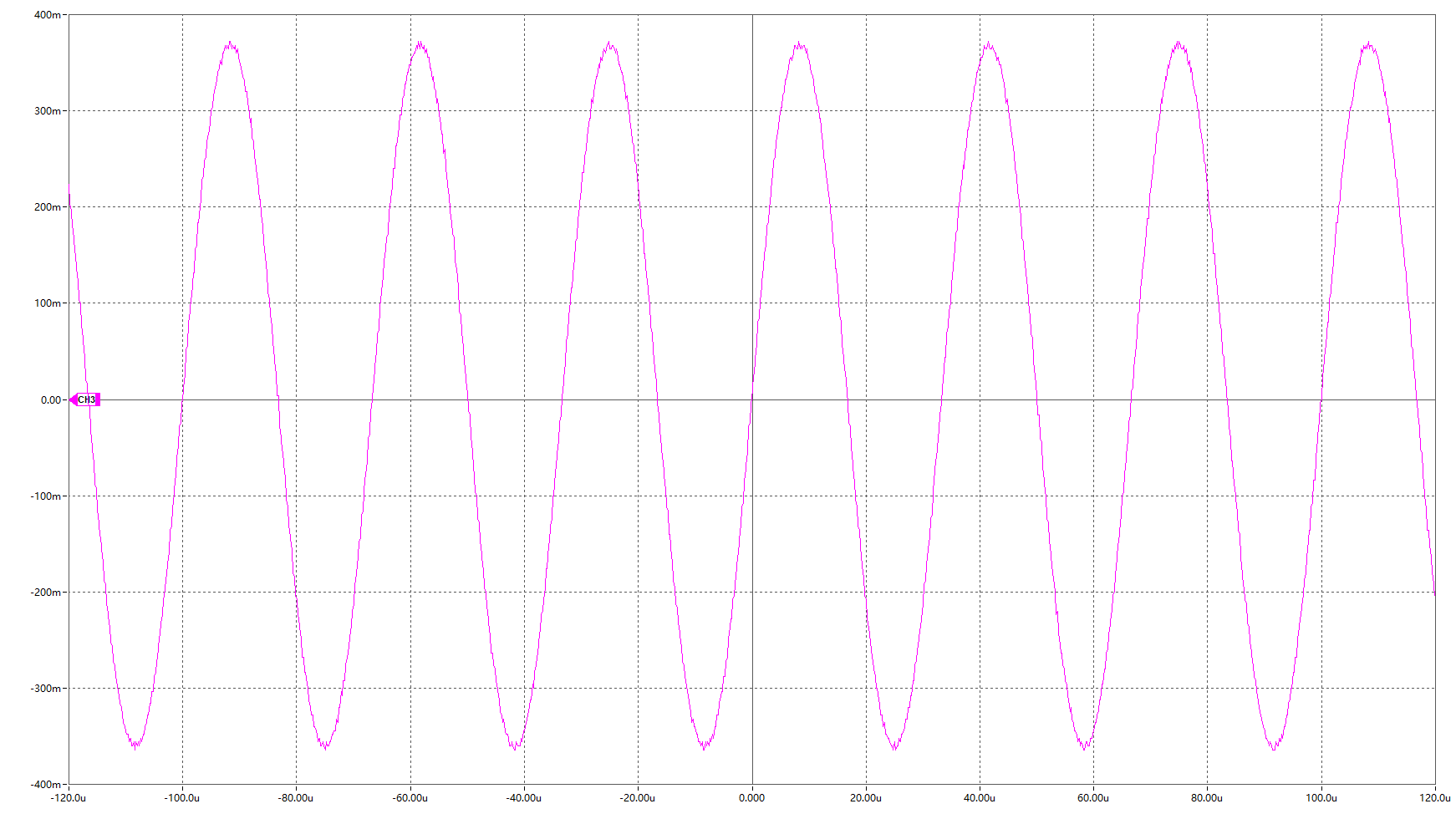

f_{out} = {FTW \over 2^{28}} * f_{REFCLK} \cdots (4-1)其中,根据硬件设计,AD9834的主时钟即 f_{REFCLK} 为75MHz,配置 FTW = {{2^{28}*10^4} \over {75*10^6}} = 35791,即可得到10kHz的正弦波输出。通过微控制器对AD9834写入该频率调谐字,并开启正弦输出模式,得到的输出波形在示波器上显示如图4.3所示。

图4.3-AD9834产生10kHz正弦信号

4.3.2-单频正弦信号质量分析

理想的单频正弦信号的频谱只含有单一频率成分,然而真实世界中没有理想信号,任何正弦信号都或多或少地含有谐波、杂散成分与噪声。从第二章可知DDS输出的信号中含有由采样系统固有特性而附带的多种镜像频率、由数字到模拟转换过程中产生的量化误差、来自采样时钟的馈通信号与电源器件上的噪声等等。精确地测量信号发生器的输出信号质量是至关重要的。信号发生器的输出级接有一椭圆低通滤波器,但是其截止频率为10MHz数量级,在DDS输出低频信号时,可能无法滤除二次及三次谐波。然而在输出低频信号时,依靠过采样可以大幅降低量化误差,提升信噪比。在输出高频信号时,多数镜像频率成分及谐波失真都可以通过重建滤波器滤除。

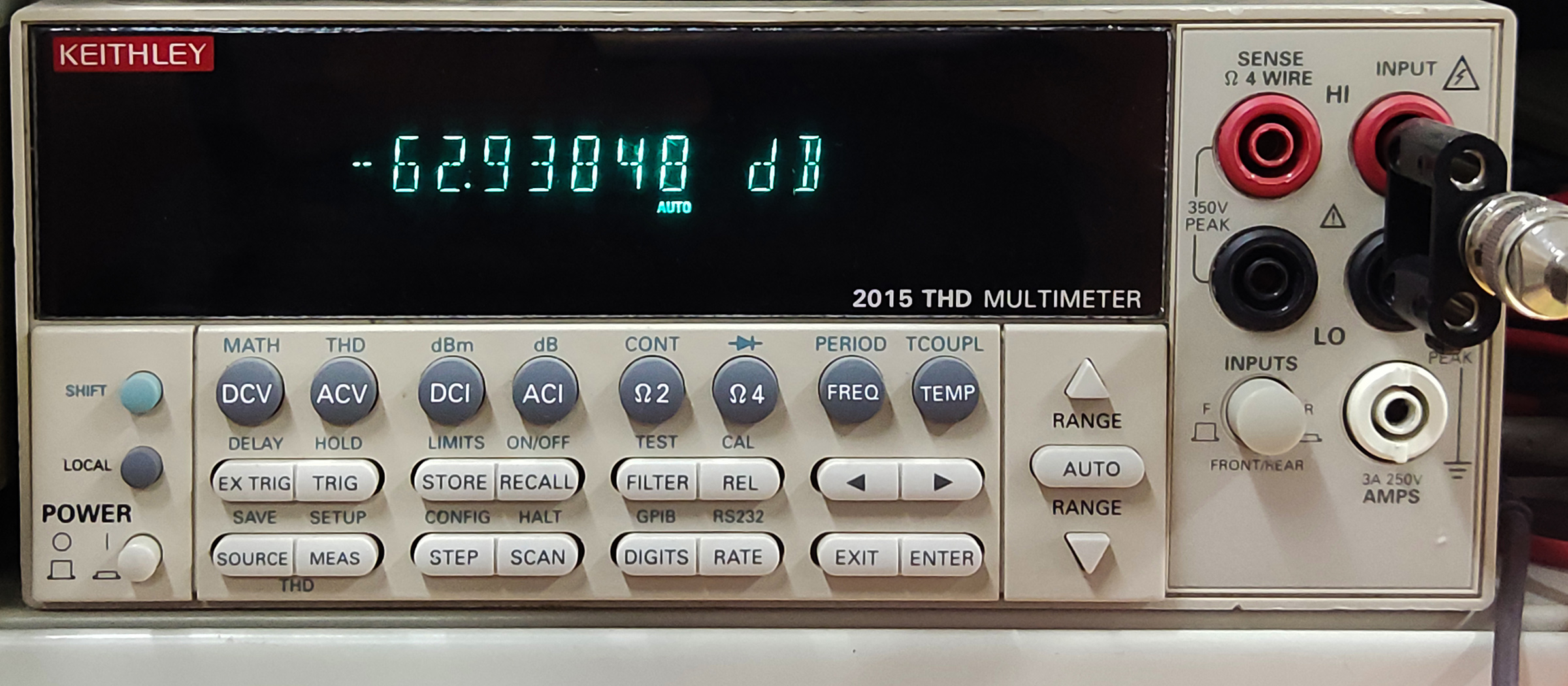

首先令信号发生器产生1kHz的正弦信号,然后将信号发生器的输出连接到Keithley 2015数字万用表上,测量其总谐波失真度(Total Harmonic Distortion, THD)。总谐波失真度是衡量信号谐波失真的一项重要指标,一般THD定义为谐波频率的振幅平方和的均方根值与基波频率的振幅的比例,如式(4-2)所示。

THD_F = { {\sqrt{V_2^2 + V_3^2 + V_4^2 + \cdots + V_n^2}} \over V_1} \cdots (4-2)设置失真度分析功能测量最高到10次谐波,并采用对数表示测量结果,测得1kHz正弦信号的THD值约为-62.94dBc(图4.4(a))。AD9834手册中标注的THD典型值为-66dBc,最大为-56dBc(f_{MCLK}=75MHz,f_{out}=f_{MCLK}/4096=18.3kHz),与实际测试结果十分接近。

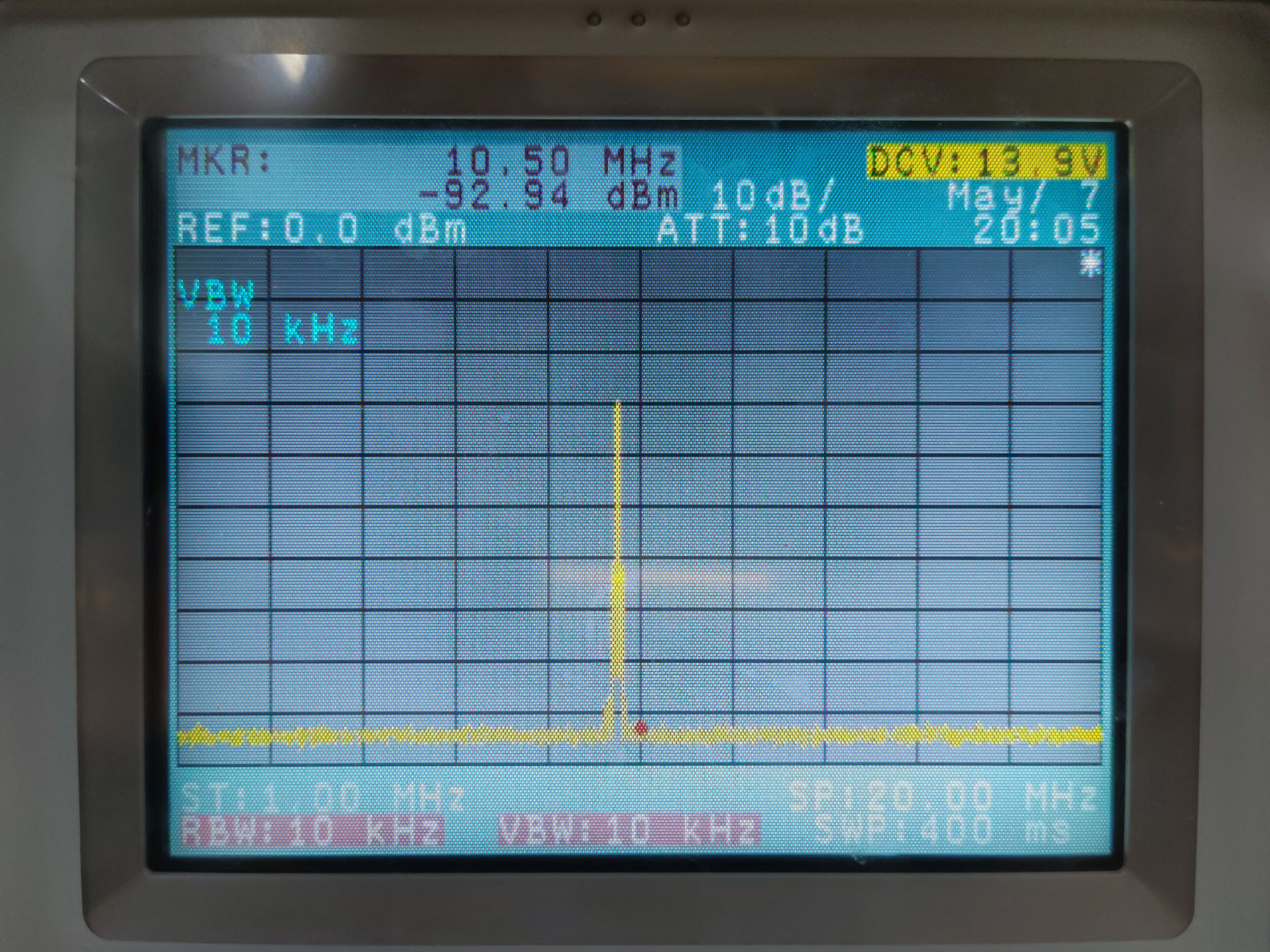

接着,令信号发生器产生10MHz的正弦信号,将信号发生器的输出连接到频谱分析仪上,测量其高频输出时的无杂散动态范围(Spurious-Free Dynamic Range, SFDR),设置频谱仪扫频起始频率1MHz,终止频率20MHz,VBW、RBW均为10kHz,输入衰减10dB,垂直档位为10dB/div,得到测量结果如图4.4(b)所示,可以从频谱图读出,其SFDR约为65dBc。AD9834手册中标注的宽带SFDR典型值为-60dBc,最大值为-56dBc,窄带SFDR(±200kHz)典型值为-74dBc,最大值为-65dBc。实际测试的结果略次于AD9834手册中标注的指标。

图4.4(a)-1kHz单频正弦信号THD值

图4.4(b)-10MHz单频正弦信号频谱

4.3.3-幅度调制

信号发生器的输出幅度由STM32微控制器片内的12-bit DAC控制,由前式(3-2)可知,改变DAC输出电压即可控制AD9834的输出满量程电流,从而间接控制输出电压大小。从AD9834数据手册得知,AD9834内置电压基准电压值为1.2V,那么幅度控制DAC输出电压为1.2V时,信号源输出电压为0V;幅度控制DAC输出电压为0V时,信号源输出电压达到最大值。为了验证幅度控制原理的正确性,编写程序使AD9834输出一固定频率的单频正弦波,并且让幅度控制DAC执行从0V到1.2V的线性扫描,在信号源的输出端观察到电压波形如图4.5所示。该结果说明前述幅度控制方案的原理无误。同时还能看出,STM32片内DAC的线性度指标较好。

图4.5-线性幅度扫描

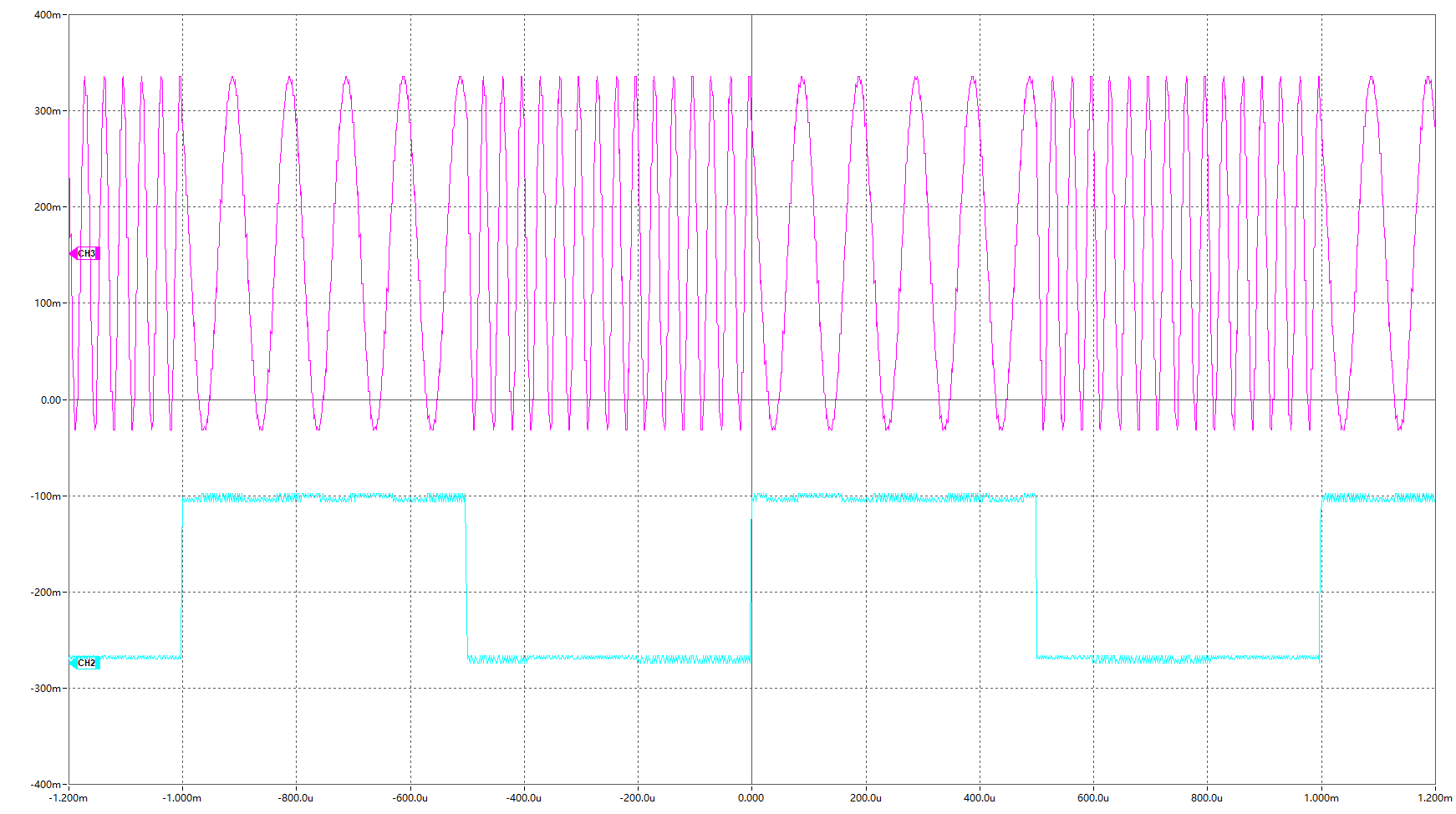

现编写程序,使AD9834执行4进制ASK调制,验证M-ASK调制的可行性。载波频率f_c=10kHz,4个符号分别对应的幅值为0.25倍、0.5倍、0.75倍、1倍满量程输出电压,调制信号每2ms更改一次符号,在信号源的输出端观察到电压波形如图4.6所示。该结果说明此信号源具有执行多符号ASK调制的能力,同时也进一步说明前述的幅度控制方案原理无误。

图4.6-4-ASK调制

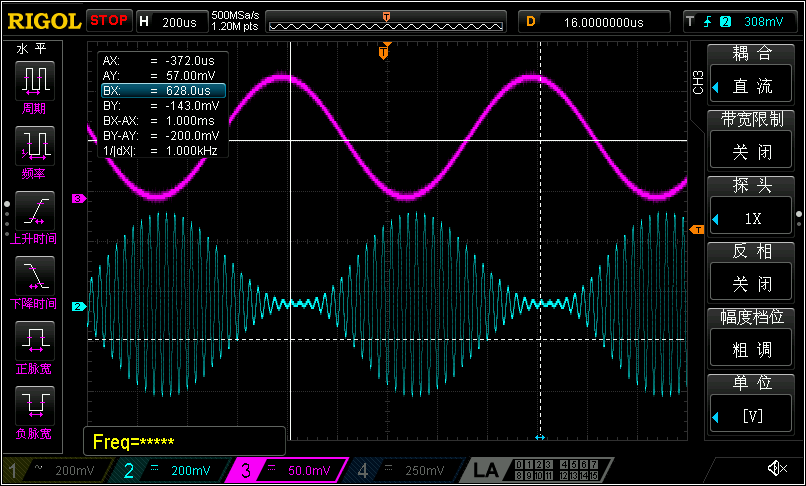

现编写程序,令AD9834的满量程输出幅度控制DAC输出一频率为1kHz的正弦波作为基带信号,同时使AD9834输出30kHz的正弦波作为载波,以此实现AM调制,电路等效于一个乘法型DAC结构。在信号源的输出端观察到电压波形如图4.7所示,蓝色波形为AM调制信号,紫色正弦波为基带信号,基带信号与调制信号的包络线存在一定相位滞后。如果改变幅度控制DAC的正弦输出幅度,就可以方便地改变调制深度。此测试结果表明前述的AM调制方案无误。

图4.7-AM调制

至此,该信号源的幅度调节能力、ASK调制能力与AM调制能力得到了验证。

4.3.4-BFSK与BPSK调制信号

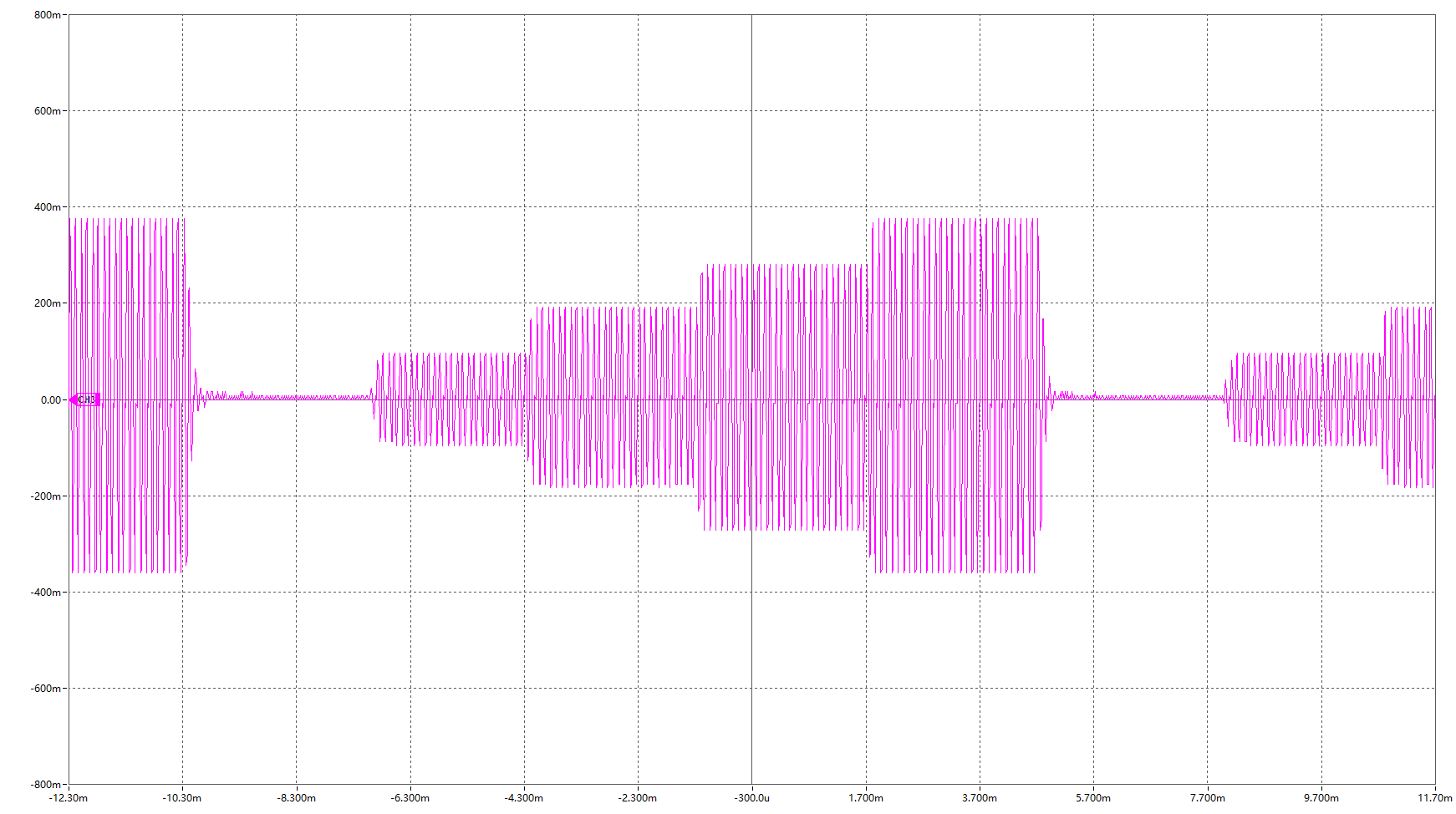

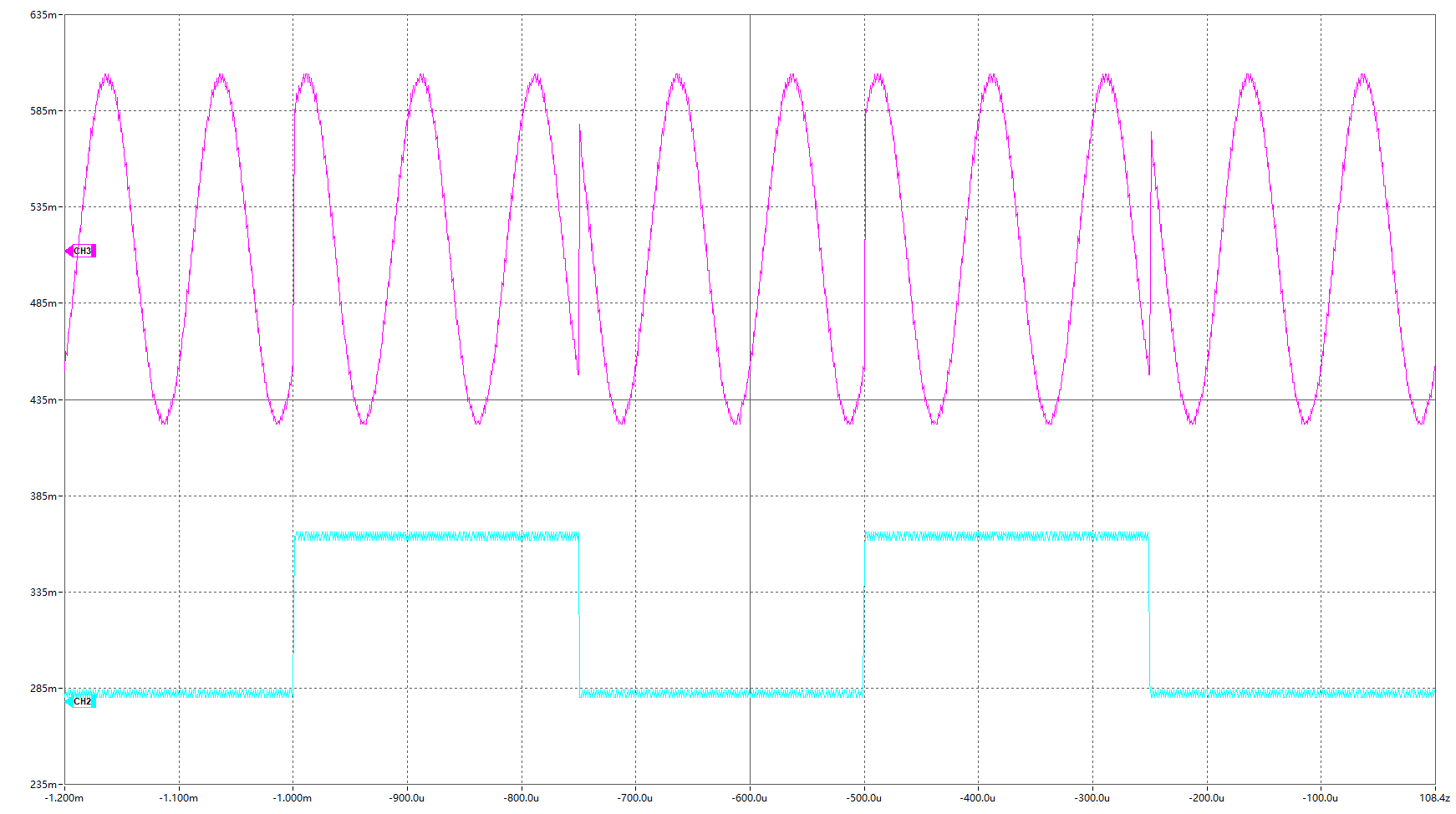

最简单的也是最常见的FSK为二进制FSK(Binary FSK,简写BFSK或2FSK)。BFSK利用2个离散的频率值分别代表不同的二进制信号(0和1),更高进制的FSK还有四进制FSK(QFSK)等。AD9834具有2个频率调谐字寄存器,所以用AD9834执行BPSK是最为简单的。若要执行更高进制的FSK调制,需要使用2个频率调谐字寄存器进行乒乓操作来不停更新频率调谐字,较为复杂;为方便测试,这里仅选用BFSK进行测试。编写程序使AD9834使用外部控制信号选择频率调谐字寄存器,然后分别向2个频率调谐字寄存器中写入2个不同的频率值(10kHz与30kHz),通过外部信号源提供基带信号用于选择频率调谐字寄存器,在信号源的输出端观察到电压波形如图4.8(a)所示。其中,紫色波形是BFSK已调信号,蓝色波形是外部基带信号的同步信号。该结果说明前述BFSK调制方案准确无误,且该方案得到的调制波形相位连续。

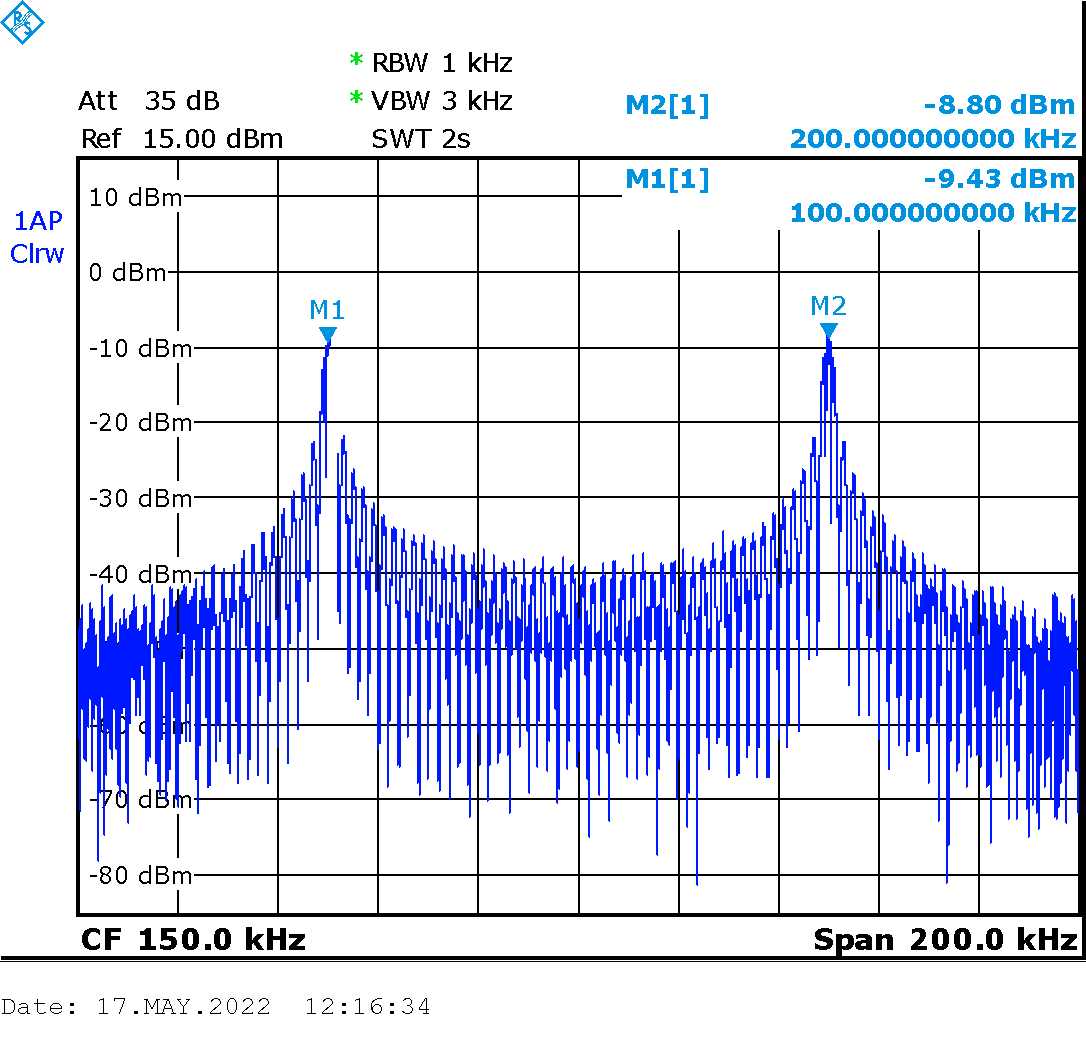

同时配置BFSK调制的频率值分别为100kHz与200kHz,调制速率1kHz,在信号源的输出端观察到信号频谱如图4.8(b)所示。

图4.8(a)-BFSK调制

图4.8(b)-BFSK调制频谱

对于PSK,同理BPSK也是最简单的调制形式,对于AD9834来说也是如此。为方便测试,这里仅选用BPSK进行测试。编写程序使AD9834使用外部控制信号选择相位调谐字寄存器,然后分别向2个相位调谐字寄存器中写入2个不同的相位值(对于BPSK为0°与180°),向一个频率调谐字寄存器中写入定值(10kHz)。通过外部信号源提供基带信号用于选择相位调谐字寄存器,在信号源的输出端观察到电压波形如图4.9所示。其中,紫色波形是BPSK已调波,蓝色波形是外部基带信号的同步信号。该结果说明前述BPSK调制方案准确无误。

图4.9-BPSK调制

至此,该信号源的BFSK与BPSK调制能力都得到了验证。

4.3.5-Chirp信号

Chirp信号是频率随时间而改变的信号,是扫频信号的一种。要使用AD9834 DDS芯片产生Chirp信号,在写入频率寄存器时需要注意连续写入带来的过渡态跳频效应——即对于正在使用的频率寄存器进行写入,会导致输出信号在写入过程中产生跳频。解决的办法是利用AD9834的2个频率寄存器进行乒乓操作,如当前使用的频率寄存器是寄存器0,那么就对寄存器1进行写入操作,写入完成后将寄存器1接入数字信号链中,接替寄存器0,然后再开始对寄存器0写入,如此循环。

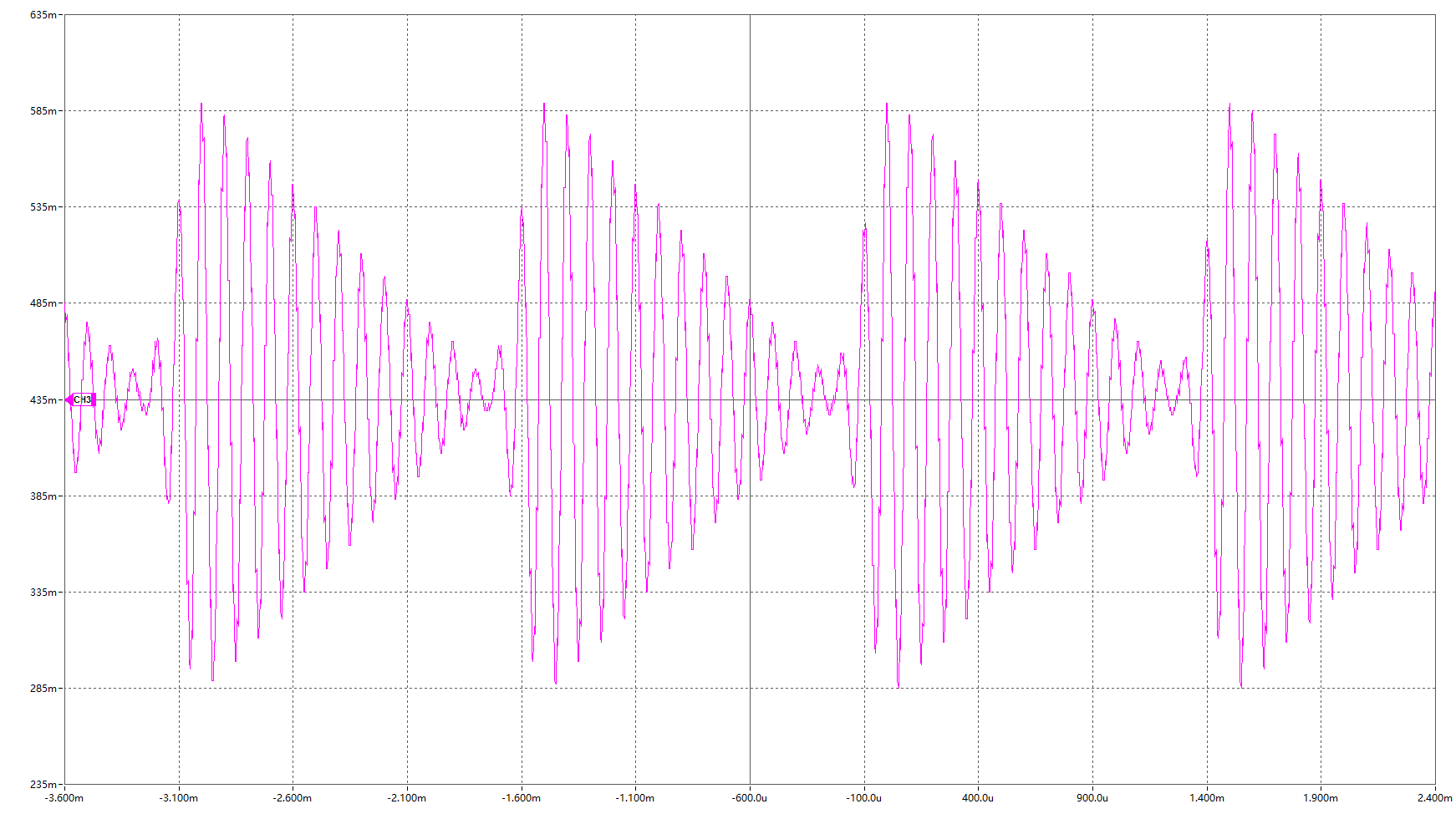

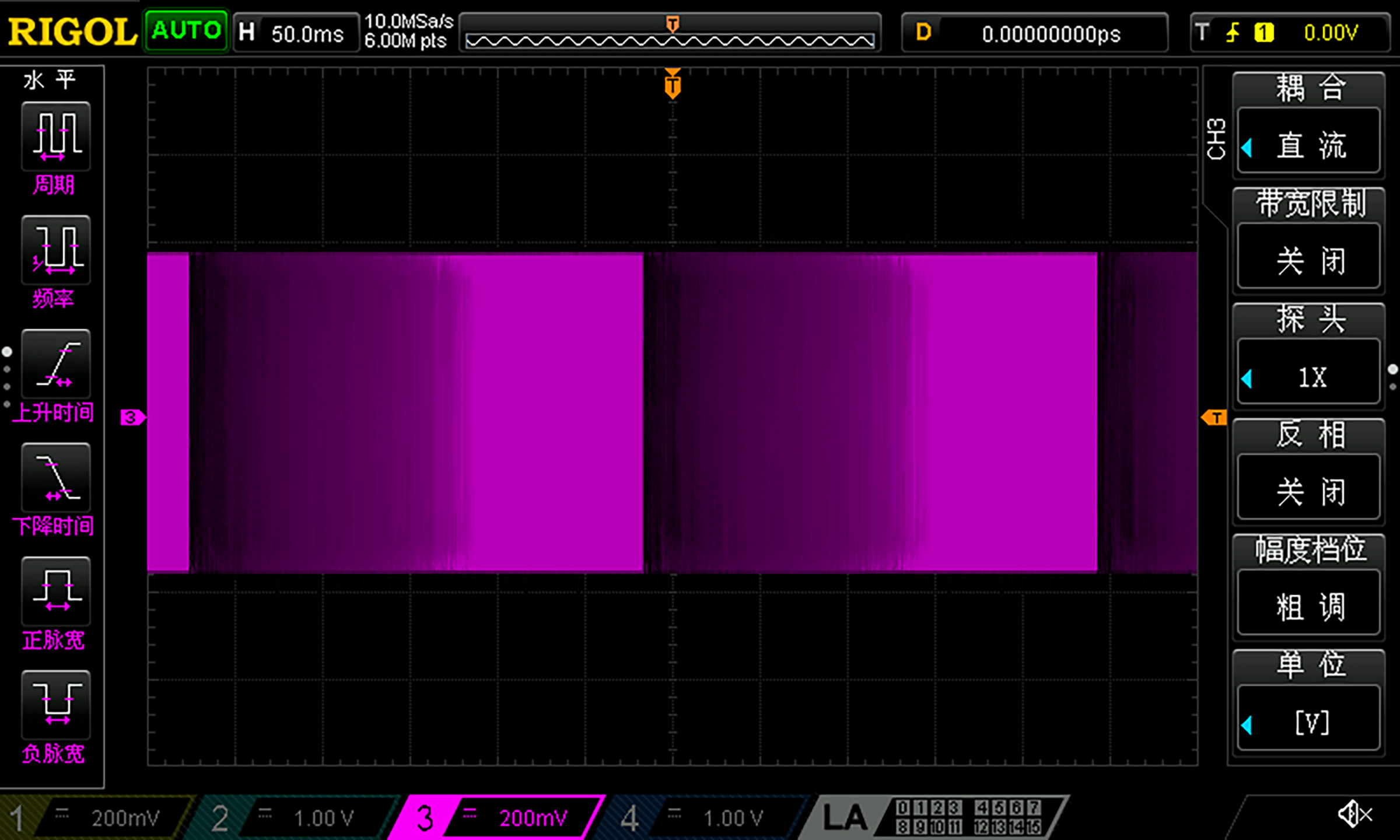

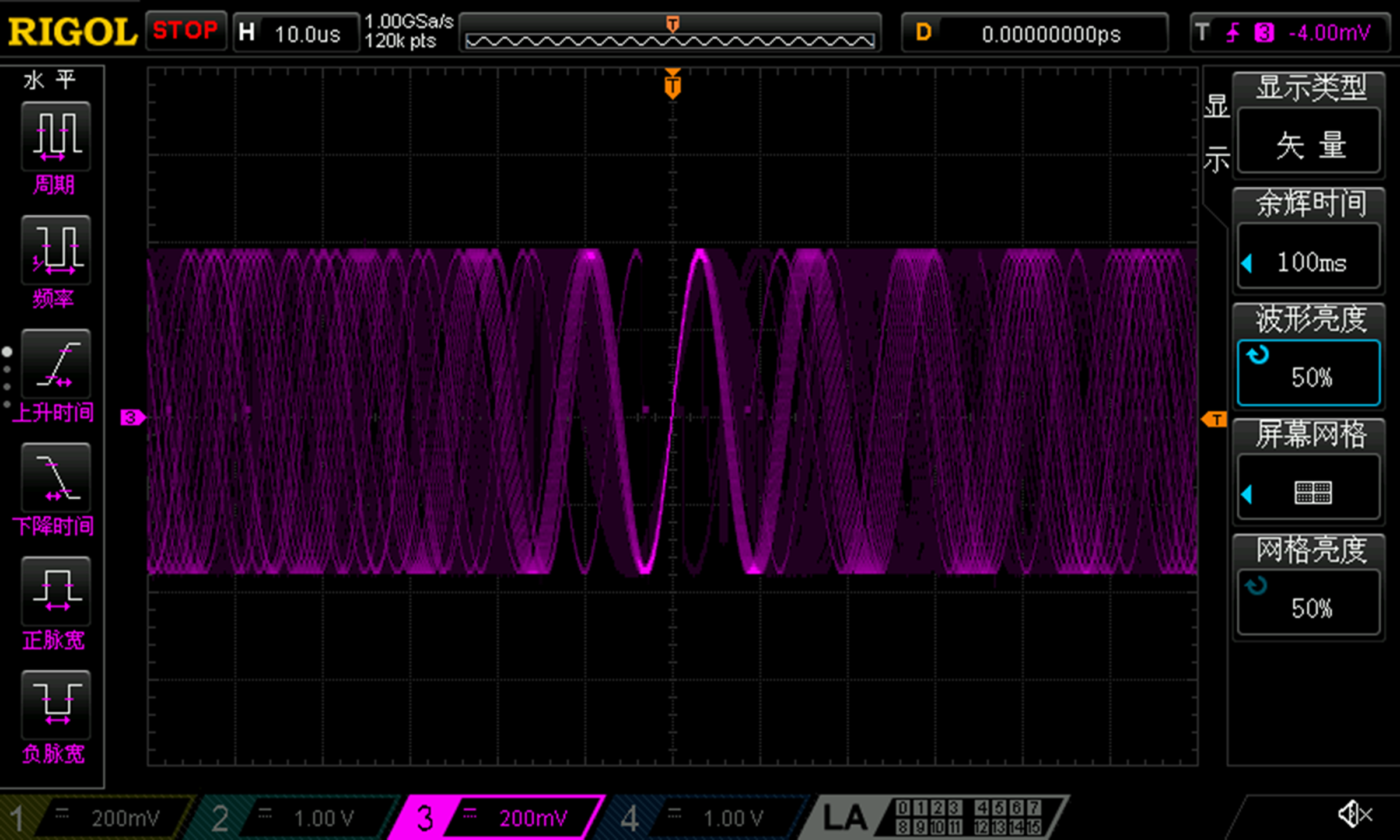

编写程序使AD9834产生10Hz到100kHz的指数增长Chirp信号,应用乒乓操作来避免过渡态的跳频效应,在信号源输出端观察到电压波形如图4.10(a)所示。由于Chirp信号的频率在不断变化,若观察其中一小段便不能知其全貌,所以更好的观测方法是观察一段时间内的波形的密度变化,可以通过示波器的灰度功能来实现:当波形稀疏时(频率低),波形较暗;当波形密集时(频率高),波形亮度较高。从测试结果可以大致看出Chirp信号的时域波形符合设计要求。该结果说明前述Chirp信号产生的原理与设计思路无误。另使AD9834产生一线性增长Chirp信号,利用示波器的数字余晖功能可看到频率变化(扫频)的过程,波形如图4.10(b)所示。

图4.10(a)-指数增长Chirp信号

图4.10(b)-线性增长Chirp信号

至此,该信号源的Chirp调制能力得到了验证。

4.3.6-功耗测试

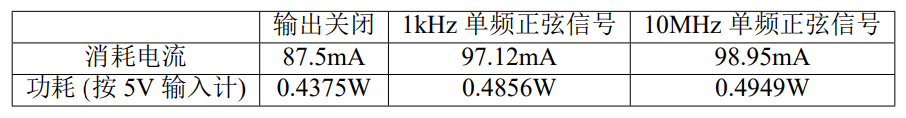

该信号发生器支持3.5V-5.5V电压宽范围供电,因为板上所有供电均由2颗LDO产生,所以系统消耗的电流是恒定的。使用外部5V电源供电,将电流表串入信号发生器的供电回路中,以测量该信号发生器的整机功耗。分别进行3个工作点的测量:关闭输出、产生1kHz低频信号、产生10MHz高频信号。总结测试结果如下表所示。从测试结果可以看出,整体系统功耗始终在0.5瓦以下。

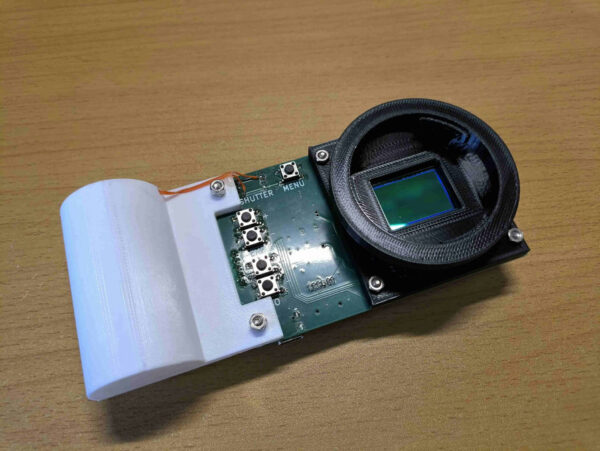

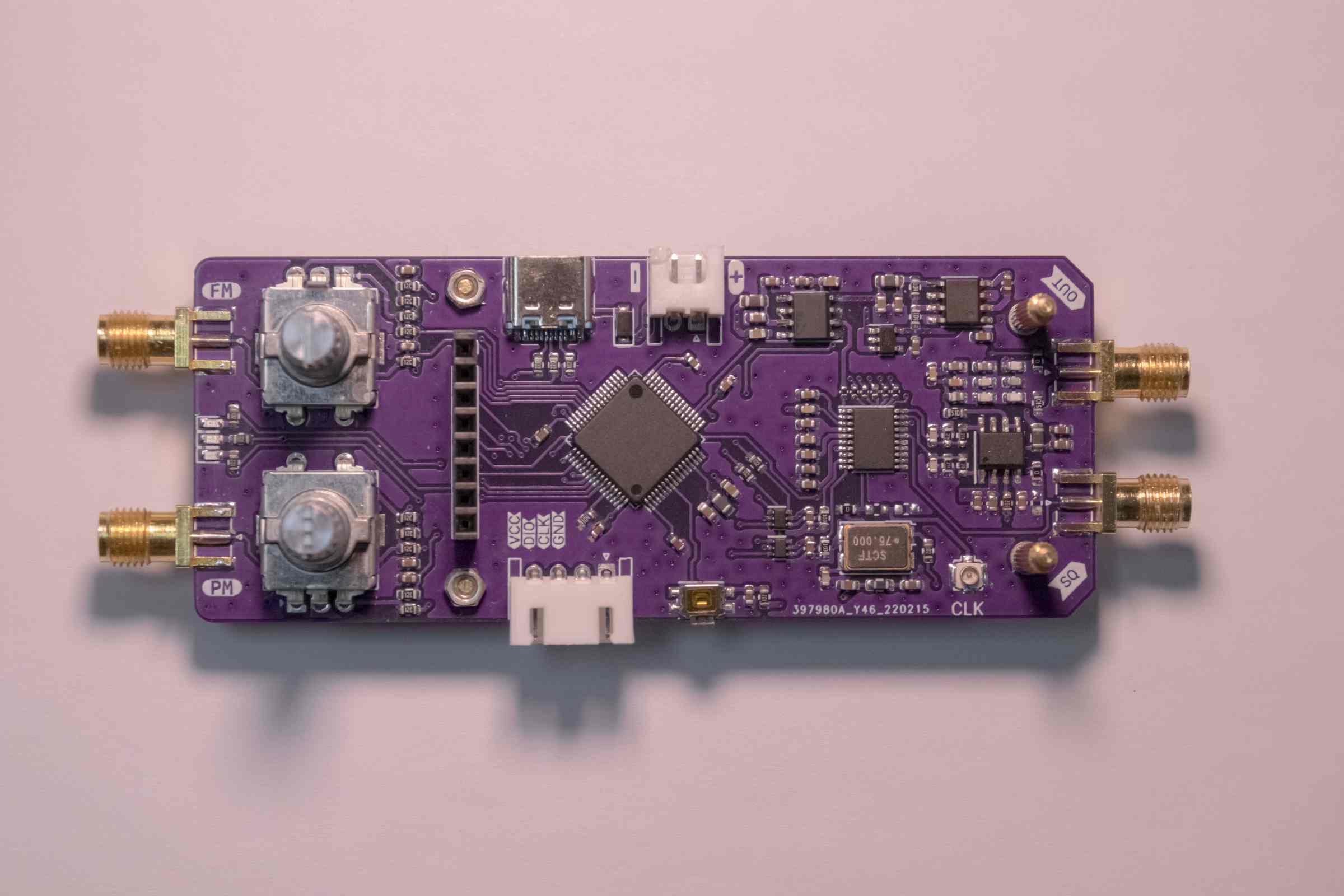

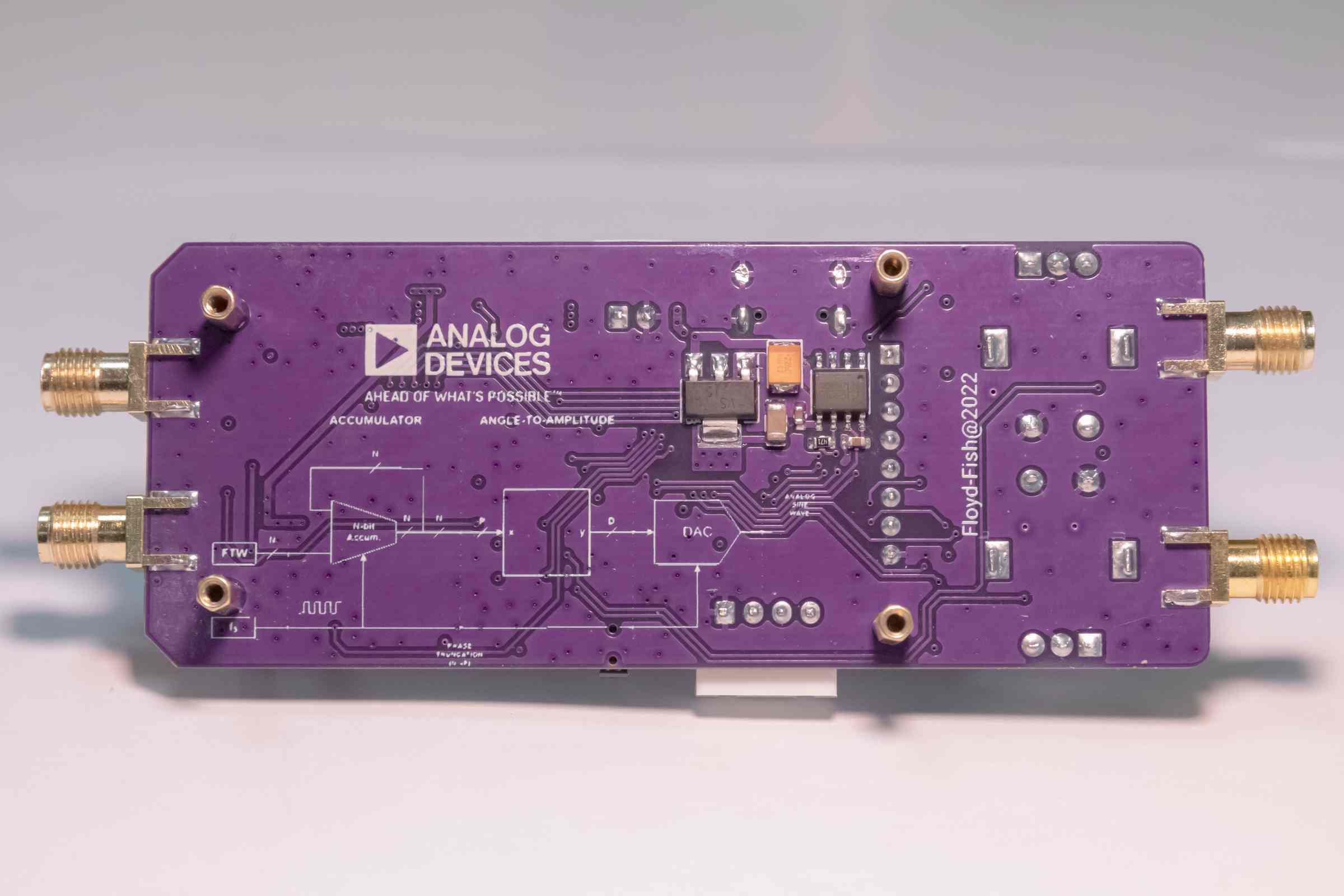

实物图

信号发生器正视图

信号发生器元器件布局

信号发生器背视图

第五章:总结与展望

5.1-研究总给

现代信号发生器对于细密步进、低相位噪声、捷变能力、高频谱纯度与低功耗等方面的性能提出了更高的要求,采用传统的信号发生器架构已经难以满足这些设计要求。随着半导体技术的不断进步,现在已经可以利用高度集成化的器件实现相较于过去传统信号发生器性能更强、功耗更低、电路尺寸更小的高速信号发生器。本文利用DDS器件与集成差分驱动器实现了较为简单的高速信号源设计。本文主要完成的工作如下:

- 介绍了DDS技术原理与特性

在第二章中,首先对DDS技术的原理与特性,对DDS的技术特点和性能指标进行了详尽的分析,包括DDS的采样输出特性、DDS的杂散性能受哪些因素影响、以及DDS技术在调制中的应用;同时说明了DDS技术为什么难以直接用于复杂模拟调制,以及相应的解决办法;

- 设计了基于DDS芯片的信号发生器的硬件方案

结合设计要求,论文第三章进行了主要芯片选型工作,然后结合实际芯片性能设计了相应的DDS外围电路与微控制器外围电路;最后对信号发生器的输出级重建滤波器(椭圆滤波器)做了详尽分析与仿真,得到了期望的结果。

- 完成了系统软件设计与测试

依据前述系统硬件方案与设计,论文第四章描述了如何利用有限状态机(FSM)思想来设计微控制器的软件框架,同时详尽分析了如何为AD9834编程。在此之后,论文对信号发生器的各项功能指标进行了测试,包括产生单频正弦波、幅度调制功能、二进制FSK与PSK调制功能、线性与对数Chirp功能,以及最后的系统功耗测试。

5.2-研究展望

现代商用任意信号发生器的架构多为FPGA+DSP结合射频DAC,前者负责读取、运算数字波表,而后者负责将信号从数字域转换到模拟域。DDS芯片使用简单、灵活性强、集成度高,并且能显著缩短产品开发周期,但相较于前者在任意波形产生方面还存在劣势。并且商用的成熟DDS器件的频率难以覆盖10GHz以上的射频频段,此频段的信号源设计目前主要还是由射频DAC主导。本文设计的基于AD9834 DDS芯片的信号发生器能够完成基础的调制功能与信号发生功能,是一个基于DDS的低频信号发生器的简易尝试。由于作者时间与精力有限,研究工作尚存在以下几点不足待以提升:

1.增加闭环幅度控制电路。本研究在设计硬件电路时并未在输出端末段设计可变增益放大器与峰值检波器电路,在低频至高频范围内,由于重建滤波器响应与DDS的sinx/x滚降响应,输出信号幅度存在一定量的起伏。增加峰值检测与可变增益放大器电路可以使信号源实时自校整输出信号幅度,使其输出的信号在工作频带内保持恒定的设定幅度。

2.使用ADC采样外部调制信号输入。本研究设计的BFSK、BPSK外部调制电路只能支持外部3.3V电平标准数字信号,如果使用ADC采样外部调制信号输入,并采用软件判定阈值的方法,可以拓展外部调制信号输入的灵活性;且本研究并未设计外部AM调制输入,如果使用ADC采样外部调制信号输入,便可将3种调制统一到一个输入端。

3.操作逻辑过于复杂。本研究设计的信号发生器在设计时为实现紧凑尺寸与小体积,所有操作由2个带按键的旋转编码器完成,在设定参数时稍显复杂。考虑后续设计可以添加数字键盘,可大大提升使用体验。

4.改善设计方案,以将输出信号频段拓展至更高。如上述对现代信号发生器的分析所述,采用FPGA+DSP结合射频DAC的任意信号发生器设计将是未来一段可预见时间内的主流方案,且这种方案所能覆盖的频段更高、任意波形发生能力也要强于DDS芯片。

由于作者在撰写论文过程中知识水平有限,文中难免有不足之处。敬请读者批评指正。

致谢

时间像一把无形的利刃,无声地切开了坚硬和柔软的一切,恒定地向前推进着,没有任何东西能够使它的行进产生丝毫颠簸,它却改变着一切。

不知不觉中,四年的大学时光即将落下帷幕。回首过去的四年,尽是对技术的无限热爱与追求,无数个在实验室度过的的日日夜夜即是最忠实的见证者。和朋友们度过的充实且惬意的每一天,同样是我大学时光中最美好的记忆。在此,谨向我的朋友们表示我的真挚谢意,生活因你们的存在而不那么枯燥乏味。

在这四年间,并没有因为所经历过的起起落落而骄傲自满,抑或一蹶不振。它们都是我成长过程中的养料与补给。感谢所有对我的褒奖与批评,正是有了它们的存在,我才得以是现在的自己。

我想感谢亚德诺半导体公司,你们丰富的技术文档与教程是电子工程师与初学者的良师益友。贵公司先进的产品与技术向我展示了"超越一切可能"这一座右铭的意义,并激励着我朝着自己理想的技术方向不断前进。

论文完成之际,我要特别感谢我的导师李老师,李老师在论文的写作中给予了最大程度的指导与帮助,在此我谨向我的导师致以最深的敬意与感谢。

我还要感谢我的家人对我的支持与关怀。无论我做何决定,他们一直都坚定地站在我的身后,是我最坚强的后盾与最温暖的港湾。

最后,我想感谢所有在科学前沿披荆斩棘,挑战其极限的工程师与科学家们,是你们让人类拥有了无限的可能性。

此地一为别,孤蓬万里征。愿我在往后数不清的日子里,任凭世界如何改变,都能拥有这求知若渴的初心与对抗狂风暴雪的勇气。

参考文献

多数为各种数据手册和参考设计,辅以部分论文和书籍

- AN-140:Basic Concepts of Linear Regulator and Switching Mode Power Supplies

- AN-159:Measuring 2nV/√Hz Noise and 120dB Supply Rejection on Linear Regulators

- AN-280:Mixed Signal Circuit Techniques

- AN-423_CN:直接数字频率合成器AD9850的幅度调制

- AN-756: Sampled Systems and the Effects of Clock Phase Noise and Jitter

- AN-837_CN:基于DDS的时钟抖动性能与DAC重构滤波器性能的关系

- AN-1070:Programming the AD9833/AD9834

- AN-1214:High CMRR Circuit for Converting Wideband Complementary DAC Output to Single-Ended Without Precision Resistors

- AN-1396_CN:如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度

- AN-4566:Extending the DAC performance of STM32 microcontrollers

- MT-001:Taking the Mystery out of the Infamous Formula, "SNR = 6.02N + 1.76dB," and Why You Should Care

- MT-002:What the Nyquist Criterion Means to Your Sampled Data System Design

- MT-031:Grounding Data Converters and Solving the Mystery of "AGND" and "DGND"

- MT-085:Fundamentals of Direct Digital Synthesis(DDS)

- MT-101_CN:去耦技术

- W.R.Bennett, 1948, Spectra of quantized signals[J].Bell System Technical Journal:446-471

- CN-0156:用于AD9834波形发生器(DDS)的幅度控制电路

- CN-0304:低功耗DDS波形发生器

- Brendan Cronin, 2012, DDS Devices Generate High-Quality Waveforms Simply, Efficiently, and Flexibly[J]., Analog Dialogue:46-01

- David Hunter, 2014, Two New Devices Help Reinvent the Signal Generator[J].Analog Dialogue:48-10

- Datasheet:TLV702 300-mA, Low-IQ, Low-Dropout Regulator

- Datasheet:LP5907 250-mA, Ultra-Low-Noise, Low-IQ LDO

- Datasheet:MAX889,高频、稳压型、200mA、反相电荷泵

- Datasheet:AD8130,Low Cost 270 MHz Differential Receiver Amplifiers

- Datasheet:OPAx211 1.1-nv/√Hz Noise, Low Power, Precision Operational Amplifiers

- Datasheet:AD9834,20 mW Power, 2.3 V to 5.5 V, 75 MHz Complete DDS

- Datasheet:STM32L431XX,Ultra-low-power Arm® Cortex®-M4 32-bit MCU+FPU, 100DMIPS,up to 256KB Flash, 64KB SRAM, analog, audio

- Keysight Technologies, 2018, Understanding Phase Noise Needs and Choices in Signal Generation[Application Note].

- RM0394:STM32L41xxx/42xxx/43xxx/44xxx/45xxx/46xxx advanced Arm®-based 32-bit MCUs

- UM1725:Description of STM32F4 HAL and low-layer drivers

- UM1722:Developing applications on STM32Cube with RTOS

- Ken Gentile and Rick Cushing and others, 1999, A Technical Tutorial on Digital Signal Synthesis[J]. Analog Devices

- Jimmy Hua, 2019, Output Noise Filtering for DC/DC Power Modules, Texas Instruments

- LC Filter Design, Texas Instruments, 2016

- 杨建国,2018,《新概念模拟电路》-亚德诺半导体,西安交通大学电工电子中心

- 樊昌信.曹丽娜,2010,《通信原理》,国防工业出版社

- Arthur.B.Williams, 1986, 电子滤波器设计手册, 电子工业出版社

- David.A.Patterson,John.L.Hennessy, 2015,《计算机组成与设计》,机械工业出版社