还记得我们曾经做过一个18位精密电压源模块吗?

那仅仅是个功能演示,相当于DAC芯片的EVM。无论是输出精度、使用灵活性、稳定性,我觉得都有提升的空间。于是EmoeCalibrator就诞生了。

过去的两年时间里🐟一直在断断续续地打磨EmoeCalibrator这个项目,从原理验证到校准、精确测试以及软件系统的搭建,可谓是下足了功夫。今天让我们来一起更进一步,打造计量级精度的电压校准源吧。

本文目录

0-设计目标

既然是计量级的电压校准源,我们的目标就不是常规的DAC能实现的了。

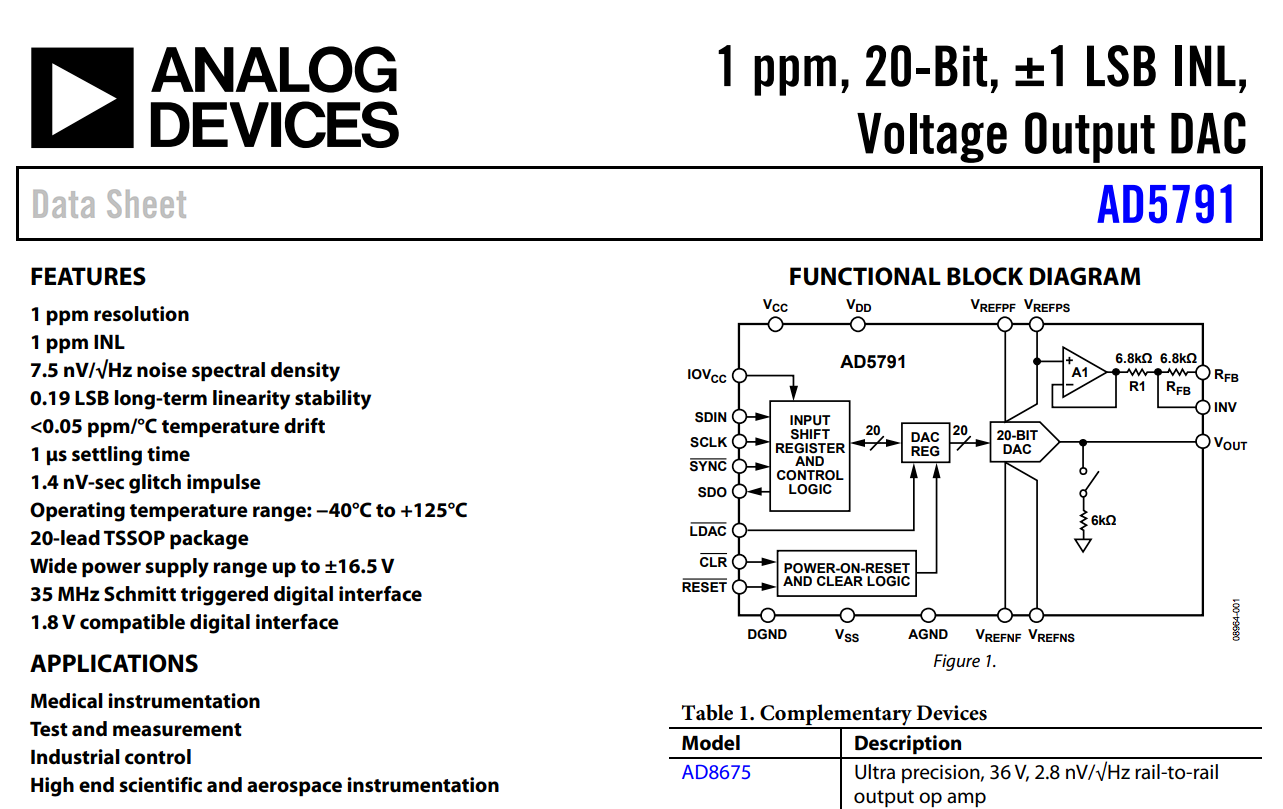

目前世界上最高精度的商业DAC器件是ADI的AD5791B和TI的DAC11001B,他们都是20-bit分辨率,双极性输出,并且积分非线性误差达到了 1ppm of Fullscale。

我们可以来计算一下其对应的指标。以AD5791为例,先作出如下假设:

- 基准使用+10V和-10V输入

- 输出范围-10V至+10V

这样我们可以计算出此DAC的分辨率达到了 19.07uV,积分非线性误差为满量程的1ppm意味着其设定精度可以达到20V*1ppm = 20uV。

听起来似乎还不错?在±10V的范围内分辨率达到了19.07uV,并且误差大致就在1个LSB以内,那可以说是相当理想的DAC了。

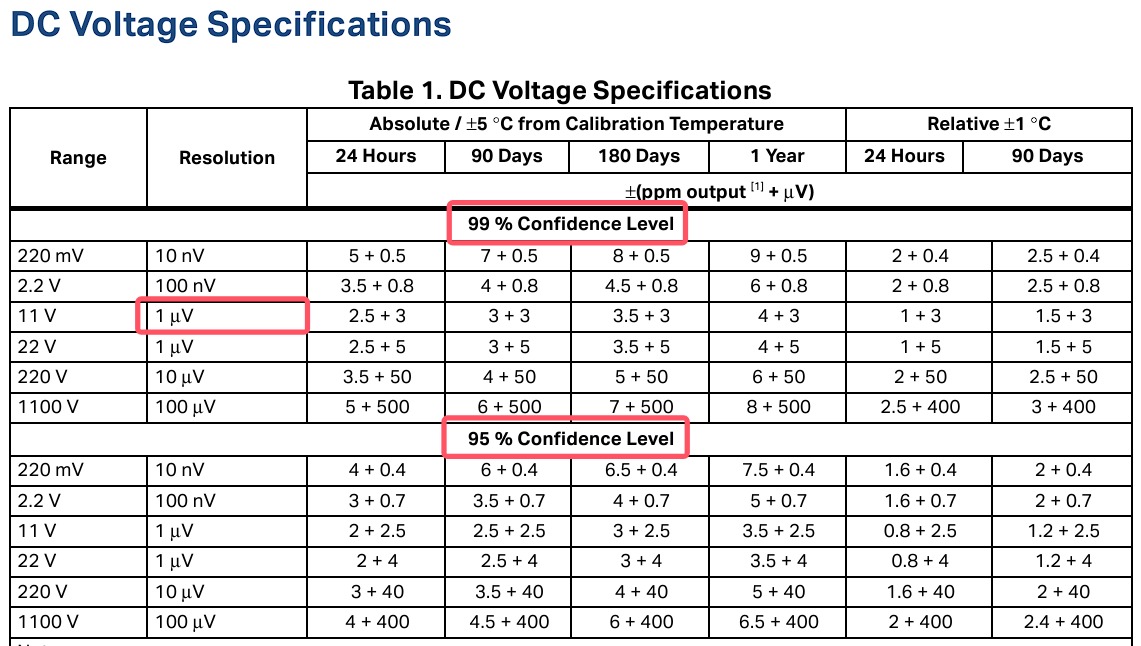

然后让我们把目光转向Fluke 5730A,这是一款多功能校准器,是业内公认的计量级校准设备,几乎是最好的设备之一了:

Fluke5730A在11V量程内的输出分辨率达到了1uV。这相当于是5791/11001的近1/20。

0.1-误差正态分布

另外注意到这个99%和95%置信度了吗?其实这来源于正态分布:

作者 M. W. Toews – 自己的作品, based (in concept) on figure by Jeremy Kemp, on 2005-02-09,CC BY 2.5

这个指标的意思是说:假设Fluke做了100台这样的设备,校准完成后对其进行长时间的测试,将其各项误差指标做统计学处理。因为每台仪器的误差都是 相互独立互不相干 的,可以近似为正态分布,那么测试结果中有99台设备的误差可以达到某个等级(上图表),这99台中又有95台的指标更好些,能达到更高的等级(下表格),另外1台指标不合格的设备就作废了。

厂家给出的这类指标是让用户了解设备的误差分布情况,给用户提供一个参考,让用户自己判断是否满足要求。

0.2-我们的指标

说回我们的项目,我们既然想做计量级校准源,那么我们就直接对标5730A好了。我也要做10V量程下1uV的分辨率。奥里给!

分辨率1uV,那么短稳、长稳和热迟滞指标呢?在做出来之前我没有底,这个指标大概只能氪金去提升(用LTZ1000等级的基准配合金属封装气密的箔电阻作为系统参考),是一笔不小的开销。所以我们且行且看。

1-高分辨率DAC技术

2025年的AI技术进步很快,我们也来尝尝鲜(Deepseek):

Q:我想实现一个24位分辨率的DAC,有什么好的方案推荐吗?

可以看出,AI的回答沾了些边,适合给外行了解技术方向,但在硬件领域,AI不能提供任何可靠的工程指导。可能是因为实际的硬件工程过于复杂,且 缺乏成体系的高质量资料供AI训练(软件的各种库和编程语言有官方文档和开源项目,硬件呢?),所以AI并不能掌握这类知识与经验。

🐟观察到现在很多博主都在使用AI生成的内容攥写文稿,写写小说就算了,技术内容还是别来碰瓷了。

不过AI提供的思路大致正确,想要做高分辨率DAC,有几条路可以走:

- 加权拼接

- 高分辨率PWM DAC

- 高速DAC抖动(算是一种另类的PWM)

- 无脑氪金上高等级的无源分压器拓展分辨率

- 催催ADI/TI的Analog Design设计更高分辨率、更高精度的DAC,同时催台积电或者某神必产线升级更牛逼的模拟工艺

其中,第四种我们就不考虑了,这种力大砖飞的思路实在是不太cost effective。你堆砌一大堆箔电阻确实能做到很高的分辨率,但…何意味…高速DAC抖动算是PWM的变种,我们可以给他合并一下。于是我们就剩下这两条路可以走了:加权拼接 和 PWM DAC。(第五种也不是我们能催得动的,可能人类的科技树点到这里就很难进行下去了)

2-经典的电压校准源

要说经典的此类仪器,那还得是Fluke的5700(5730由于我没找到拆解和内部结构分析,不在讨论范围内。

我们来看看Fluke自己的介绍(装逼):

5720A:超级高精度多功能校准器

自 1988 年面世以来,5700A系列多功能校准器系列产品便获得了全世界对其性能、可靠性以及质量的公认,也因此成为了政府与工业领域内进行电气校准的理想校准器选择。

5700A系列是福禄克公司生产的、经过大量测试证明、极为可靠的、高精度校准器。5700A系列已经在全世界的范围被看作是校准器的标准,具有很高的价值,并且该系列产品在稳定性、实用性、耐用性等方面得到用户的广泛认可。很多用户拥有该产品20年以上并仍在使用中。

嗯,一台仪器传三代,工程师下岗了仪器还在上班。(老HP的射频仪器也有类似的待遇)

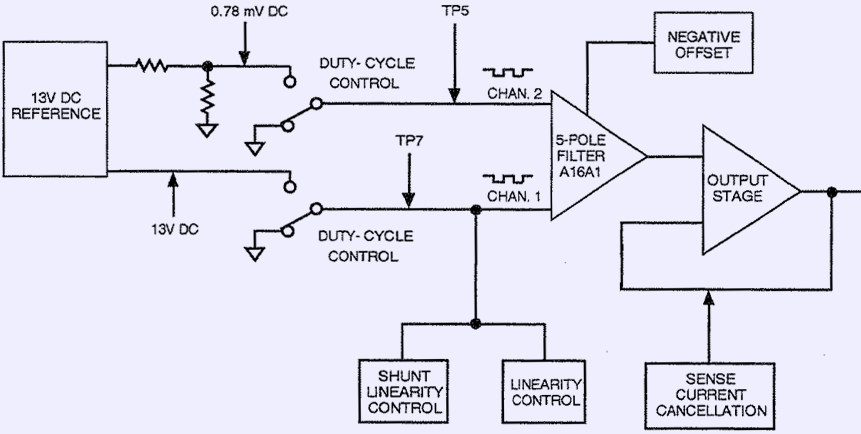

EEVBLOG 上有人对5700这一经典型号做了完全拆解分析;我们从拆机图和官方给出的Manual中的电路图可以发现,Fluke使用了大量定制的混压电阻网络来保证其各个部件的精度、匹配与温度稳定性。核心的PWM基准大致如下图:

主基准生成13V的参考电压,然后通过一个精密匹配的分压器得到780uV的参考电压,随后将这两个参考电压进行PWM斩波,通过某种方式将其线性相加后再经过低通滤波,就可以得到高分辨率的直流可调输出。

原理看起来很简单,但是你要问我为什么Fluke这机器里用了那么多电路呢?框图中看似简单的一个Block,实际的实现都可能极为复杂。那我来问你一些问题吧):

- 13V电压基准部分如何设计?

- 怎么保证有源滤波器的直流漂移极其稳定几乎无漂移?

- 如何保证PWM开关的一致性?

- 如何补偿非线性度?图中的2个Linearity Control的原理是什么呢?

- 如何产生高分辨率的PWM信号?

- …

这只是从设计框图中简单挖掘的疑问,实际设计制作的时候,会碰上数十倍之多的问题需要解决。

这也是人和AI共有的局限性,厂家就算给你了电路图,但是由于其过于复杂、定制器件繁多且没有参数,图放在你面前你也做不出来。

国内也有此方面的研究,有人实现过较小范围内的PWM基准,但我也没找到具体的资料。这一个技术路线我觉得挺好,他不需要高分辨率的DAC器件,但是设计难度过高,系统过于复杂,我暂时没精力折腾这条线,留待以后再说吧)

我在网上搜资料的时候看到了一位博主写的使用STM32的DAC抖动来实现更高分辨率的文章,感兴趣的读者可以去看看 用单片机内部12bit DAC实现 20bit DAC效果。不过我感觉他是来带货那个采集卡的,哈哈哈。

3-ADI的Demo

3.1-AN86

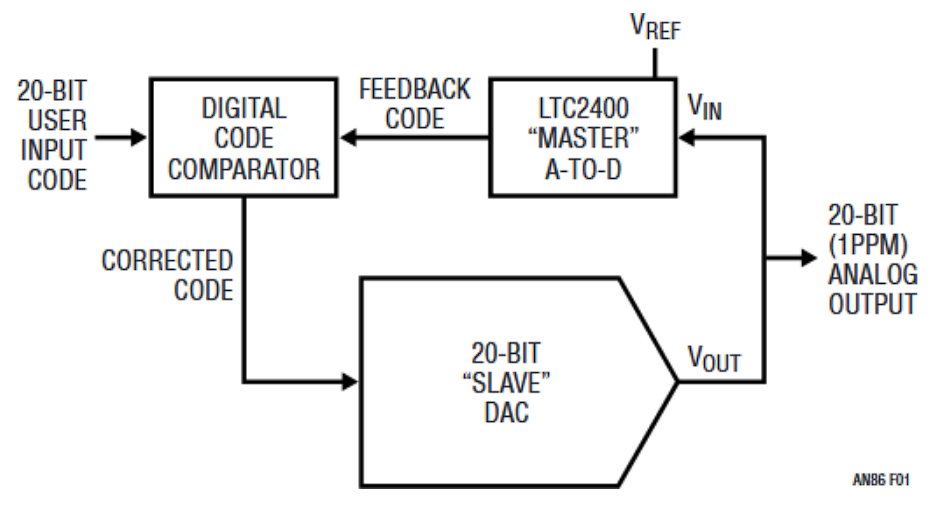

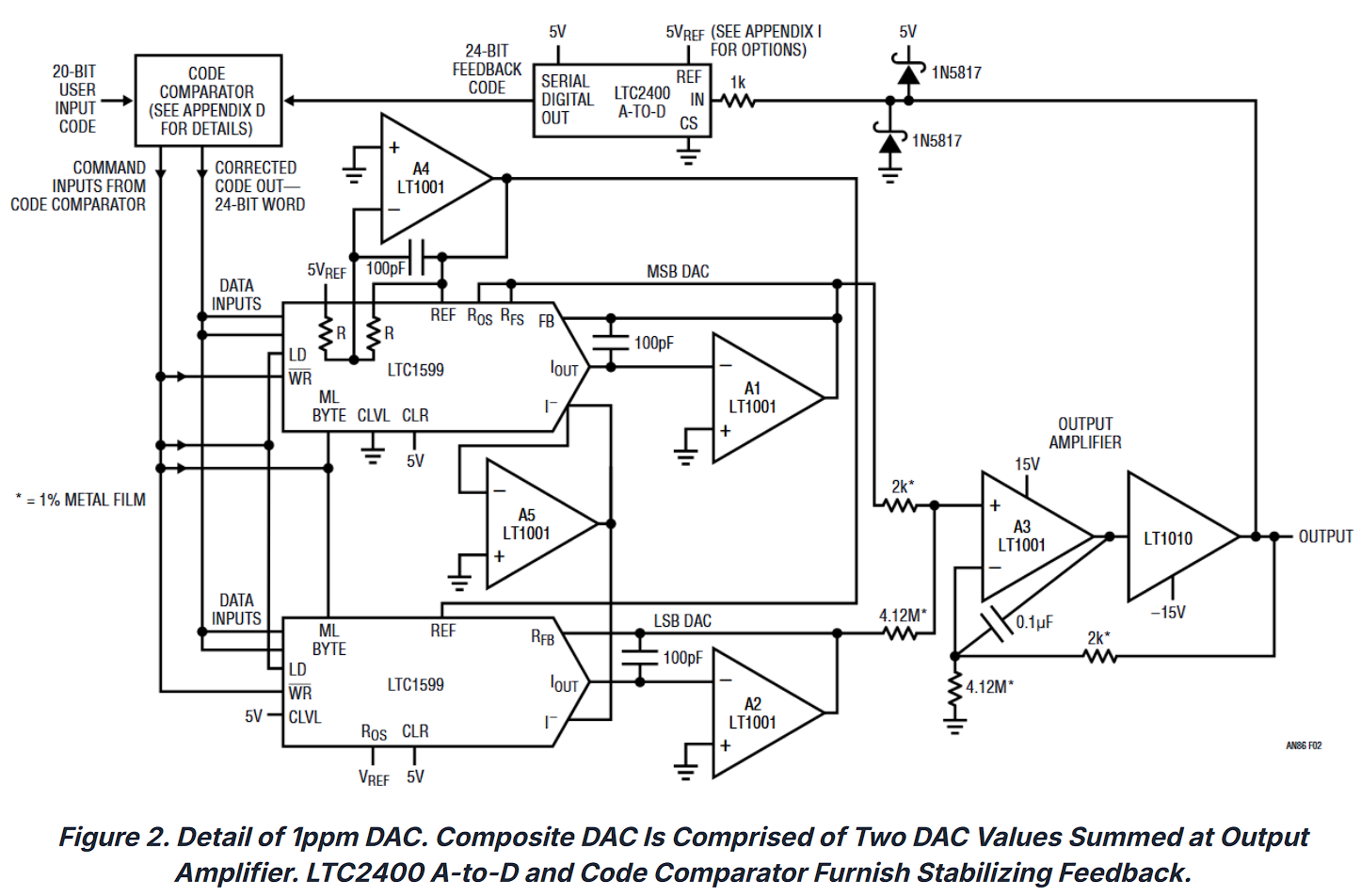

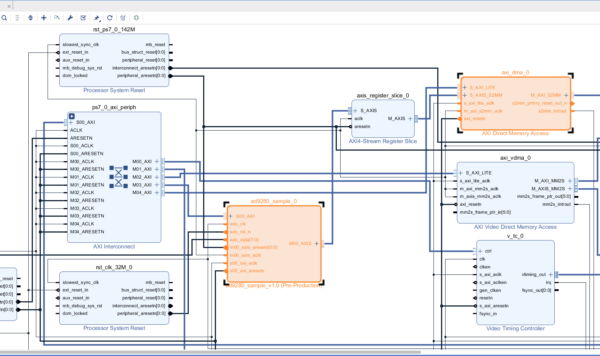

Jim Willams等人曾经在AN86中设计过一个ADC闭环的加权20-bit DAC,此刻的日期是2001年,ADI还没有推出5791。所以受限于时代,当时想要实现20bit分辨率的DAC,只能依靠24bit的高精度ADC去做闭环。

他的拼接是这样的:使用2个16位的乘法DAC,输出双极性电压,然后通过一个加权比例极大的同相加法器将2个电压相加,得到更高位的输出,然后在输出使用一个高线性度的24bit ADC实时监测输出,修正拼接DAC的误差。

这种依赖闭环的加权方案的精度上限主要取决于ADC信号链,DAC可以用差一些的(但DNL要保证小于1LSB),但ADC差了系统天花板就到那了。并且这种闭环修正精度的方案将严重影响整个DAC的建立时间,因为他需要一定的时间来完成ADC的高精度修正。

不过对于静态直流应用,这个方案还是非常不错的,因为高精度ADC现在可选的比DAC多多了,来个现代化升级改造,做一个20位低温漂的直流源也是轻而易举。

3.2-更暴力的方案

ADI在2024年发布了一篇技术文章:How to Achieve Ultrahigh Accuracy when Designing a 21-Bit Precision Voltage Source

这篇文章里直接将2个AD5791的输出等比例相加(并联),实现了一个1+1=2的效果,拼出了个21bit的DAC,

在他们的测试方案中,能实现±1ppm的INL,这也可以预见(2个非相干的误差源叠加在一起,误差会更小些),我觉得比较难绷的是文章的作者说,用4个5791就能拼出22bit辣!和之前我们说的用一堆箔电阻拼好机有异曲同工之妙…好吧,可能是要为公司产品带货,倒也正常吧…

4-我们的尝试

得益于群友DualMono和另外一位神秘群友的支持,我拿到了一片DAC11001B、AD5791B和ADR1399。感谢赞助~

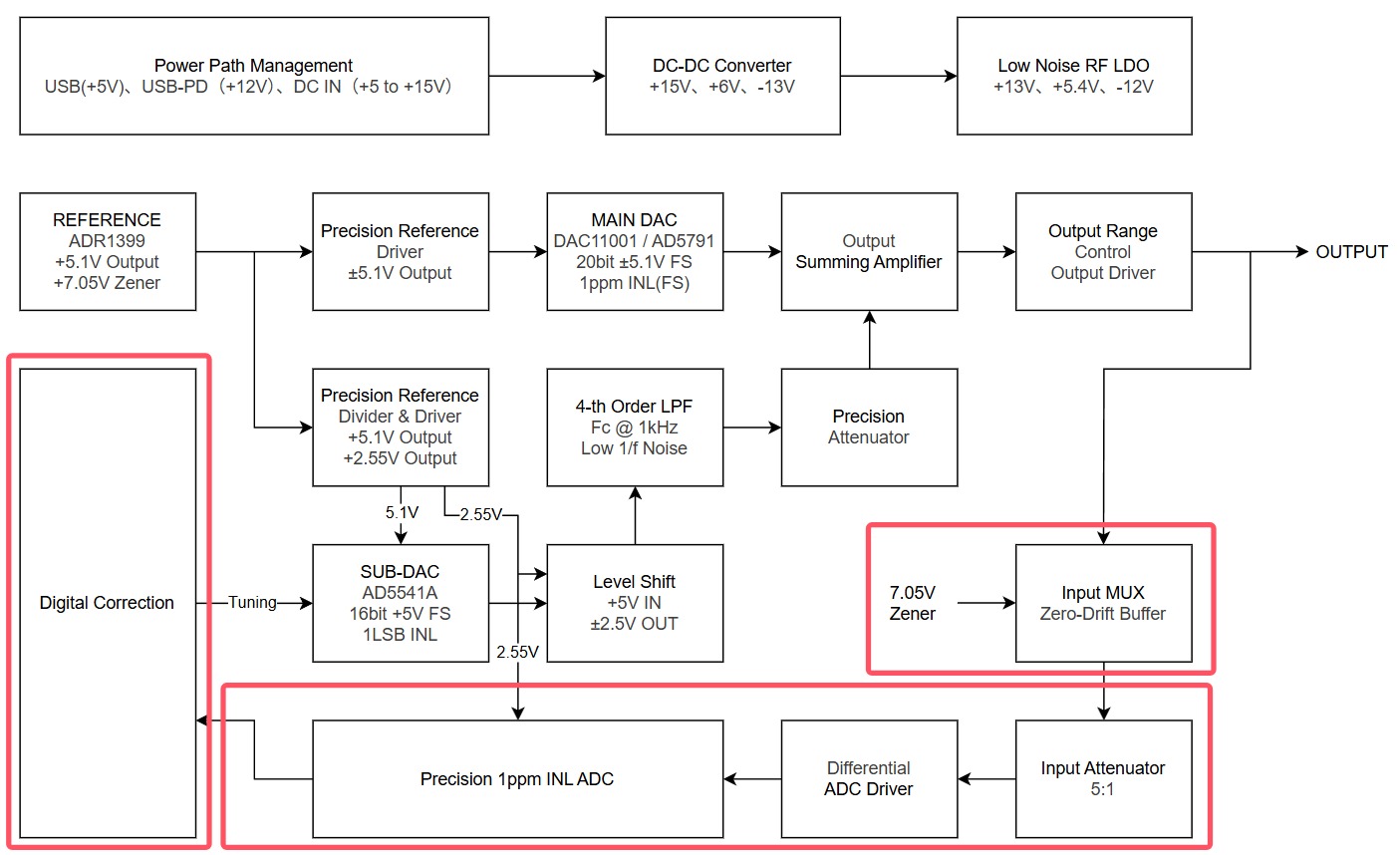

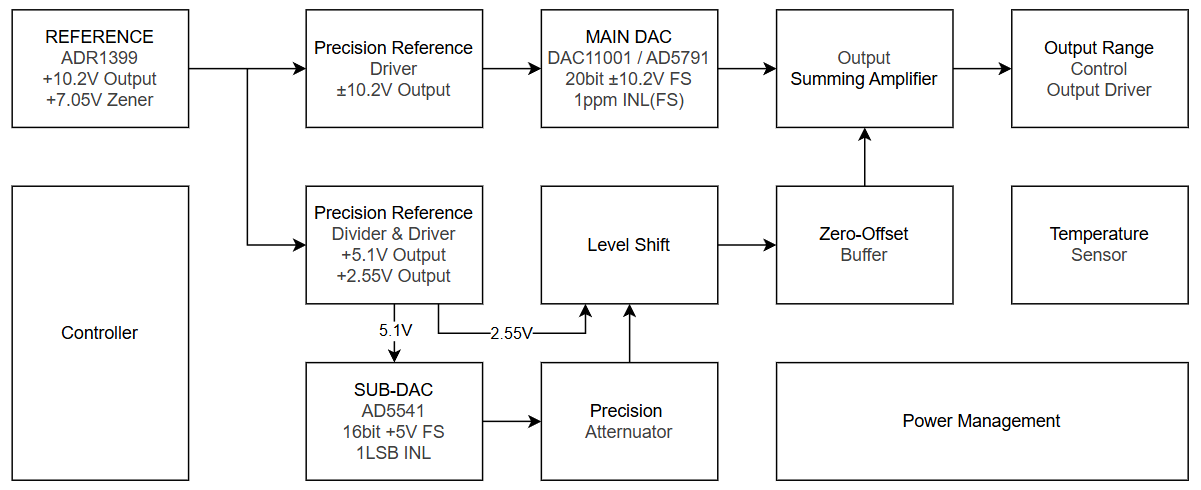

在参考了上面的2种拼接方案后,我也设计出了一种方案:

使用LM399/ADR1399作为系统基准,用DAC11001/AD5791作为主DAC,选了一个16bit的从DAC,将这两个DAC的输出通过精密电阻网络+运放求和,实现拼接的功能。

初版为了验证的目的,我将DAC加权拼接、DAC抖动以及数字闭环修正的电路全画到了系统设计框图上。但最后偷懒了,就在PCB上画了个加权拼接,红色框图内的内容全没做。(非常像开题报告踌躇满志,中期答辩支支吾吾,课题收尾潦草完事)

4.1电路细节

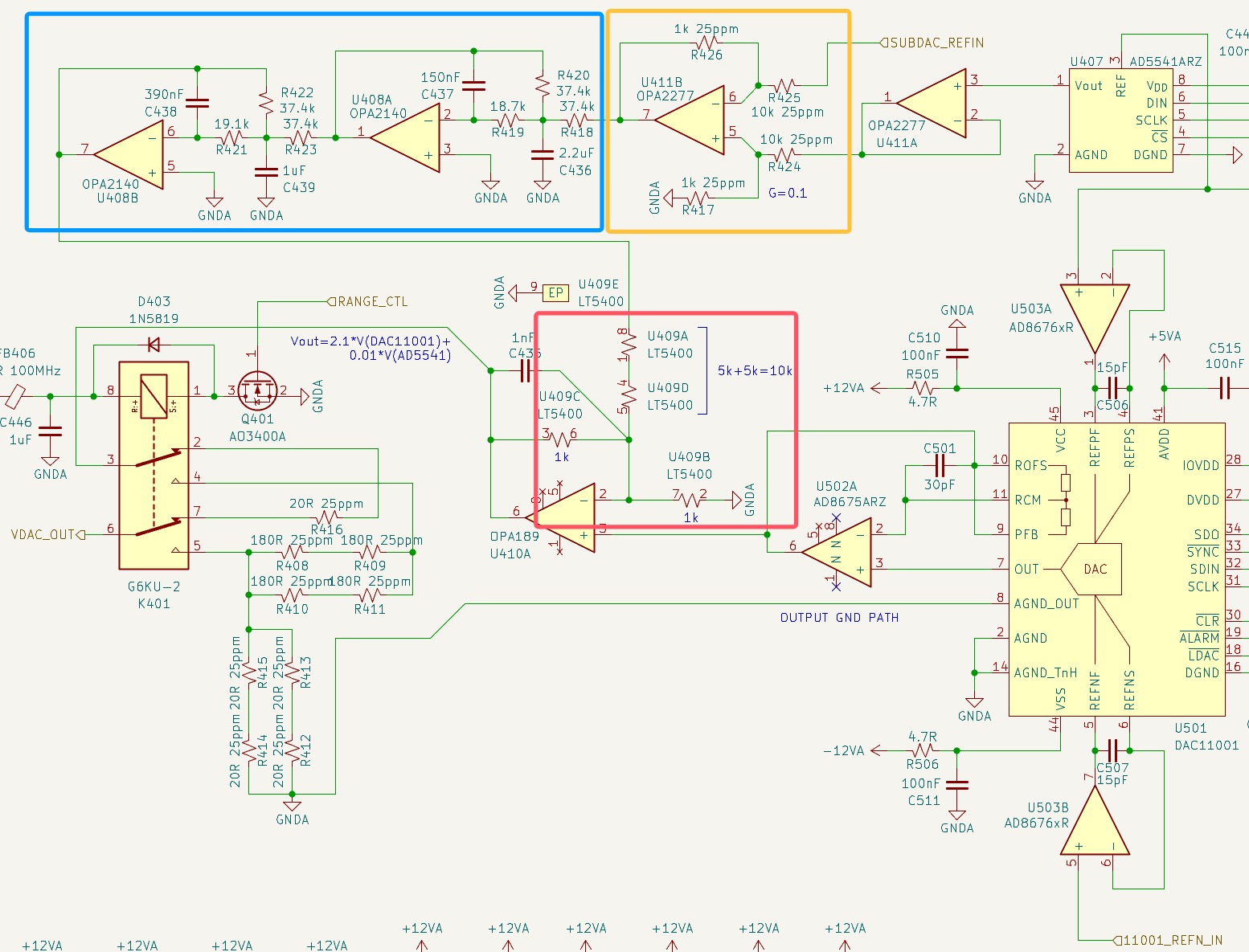

此处我设计的是用主DAC出±5.1V,从DAC出±2.5V,从DAC的输出经过衰减、滤波后再与主DAC按照比例求和,在加法器那一级,主DAC的信号还会被放大2.1倍,从而实现±10V输出。

电路图中:

- 黄框-差动放大器对从DAC的输出进行移位+衰减,将0至5V输出搬移到-250mV至+250mV范围内

- 蓝框-4阶有源ButterWorth滤波器,对从DAC的输出进行滤波

- 红框-带偏置的同相放大器,通过精密温漂匹配的电阻网络LT5400,可以让这个加法器的比例温漂做到0.2ppm左右。

- 输出我还做了个无源衰减器,不过最后没用上。

最终的输出电压与2个DAC的关系是:

V_{OUT} = 2.1*V_{DAC11001} + 0.01*V_{AD5541}需要注意的是,上式中AD5541的电压是经过电平搬移后的,5541的输出范围是0-5.1V,搬移后是-2.55V至+2.55V。

其余的没啥好看的,都是手册里的典型应用电路,照着抄就完了。

但是!layout要注意遵从精密电路的layout法则,详情可以参考我之前的总集篇:精密电路硬件设计指南

4.1.1-误差分析与选型要求

在对这个电路做误差分析时,我们要假定一些条件:

- 假设加法器是理想的(不引入非线性)

- 基准电压源稳定

- 各个运算放大器较为理想,作为DAC输出驱动时,不引入非线性误差(基准驱动因为工作在固定电位,误差固定)

于是,2个DAC的噪声、非线性误差、增益温漂、失调温漂都会跟随加权系数线性变化,从DAC那路还有一个差动放大器和有源滤波器,这两个电路的误差一并代入计算。所以到这里其实就比较简单了,列一列加减乘除就出来了。

但是事实可能并不会如我们所愿,在ppm量级,平时被忽视的种种误差都可能破坏我们系统的精度。比如运放的输入共模范围、输入失调电压/电流随共模输入的变化趋势有没有突变、变化斜率如何、运放加法器/滤波器/差动放大器处选用的电阻值大小是否合理,会不会引入过大热噪声/失调电压,等等一系列工程问题…关于这块的讨论我们暂时不展开,待我日后写个运放的应用手册总集篇。

Calibrator对于核心元件选型有大致如下要求:

- 主从DAC符合手册指标,INL和DNL在1个ppm/LSB内(即2个DAC单调)

- 基准电压源必须低温漂、低长期漂移,否则1ppm精度在短期稳定性中都实现不了,后级电路指标再好也没意义了。

- 不同位置的运放选型合理,根据功能和连接的前后电路重点侧重不同的指标来选型。

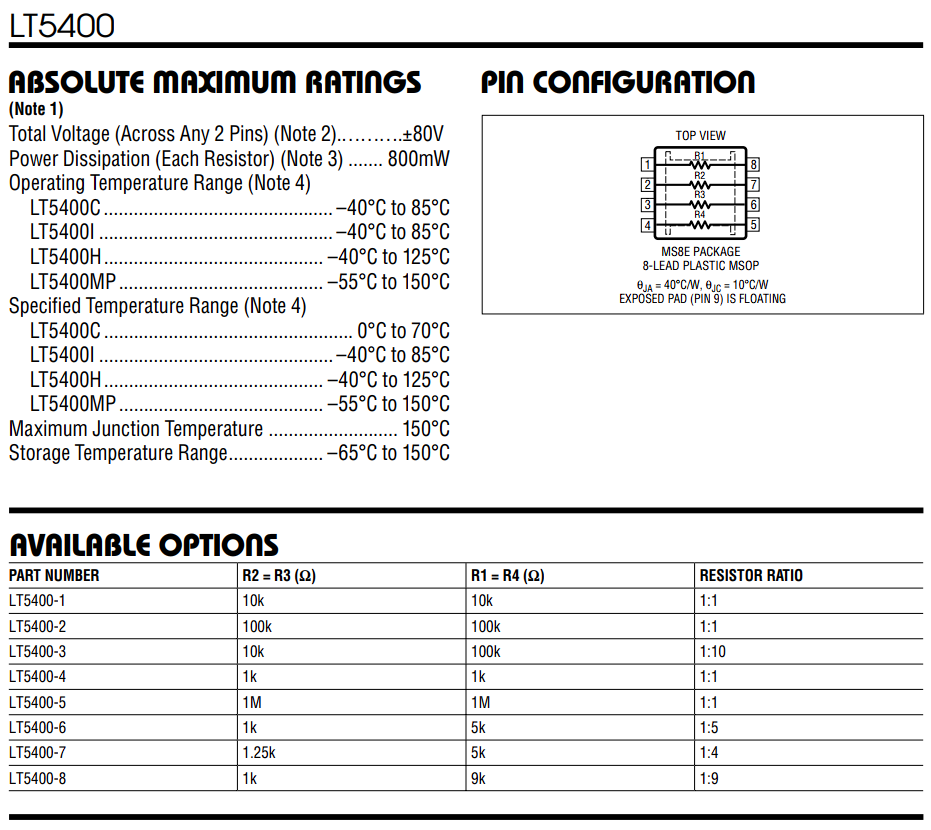

- 输出的加权求和使用的电阻必须严格温漂匹配,最好是使用LT5400这类硅上匹配的精密电阻网络,这样能确保系统的输出温漂指标,同时这里的电阻匹配的长期稳定性也决定了系统的长稳。

- 别买到假芯片调不出来还怪我)

4.1.2-基准电压源

上次我们做18位精密电压源时,使用的基准是LCC封装的LTC6655,虽然这颗基准噪声很低,温漂性能优秀,但是其长期稳定性不太符合我们对计量级的需求,更适合用在精密AC采集、超低噪声等应用中。

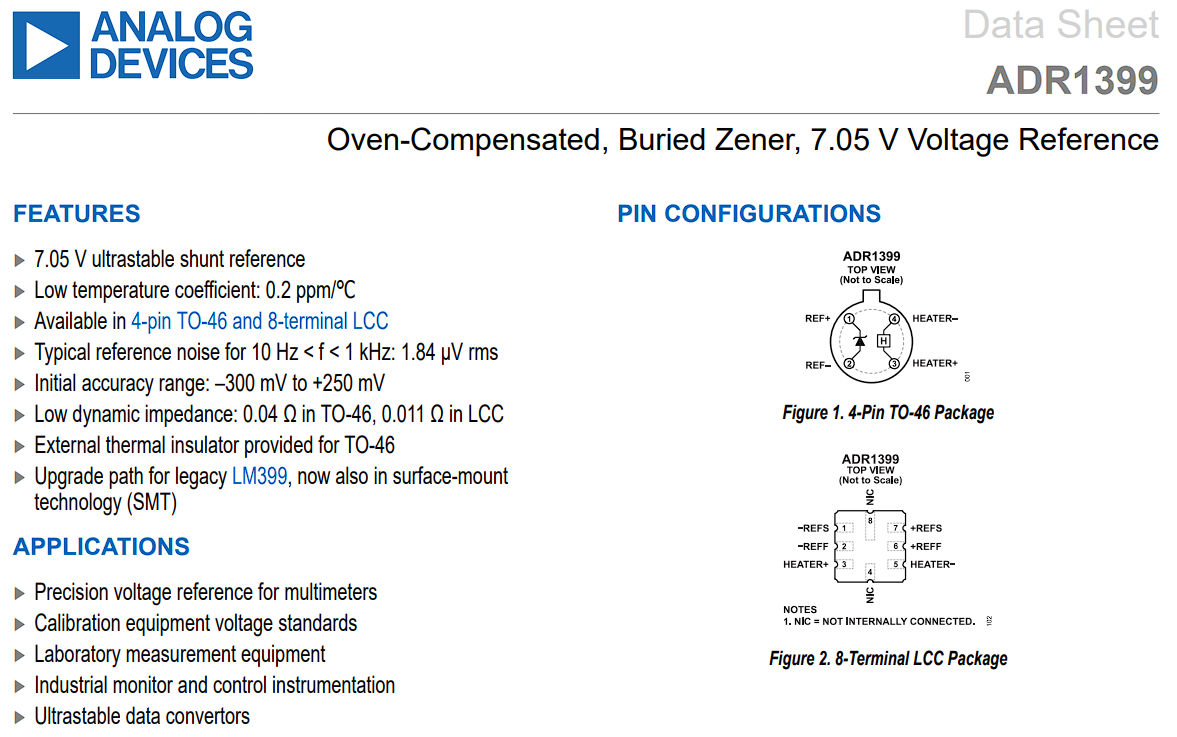

这次我们的基准电压源使用的是ADI的ADR1399,ADR1399是LM399的升级版本,在噪声、ZENER的动态阻抗、等方面有明显的进步,并且推出了可以SMT的LCC版本,温漂和长期稳定性也非常优秀,很适合我们的应用。

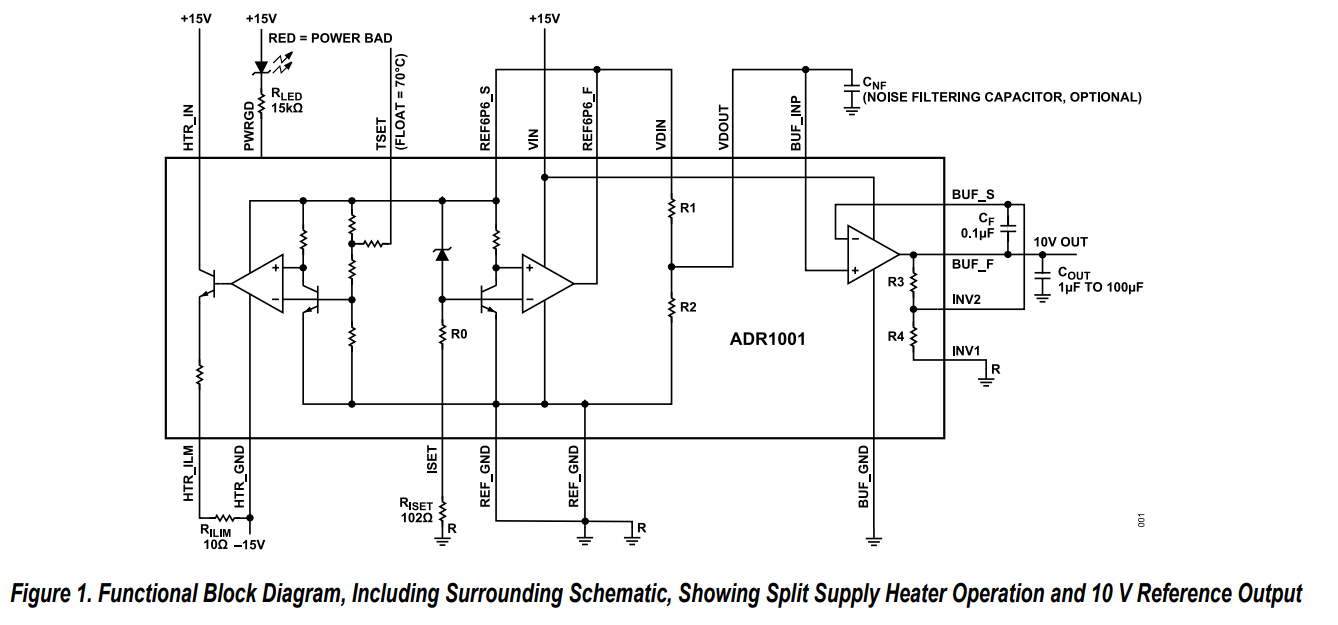

当然,如果追求极致的性能,应当使用LTZ1000或ADR1000这两颗基准。ADR1000也推出了新的ADR1001,内部集成了5V分压,外围配置仅需要一个箔电阻设定ZENER的工作电流,可以直接为现代工艺的ADC/DAC提供5V基准,并且提供一个10V升压输出。属于是为小体积量身定制的新一代超级电压基准。这里出于成本考虑,使用ADR1399的罐封版本。

另外🐟也了解到ti最近也出了ADR1001的对标芯片——REF80,看起来也是个不错的基准,不过🐟没有品鉴的渠道/机会了。。

4.1.3-电阻网络

这里如果按照FLuke的思路,应该就是自己定制精密匹配的混合电阻网络作为加权求和的无源器件了。但是那是1980s的思路了,现在的新技术有更低成本的方案:LT5400

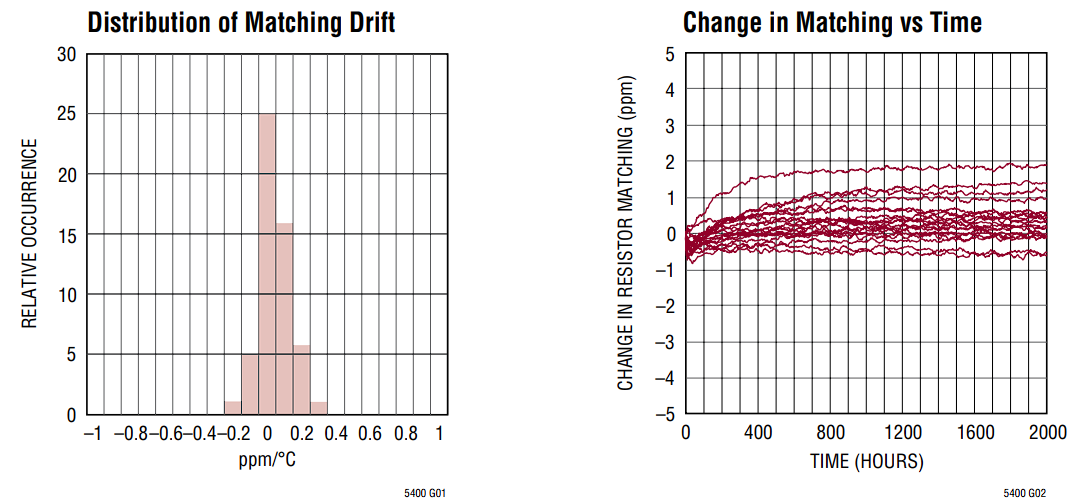

5400是在硅片上制作的4个精密匹配的电阻网络,虽然他不能保证阻值的绝对精度(绝对精度可能误差有15%之大!),但是这4个电阻由于是在同一个die上制作,意味着他们的温度是非常紧密耦合的,因此可以做到在正常工作的全温度范围内,4个电阻之间的比例变化非常小,能做到±0.2ppm/°C。要知道,如果用单独的金封箔电阻都不一定能做到这个指标(氪大金人工筛选一下可能是可以的),所以5400用在这种需要比例的电路中几乎是最佳选择(如放大器、差分放大器、加减法器、仪表放大器等)

另外由于是在die上制作,每个电阻的阻值都可以通过激光修调的方式调整,于是5400的匹配精度也是非常高的,典型的电阻比例精度能达到0.025%,即250ppm。又因为这4个电阻在一个die上,他们之间的比例长期漂移指标也非常离谱(可以理解,因为漂移的趋势和程度都几乎一样),在经过2000小时的正常工况后,比例漂移仅有2ppm。

当然,2025年的现在也不止ADI生产这类电阻了,国内也有很多厂家跟进了,比如领慧立芯的LHE5400、圣邦微的SGM9100、3peak的TPR82/86系列。

这类电阻也不光是优点,比较大的一个缺点是不耐高压。LT5400的任意2个pin之间的电压不能超过80V,所以只能在低压精密场合用用,高压还是得用体积更大些的传统电阻器去抗。

4.1.4-DAC器件

AD5791和DAC11001我觉得不用介绍太多了,我们着重介绍一下他们最重要的特性,这里我们以AD5791为例,11001的性能指标和5791没差太多,多了一个温漂补偿功能

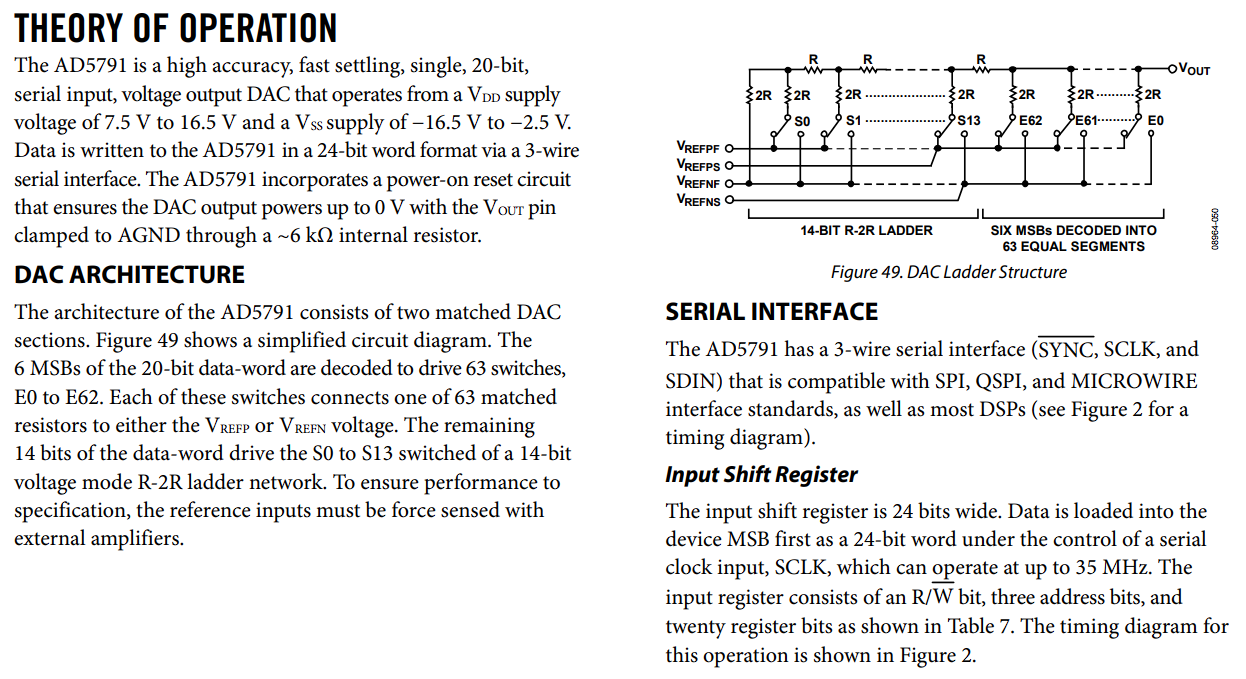

5791这类高位DAC使用的不是纯R2R架构,而是混合型R2R,高6位由63个开关控制接入匹配的63个电阻,低14位则是传统的R2R ladder,这样的架构支持双极性基准,并且5791明确要求基准输入必须由外部运放驱动,要保证sense连接(具体可查阅典型应用)

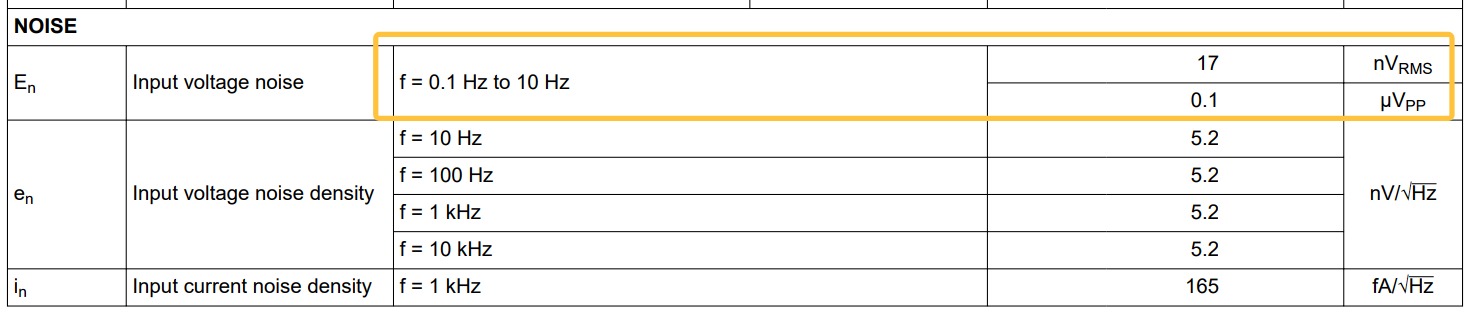

5791的核心指标如下:

- 20bit 分辨率(1ppm)

- 1 LSB线性度(约等于1ppm),不过是B级才有这个性能,A级略差,最高到4个LSB

- 线性度长稳指标 0.11~0.19 LSB,我的理解是线性度误差偏移的大小。

- 增益误差温漂 ±0.04ppm Full Scale Range / °C

- 输出压摆率50V/us,建立时间1us(到0.02%,全精度建立为止)

- 输出电压噪声谱密度 7.5nV/√Hz @ 1kHz~100kHz, 输出为midcode时(如果双极性操作,此时为0V输出)

- 输出低频噪声 1.1uVpp(0.1-10Hz,输出为midcode时)

另外使用时也要注意,5791的基准电压范围有要求,最低为5V,最高不超过模拟供电VDD-2.5V。意味着如果你想用10V的基准电压,电源要给到12.5V以上。5791的电源轨支持最高33V压差(即±16.5V),最低需要7.5V压差

我们对于主DAC的核心诉求就在于:低增益温漂、长期稳定性、低噪声、低线性度误差,最好还能快速建立。目前看来这就是我们的理想DAC选择。

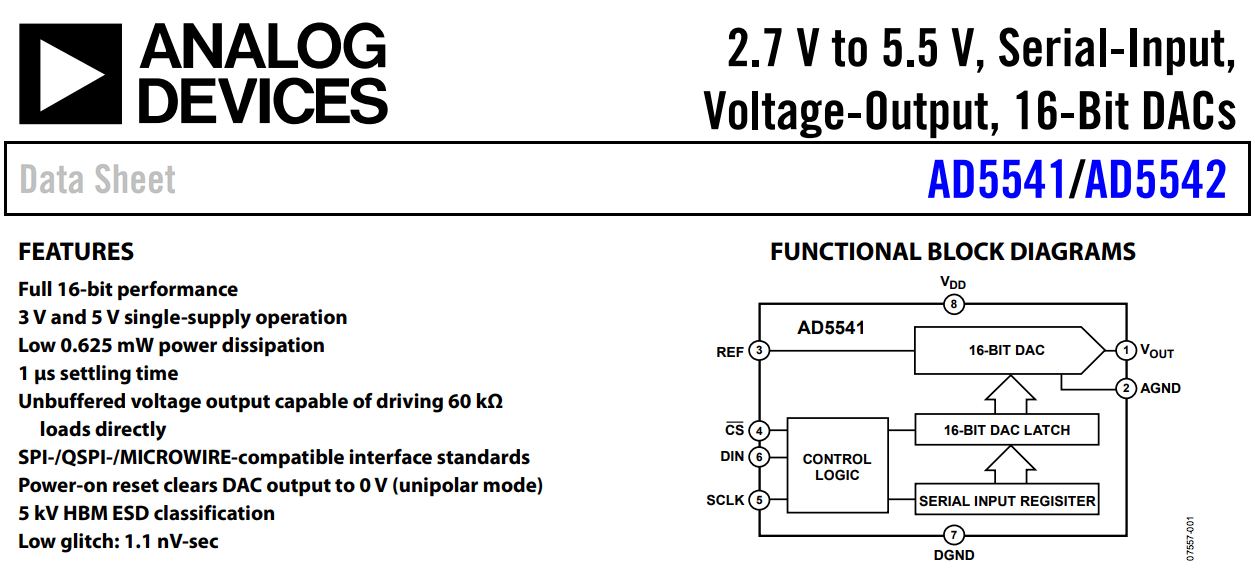

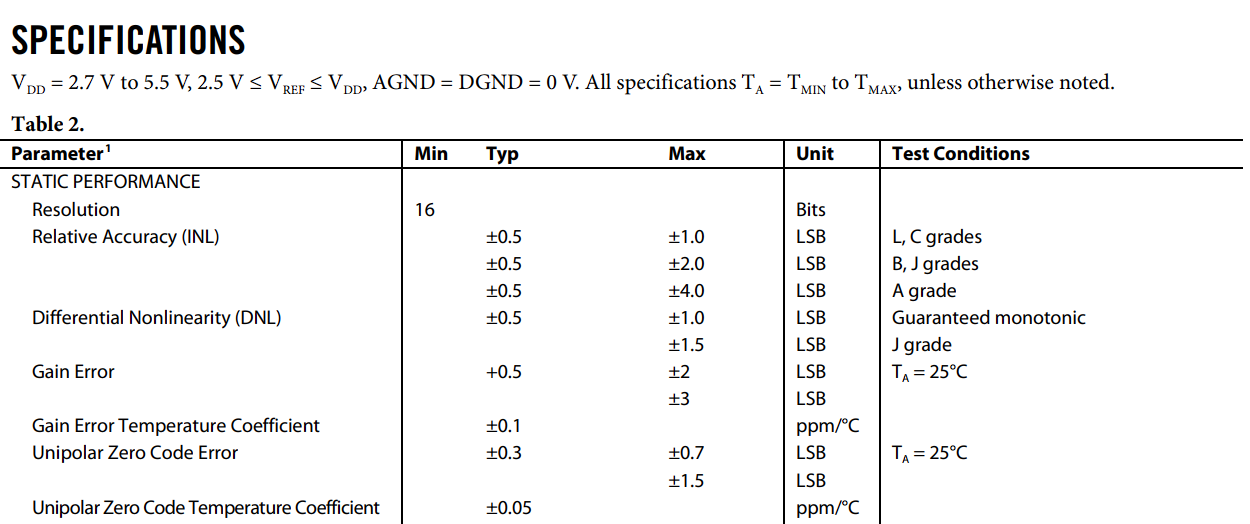

至于从DAC,由于从DAC的输出被衰减了100倍以上(依据电路设计),所以从DAC的温漂、噪声对输出的影响也会减弱相应的衰减倍数,所以对于这两个指标没有那么苛刻,但是也要尽量保证从DAC的线性度优秀,如果从DAC不单调,会对我们最终的系统误差产生较大的影响。这里我们选用ADI的真16bit DAC——AD5541

L/C级的INL保证在1个LSB以内,并且DNL保证单调,增益温漂0.1ppm/°C,算是非常优秀的DAC。

4.1.5-extra吐槽

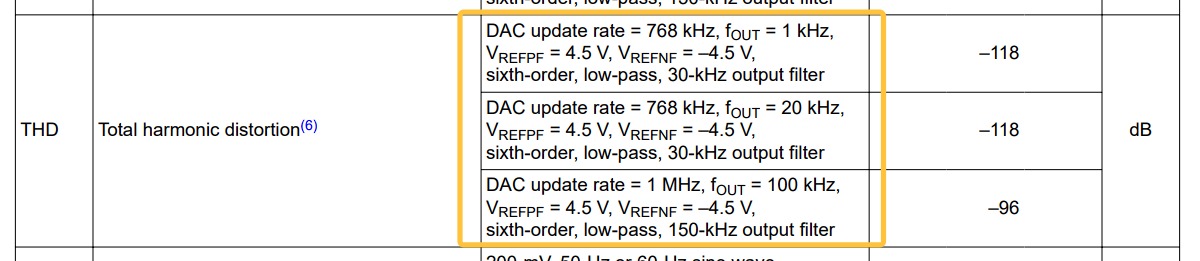

我想吐槽一下TI的数据手册…

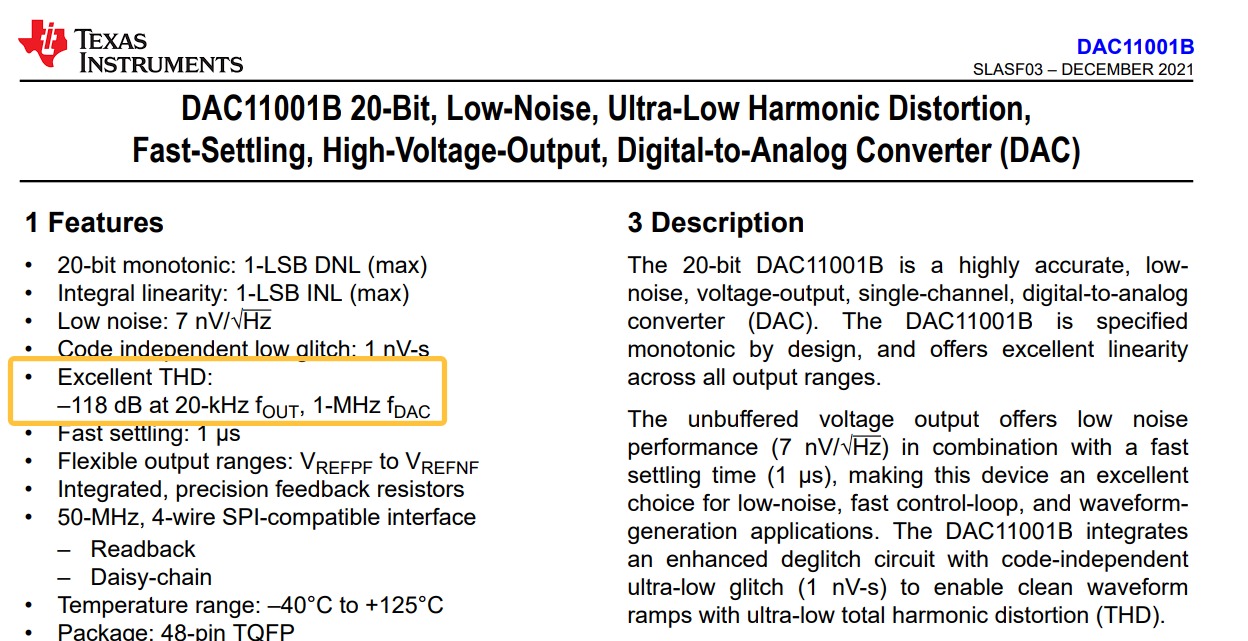

第一眼看DAC11001B的介绍,哇,-118dB的THD

然后复现了一下感觉没那么高,怎么回事呢?仔细看指标栏的测试条件:

合着你这测试还是过了6阶有源低通滤波器的…写手册嗯造漂亮数据的工程师也是高人了

4.2拼接算法

按照最终的输出关系式来估算2个DAC对输出的影响权重:

可以看到,从DAC在最终输出呈现出的1个LSB是0.778uV,勉强能满足1uV分辨率(若要实际达到,系统最小步进需要达到0.5uV以下,这可以通过改变从DAC的衰减比例来实现)。

如果用户输入一个设定电压值比如1.234567V,我们只需要给2个DAC合理地分配各自的电压就可以了。算法的流程如下:

- 根据用户输入电压值,计算出主DAC需要输出的电压,取得对应的dac code记为 C1

- 根据 C1 计算出主DAC的理想输出电压应为多少,然后与用户输入的电压作差,求出残余电压 V1

- 将 V1 作为从DAC的目标输出值,计算从DAC的Code,然后写入从DAC即可

增益、失调校准在系统层面进行;INL校准更为复杂,需要进一步讨论

4.3初步测试

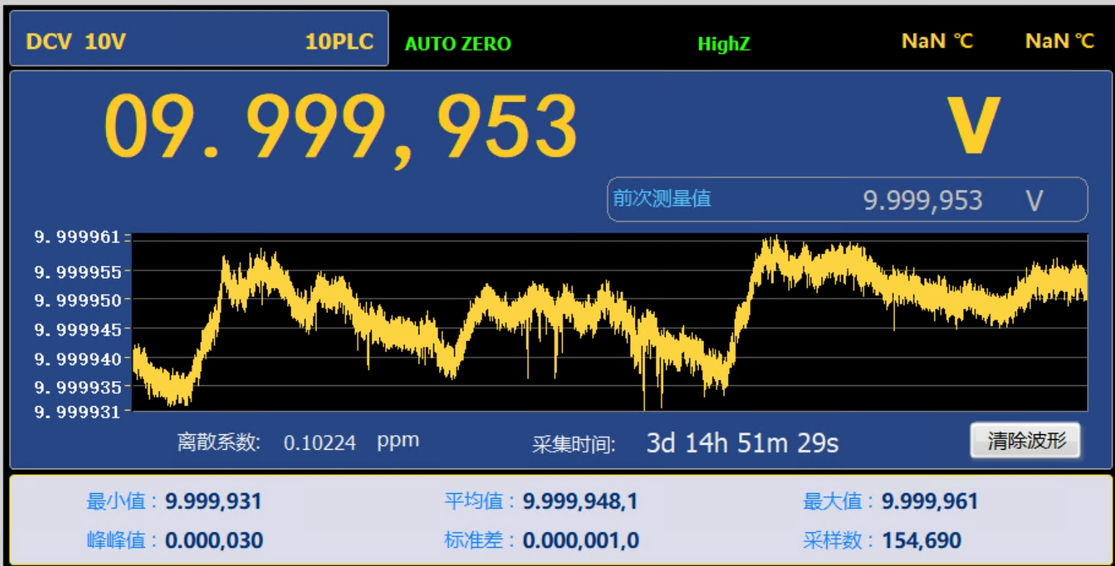

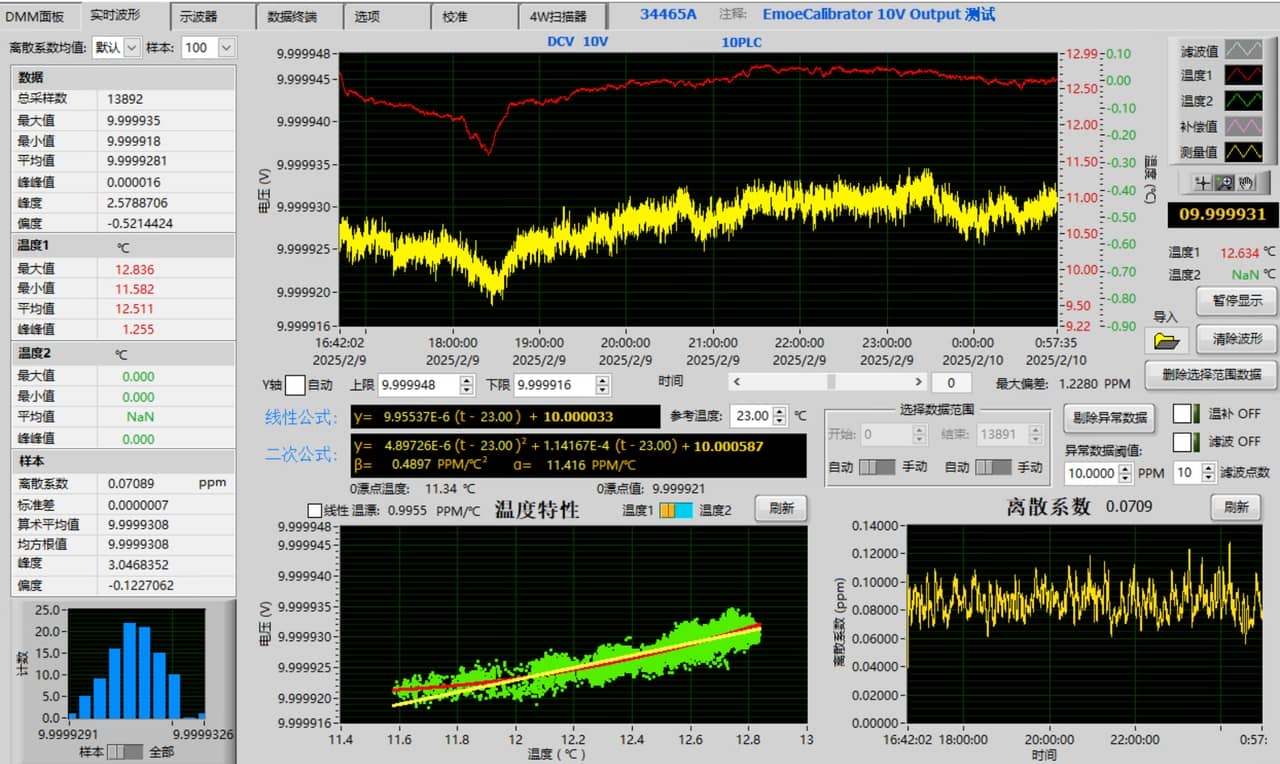

使用34465测量这一版的Calibrator输出稳定性,连续测量3天得到数据如下,能看到明显的昼夜温差带来的影响,约为1.5个ppm of Fullscale(满量程是±10V即20V的绝对值,1个ppm是20uV)

此上位机是ZDD老师开发的DMM_PC TOOL

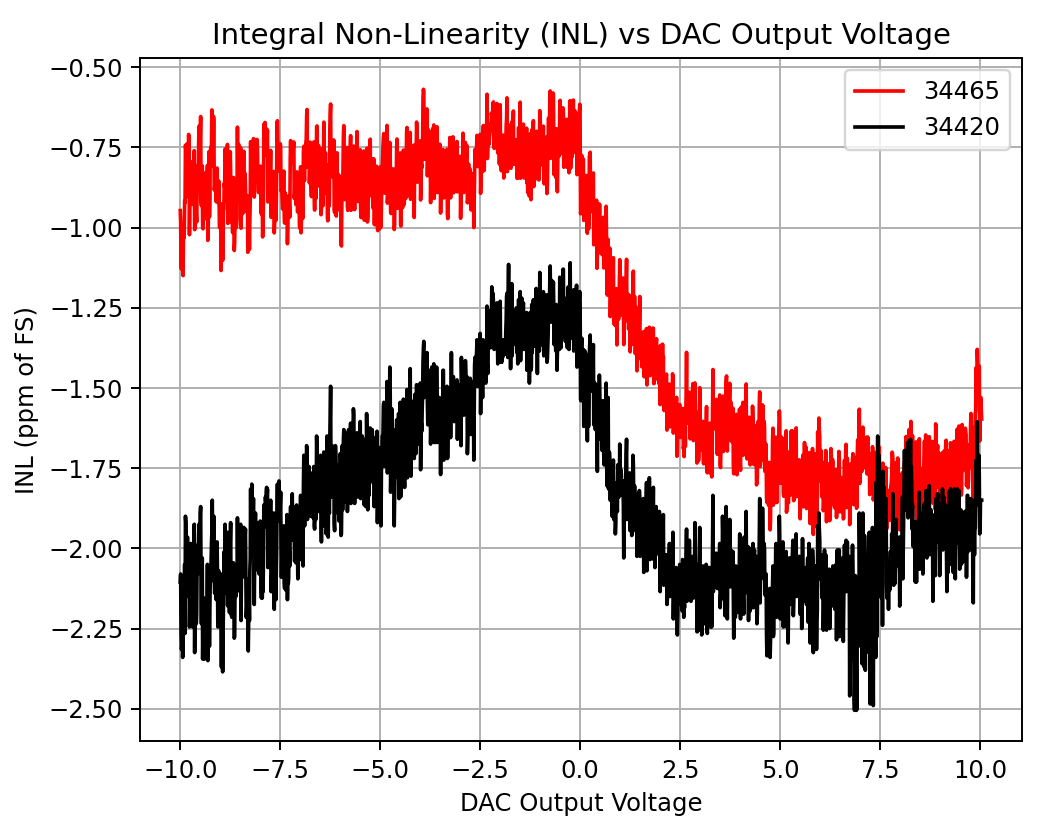

使用34465和34420这两台6位半来拷打初版Calibrator的线性度,发现有一个明显的断层出现,而且是2台表都有的现象,我怀疑是在过0转折的地方计算方法出了些问题。如果你还不知道如何测试INL,请看:精密电压源设计 中的INL测试介绍

不过大概能看出,这样拼接的DAC具有实现1ppm性能的潜力(在-10V到0V的区间内,INL曲线非常平直,且峰峰值没有超过1个ppm,34420的斜率和34465有区别是因为这俩的增益系数有微小差异,这在高位DMM系统中是正常现象,不是每台机器都是准的,我们只看INL即可)

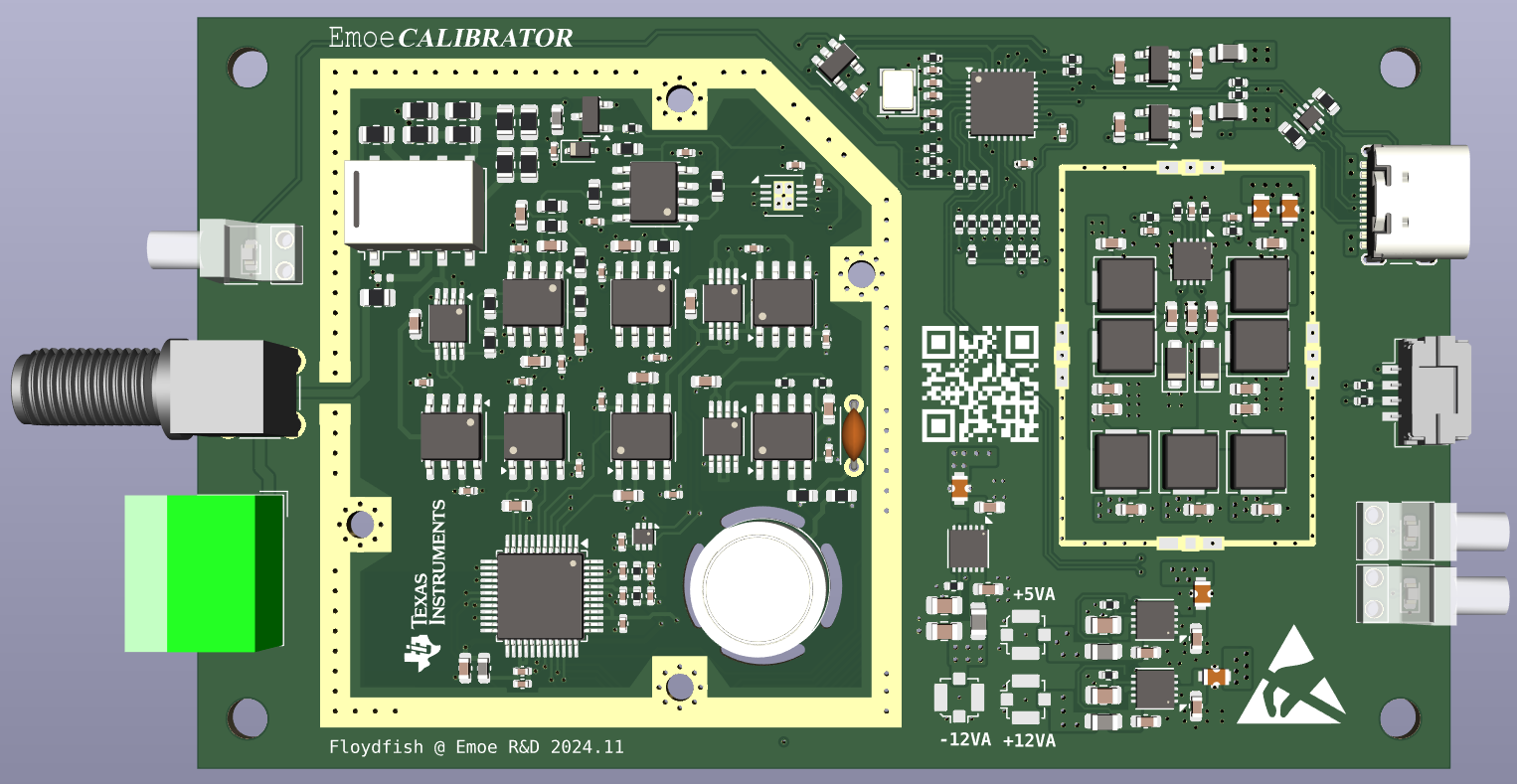

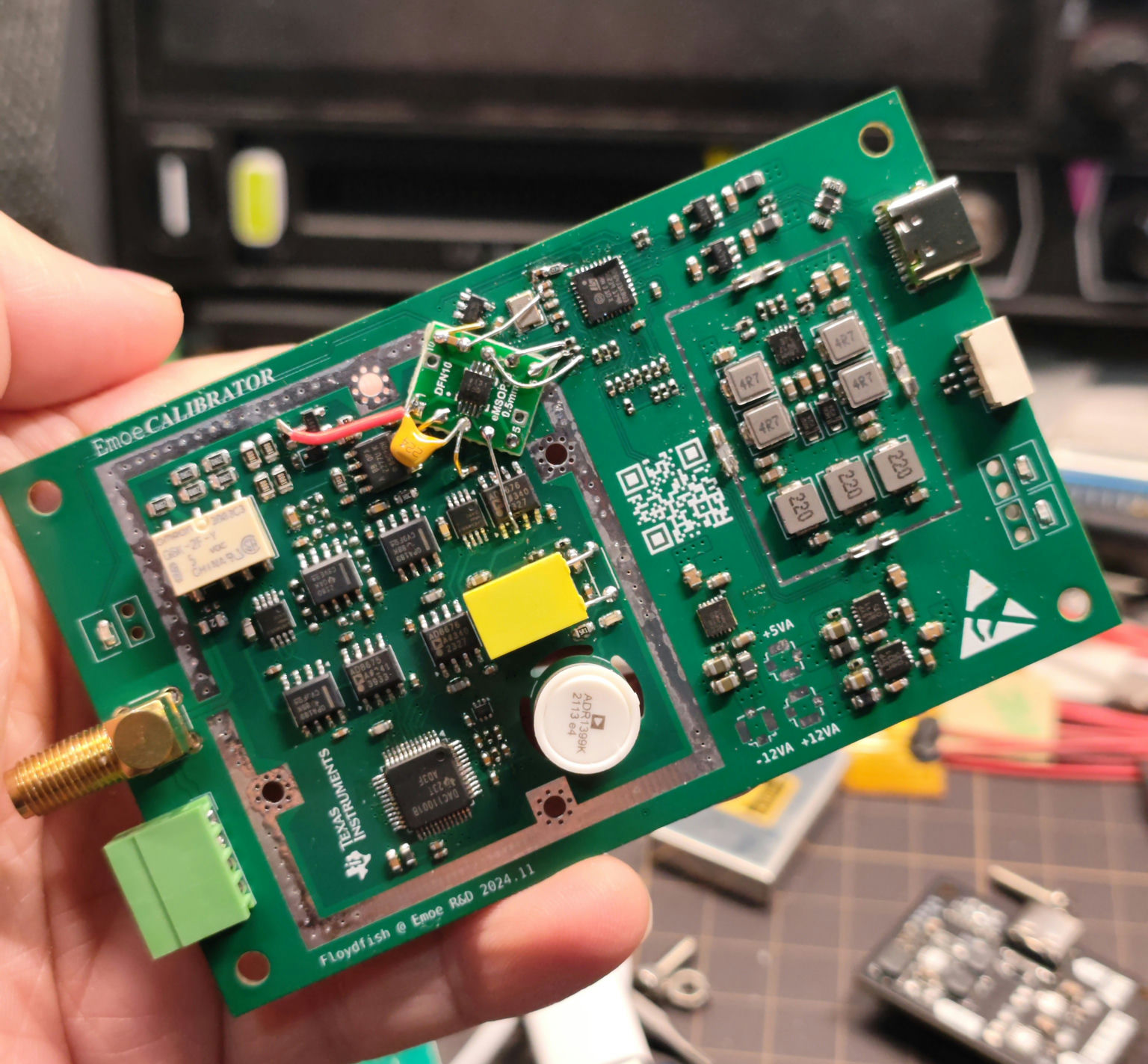

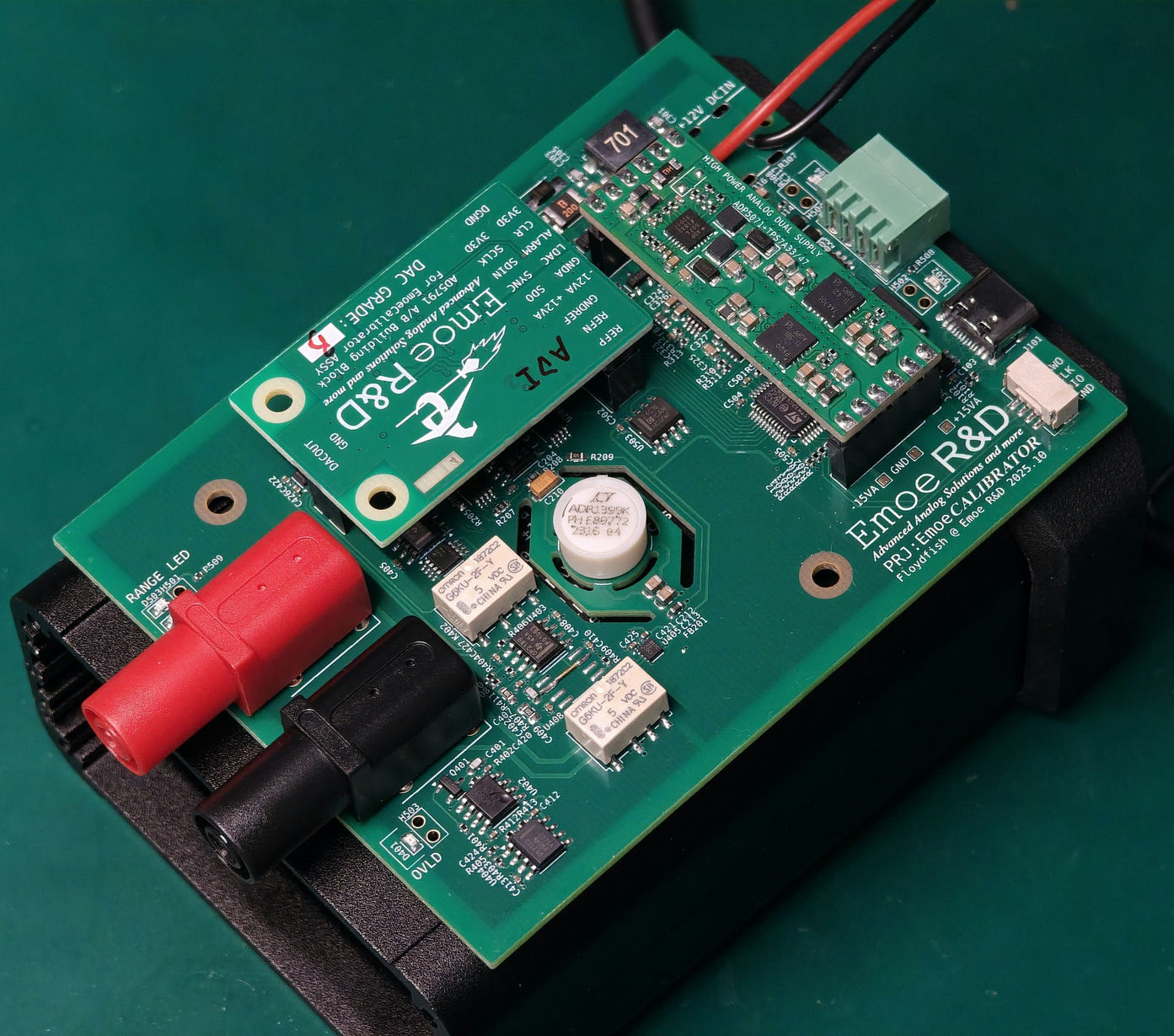

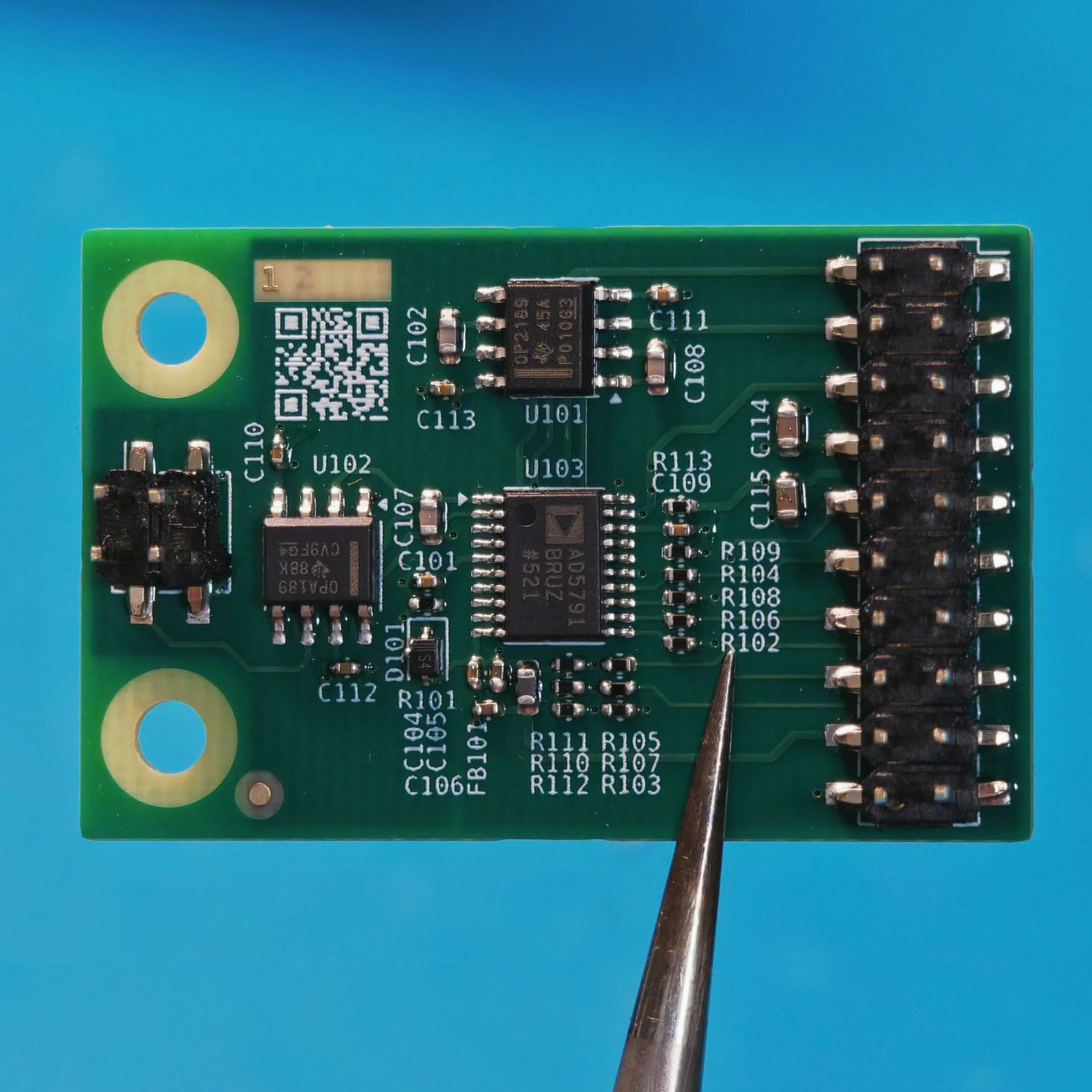

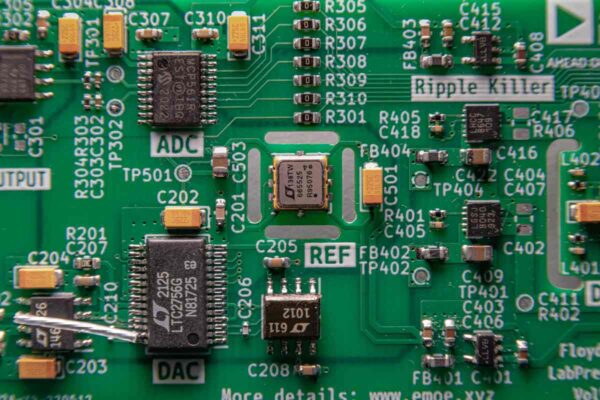

然后上一张实物图(不要吐槽那个飞线的模块,我DAC封装画错了…..):

接下来将Calibrator装入外壳,做一些简单的温漂测试:

我使用EmoeTemp(精密PT100温度采集卡)配合ZDD老师的上位机软件连接34465,测试Calibrator的温度系数,发现竟然高达1ppm/°C。我觉得我的设计中不存在如此大温漂的东西,于是看了一下34465的spec,即使开启自动校准后,10V档位的温度系数也高达 2±1ppm/°C。

测到这里我已经发现,34465这类6位半万用表的性能已经不足以测试我的Calibrator了。

4.4-初版设计总结

通过上述测试虽然没有完全测出Calibrator的真实性能(仪器拉了),不过我们至少可以确信这种拼接方案是可行的,并且他具有一个天生的优势—— 快速响应,因为他的精度不依赖ADC来闭环控制。意味着在某些对实时性有要求的地方,用这种架构的DAC可以兼顾高精度、高分辨率和快速建立、快速响应的需求。

不过在主从DAC码值切换时产生的跳变(或Glitch Impulse)我们还没有测量,之后我们的计算和DAC更新算法可能还有朝着这个方向优化的空间。

另外,我们也可以看出,这种方法体现出的是主DAC的非线性度性能。如果主DAC的非线性度较大,同样也会造成最终精度不及预期。

5-更高精度

经过初版验证方案ok后,我对DAC拼接技术充满了信心,于是开启了下一版的设计。

这一版我对架构做了些微调:

- 基准电压变动为+10V以上

- 输出加权比例改动

- 电源树改动

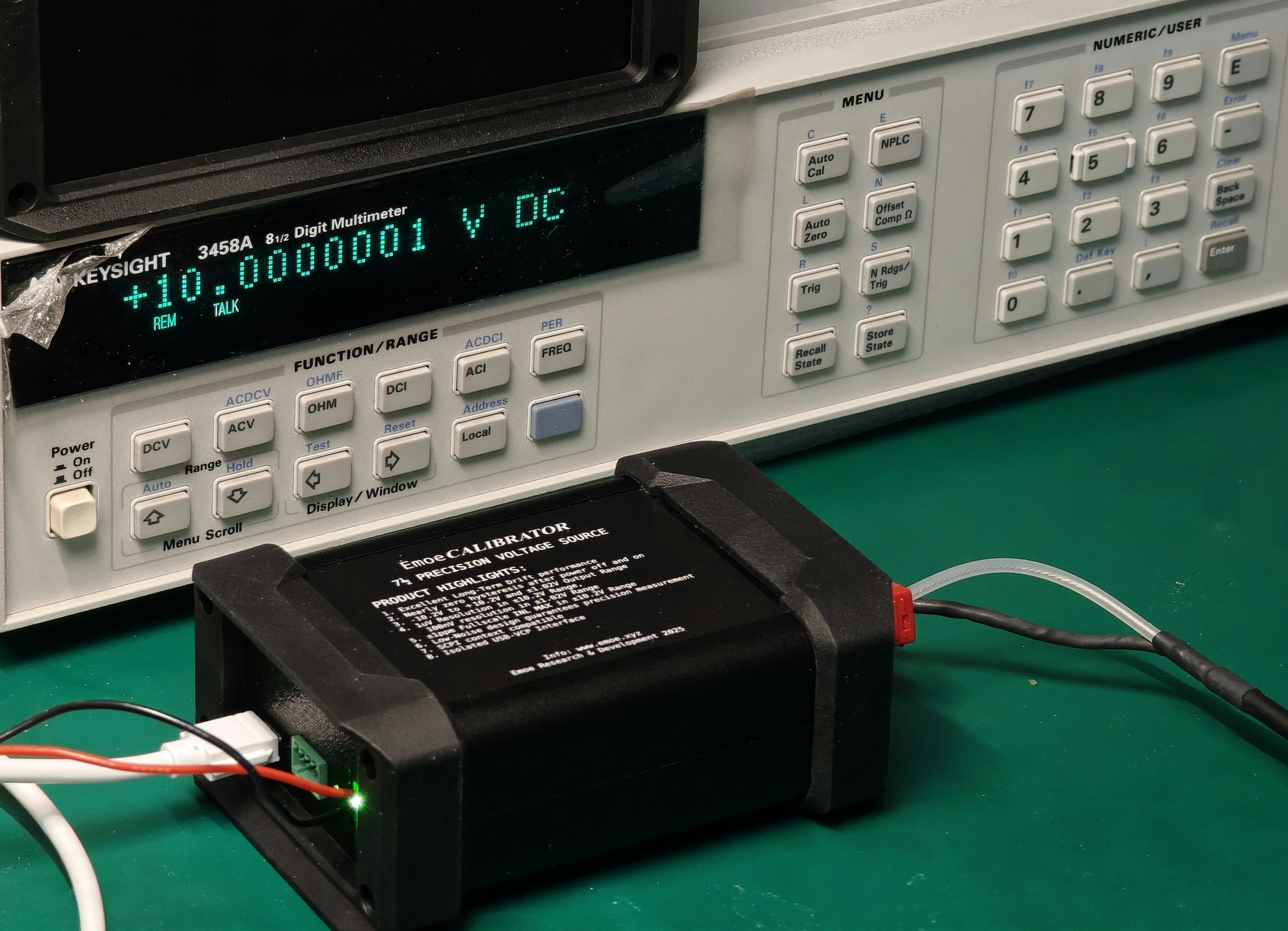

同时,还从群友那里借来了直流精密界的至尊霸主——Keysight 3458A,太基米了!

这一版设计中我将USB接口设计成隔离的,整个系统由外部12V电源供电(其实+9至+15都行),模拟部分的电源由我之前设计制作的超小体积低噪声模拟双电源模块提供,非常的节省空间,悬空起来增加了热阻,也不容易影响到精密模拟部分电路的温度(其实那边发热本身也不小,哈哈)太基米了!

同时,我还将DAC设计成了模块化可插拔设计,方便直接更换DAC进行验证。同时也可以兼容AD5791和DAC11001两种高性能DAC,太基米了!

在上一版中,🐟还没来得及做系统级的校准和软件框架的完善工作(病了不想动),这一版也都加上了,那么我们来看看完整版Calibrator的性能如何:

5.1-来自3458的究极拷打

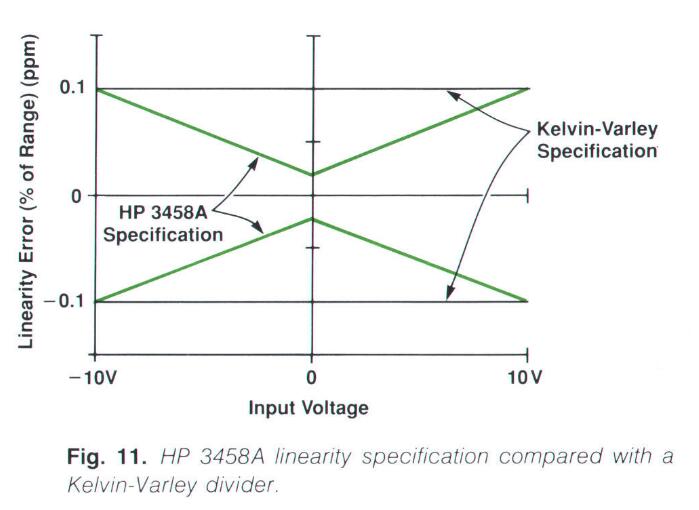

我们之前了解过,3458的INL指标是DMM中最好的,几乎没有之一:微观尽头——精密信号测量:Intro

所以,在做ppm level的线性度、精度测量时,3458绝对是不二选择(keysight的广告费结一下谢谢~)

当然,我也没有条件同时借到3台3458来做联合测量以提高置信度,所以就用一台3458的结果看一下吧:

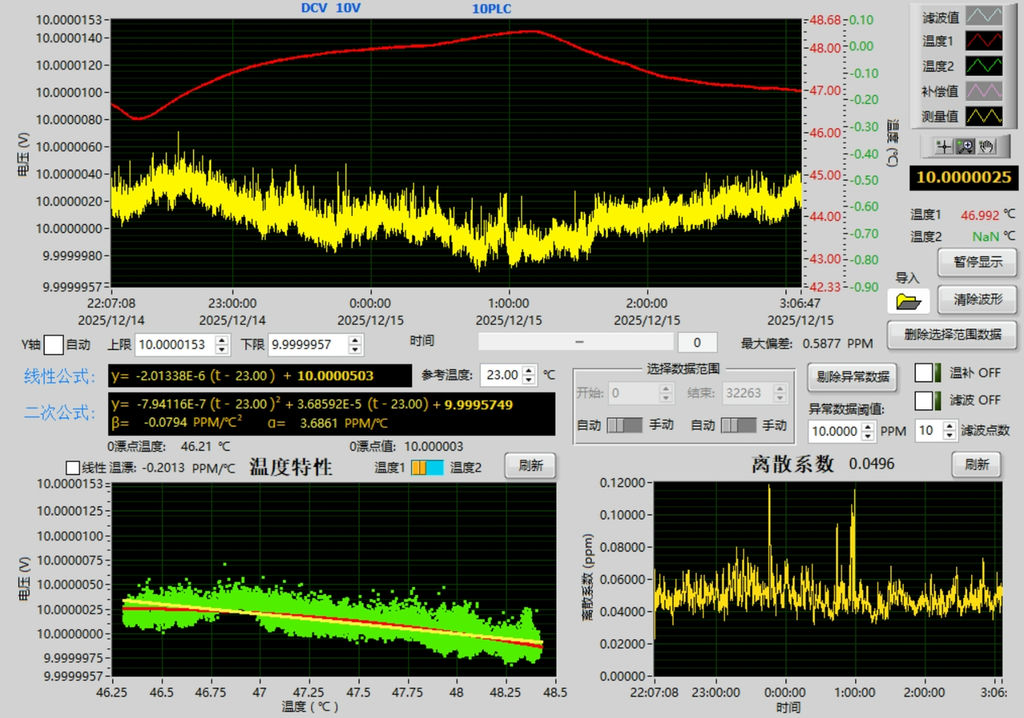

由于这次在机内设计了高精度数字温度传感器,所以就不再使用EmoeTemp读取环境温度了。转而读取的是机内温度(可以看到,基本在48°C左右,室温23°C,还是很热的)

测试下来线性温漂大概在0.2ppm/°C左右。同时这一版的噪声也有了很大进步,10V输出时,基本和基准电压源的原始噪声差不太多了(0.05ppm rms of Fullscale)

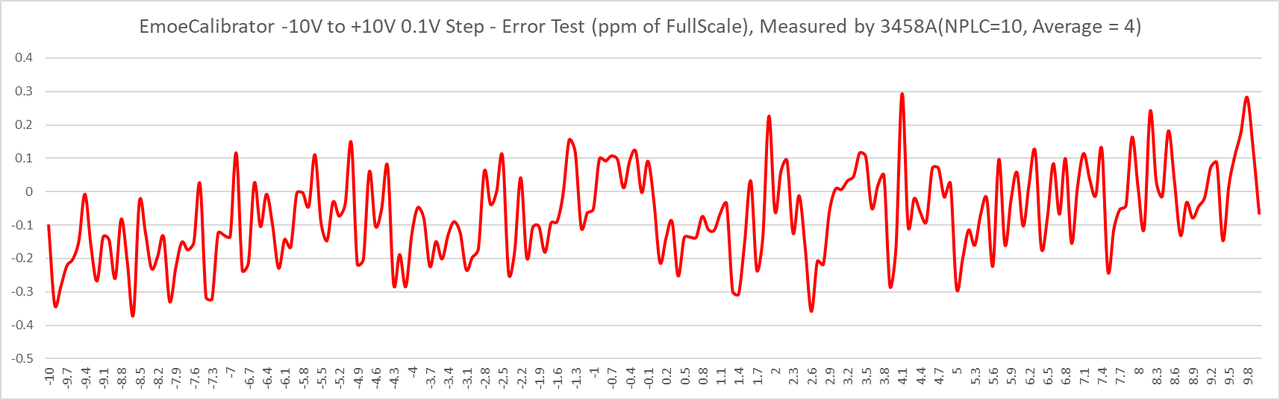

然后就是重头的INL测试了。在测试前我对其进行了系统级的增益和失调误差校准,并进行了INL补偿。3458测试出的结果非常好,这一版的非线性误差几乎在 ±0.5ppm 以内。

当然这只是初测了一下,由于这个指标过于变态,±10V范围内做到了1uV分辨率,想要测试全码值几乎是不可能的。后期我会再减小步进,进行更为细致的INL测试。

Fluke 5730A标称是能为8位半DMM校准,那么我觉得我标个7位半问题不大吧)

5.2-10V、1V与100mV

有人可能会问:既然已经能在10V档位实现1uV的分辨率了,那做1V档甚至更低的有必要吗?

答案是有。关键的原因其实很简单,在于 噪声。

10V档位下,我们的Calibrator输出10V时的噪声约为4uVpp,不到1uVrms(测试条件是3458 NPLC=10),看起来已经足够好了?但是如果在测试一些超低噪声的系统时,可能还是不够用。比如nV表前端,一是需要mV甚至uV级的信号作为激励,二是需要这个激励信号的噪声极低。那么我们如果只有10V档就有点尴尬了。

此时如果用9:1的电阻分压器将10V输入衰减10倍,得到1V的输出,噪声也会被衰减10倍(前提是衰减器的阻值合适,不引入大于或者接近本底的噪声)

衰减一遍后再衰减一遍,噪声将会更小,比如10V输出时4uVpp噪声,衰减100倍,100mV输出,噪声变为40nVpp…吗?

当然,这是很理想的情况。实际情况中,输出级的运放引入的噪声就大于这个量级了。

比如这是OPA2189的手册,其在0.1-10Hz内的噪声就已经有100nVpp了,就算是把他当作单位增益缓冲器使用,40nVpp的噪声叠加上100nVpp,仍然会恶化。所以输出级想做到超低噪声也是一个挑战。

不过我们现在只做了10V档和1V档,在1V档下可以实现100nV的分辨率,噪声也符合预期。由于最近我们的实验室搬迁,仪器设备还未完全准备就绪,所以这部分的噪声指标我们后续补测后再放上来。

5.3-SCPI指令集

和我们之前设计的EmoeDAQ一样,我们在Calibrator上也使用了SCPI指令集系统,让控制指令遵循标准格式,变得更像人设计的东西。

5.4-未来的升级

后续我想增加100mV档和100V档,让其变成一个真正能在实验室中使用的、计量级的可调直流电压基准源。

同时还可以为其增加选件,同时做一个压控的电流基准源。不过电流基准的难度要比电压基准更高,所以这是不知哪年才能做好的项目)

另外,我们也可以尝试做一些降级(比如5位半、6位半的模块级的DAC,学学ADI做的SiP(uModule),做成一个模块化的高精度DAC。

6-后记

其实🐟去年的一年里身体都不太好。年初是感觉隐隐约约的腰疼,后来5月确诊了腰椎间盘突出,较为严重的那种。于是后来的半年时间里只能躺在床上边修养边办公,所以做项目/填坑的意愿和动力都不足。(在这里也给长期久坐的朋友们提个醒,注意腰椎健康)

好在经过一段时间的康复+训练,现在勉强能坐着使用电脑了。还请各位催更的朋友稍安勿躁,我和Emoe的编辑们会慢慢填坑的。

Emoe的服务器在25年底经历了一次迁移,倒是并没有出现太严重的问题。另外我发现Emoe的知名度似乎越来越高…在模拟设计这个小众领域内随便聊聊就能碰到群友,不知道该为我们做出的成果高兴,还是要为模拟的逐渐式微感叹)

总之,新的一年继续前进。

开源链接

Beta版本原理图放在github上,有需要的同学自取:https://github.com/emoestudio/EmoeCalibrator

![仪表博物馆[04]—HP 3312A模拟信号发生器](https://www.emoe.xyz/wp-content/uploads/2023/06/IMG_5451-2-600x400.jpg)

![[Magic Circuits]-中高速模拟信号采集系统](https://www.emoe.xyz/wp-content/uploads/2021/05/2-600x157.png)

![雷达信号处理-[3]-数字下变频(DDC)](https://www.emoe.xyz/wp-content/uploads/2021/11/1-1-600x184.png)

有点吊,开个脑洞如果不用分压电阻LT5400而是用一块DAC啥也不干专门拿来生成一路基准给辅助的16bitDAC当基准,是不是能省下精密匹配电阻的钱?

另

opa189的加法器的非线性也就是INL问题是如何解决的?好奇

得看辅助DAC的基准输入范围有多少,取决于从DAC总体的输出范围,可能得修改电路来适配这种DAC级联的方案,不过最后加法器的精密电阻还是省不掉,意义不大。

加法器的非线性度一般靠opamp自身的极大开环增益来减小,减小不了的只能软件想办法补偿了)

极大开环增益会不会带来更多的问题啊(之前遇到过为了补偿线路电阻,增加开环增益导致放大器震荡的问题),感觉软件补偿像是更好的路子?

这里不是说要人为去增加开环增益,选用开环增益足够高的运放,闭环之后线性度会比较好。设计成熟的运放是考虑过相位裕度和各种补偿的,除开电路设计不当的缘故,很难震荡起来。