信号完整性与电源完整性学习笔记-01

前言

鱼最近在学习《信号完整性与电源完整性分析-第三版》这本书。SI/PI分析在现代电子设计中起到了至关重要的作用。在信号频率逐渐升高时,SI/PI设计分析将是电子设计验证中必不可缺的一环。

你可以在 老吴的博客 下到这本书的电子版,不过似乎只有第二版的,我看的是第三版纸质书。

本文主要记录一些鱼学习的笔记,主要是重点概念与术语。如果你想要简单了解一下SI/PI,可以看看本文当作参考。

本文会长期更新,前提是我不鸽)

什么是SI/PI?

在时钟频率只有10MHz的年代,电路板或封装设计的主要挑战是如何在双层板上布通所有的信号线,以及如何在组装时不破坏封装。由于互连线并未影响系统性能,所以互连线本身的电气特性并不重要,在这时可以说:对信号而言,过去的互连线是畅通透明的。

简单来说,对于一个上升沿为10ns,频率为10MHz的信号,用最粗糙的互连线,电路也可以工作。

但是现在的时钟频率提高了,信号的上升沿也变短了。在多数电子产品中,时钟频率超过100MHz或者上升沿小于1ns时,信号完整性效应 就变得非常重要了。

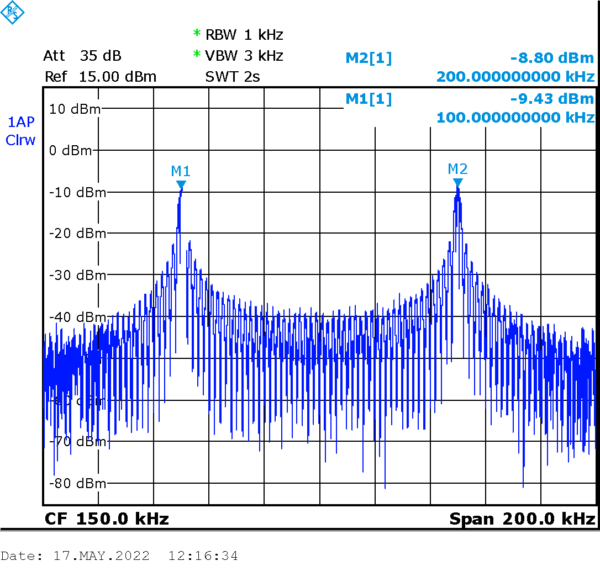

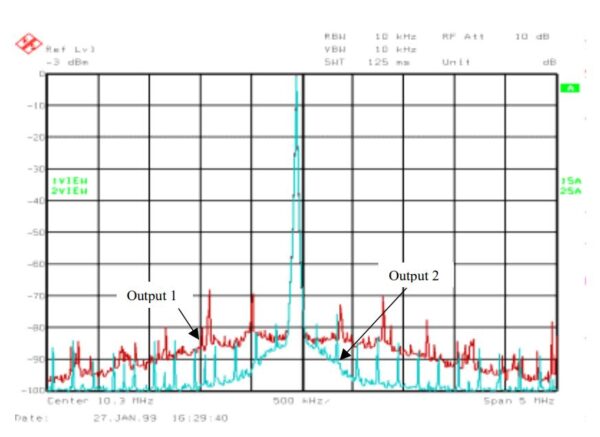

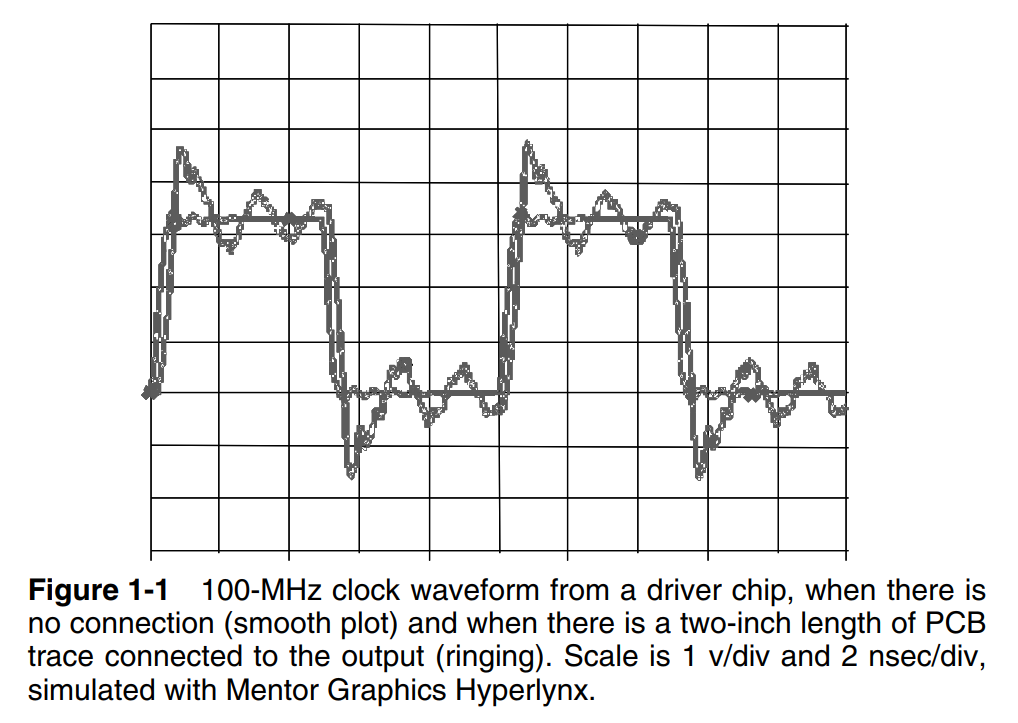

比如上图中,一个由时钟驱动芯片产生的频率为100MHz的时钟信号,如果让输出引脚悬空(不连接任何导线),测得的波形是比较规整的方波。如果在这个引脚上连接一段2inch(约5mm)的导线,输出将产生严重的 振铃(Ringing)

广义上讲,信号完整性指的是在高速产品中由互连线引起的 所有问题 。它主要研究当互连线与数字信号的电压、电流波形相互作用时,其电气特性如何影响产品的性能。

可以将所有问题分成下面三大类,但他们之中也存在着相当大的重叠。

- 信号完整性(Signal Integrity, SI),指信号波形的失真。

- 电源完整性(Power Integrity, PI), 主要指为有源器件供电的互连线及各相关元件上的噪声。

- 电磁兼容(ElectroMagnetic Compatibility, EMC),主要指电路自身产生的电磁辐射和由外部场导入电路的电磁干扰。

根据问题类型又可以分为以下6大类:

- 单一网络的信号 失真

- 互连线中频率相关损耗引起的 上升边退化

- 两个或多个网络之间的 串扰

- 作为串扰特殊形式的 地弹(Ground Bounce) 和 电源弹(Power Bounce)

- 电源和地分配中的 轨道塌陷

- 来自整个系统的 电磁干扰(EMI) 和 辐射(Radiation)

接下来来总结一下各种问题。

1.单一网络的信号完整性

网络(Network) 由系统中所有连接在一起的金属组成,例如从时钟芯片的输出引脚引出的导线与其他3个芯片的引脚相连,连接这4个引脚的每条金属可认为属于同一个网络。另外一点,网络不仅包括信号路径,还包括信号电流的返回路径(return path)

互连线引起单一网络上信号失真的共性问题分为3个方面。第一个就是 反射(reflection)。引起反射的唯一原因就是信号遇到的瞬时阻抗发生了改变,简称 阻抗突变。

信号感受到的瞬时阻抗与信号路径和返回路径的物理特性有很大的关系。任何改变横截面或网络几何结构的特征都会改变信号所感受到的阻抗。引起阻抗变化的所有特征称为突变,突变的情况来自几点:

- 互连线末端

- 线宽变化

- 层间转换

- 返回路径平面上的间隙

- 接插件

- 路由拓扑的改变,比如分支线、T形线或柱线

这些阻抗突变是由横截面、布线拓扑结构或附加元件产生。最常见的突变发生在导线末端处,通常遇到的是接收器的开路高输入阻抗或驱动器的低输出阻抗。

如果反射噪声的源头是瞬时阻抗的变化,那么解决这个问题的方法就是 把互连线的阻抗设计成恒定的。

怎么设计呢?以下4种方法可供参考:

- 使用导线阻抗为常量或所谓的

可控的电路板,这通常意味着使用 均匀传输线 - 为了控制末端反射,采用电阻器的端接匹配策略去控制反射,让信号看不到阻抗有变化。(比如USB2.0连接器的2根数据线,在PCB上靠近连接器端串接2个小电阻,典型值为22欧姆左右)

- 使用沿线拓扑的阻抗维持恒定的布线规则,这就要采用点到点布线,最小化支路长度或短柱线(我没怎么明白短柱线是啥…)

- 设计不均匀的传输线结构以减轻线的不连续性。要对线的几何特征进行精细设计,以修整边缘场(不太明白。)

今天累了orz,等我歇歇再来~

![[Magic Circuits]-中高速模拟信号采集系统](https://www.emoe.xyz/wp-content/uploads/2021/05/2-600x157.png)